innovus学习笔记——数字后端IC

innovus学习笔记——数字后端IC

一、物理后端设计流程简介:

1、Layout版图设计:

由fab提供的PDK库导入各种标准库文件进行设计,版图一般用GDSSII文件表示。

版图设计完成后要做DRC(Design Rule Check)和LVS(layout versus schematic)检查。DRC主要检查版图是否符合设计规则(参考fab提供的design rule文件)。DRC的检查结果不能全信。 LVS通过EDA工具从版图中抽取出晶体管级的SPICE网表与用Dracula和Assura等工具将标准门级的Verilog电路网表转换后的SPICE网表做对比。检查电器连接规则、器件数目和类型、电源线和地线连接等问题。

上述过程没有问题后,进行后续的RC参数提取产生SPF文件,然后进行延迟计算得到SDF文件,并进行后续的静态时序分析STA。

2、物理单元建库(LEF)

2.1 物理建库单元

逻辑单元电路:

标准单元(组合逻辑和时序逻辑电路等)、模块单元(存储单元ROM,RAM、专用模块(COT,SSP)、IP)、I/O单元。

对应的物理单元建库元素:

标准单元(standcell):反相器、与门、寄存器、选择器、加法器等。

模块单元(block):RAM、ROM、COT)。

I/O单元:输入、输出、双向、供电、接地。

组成:PAD接口、信号缓冲电路、静电放电保护电路ESD。

特殊单元等。

2.2 LEF文件

LEF(libary exchange file)——物理库交换文件。

种类:technology LEF和Cell LEF

第一种包含布局布线规则和晶圆厂的工艺信息。

第二种用于定义标准单元、模块单元、I/O单元和各种特殊单元的物理信息。

文件的产生:需要单元库的版图库、时序库、工艺信息通过Virtuoso Layout editor 和Abstract generation 生成。

3 时序单元建库(lib)

3.1 延迟

芯片电路延迟:器件延迟和互连线延迟。(由实际的节点和负载电容预估)

1、器件延迟:根据版图库提取的RC参数,结合晶体管级理论参数模型。通过SPICE仿真,根据不同输入信号的转换时间(transition)和输出端负载建立的数据表。

定义:器件延迟(传播延迟),信号通过一个逻辑门需要的时间,输入信号电压变化的一半到输出信号电压变化的一半。

上升、下降时间:信号10%~90%

2、互连线延迟:逻辑综合时由线负载模型(WLM)预估

3.2 lib文件

1、.lib时序库的文件格式,描述单元库各个单元时序信息的主要库文件。(ILM、TLF、ALF等)它定义了每个单元不同输入情况下各输入端口到输出端口信号的传播延时,工具通过仿真不同工艺角(process corner condition)条件下电路的工作状态得到相应的时序数据,再将数据转换成工具可以识别的库交换文件(.lib)用于芯片的时序分析。

2、时序库的建立需要PTV条件,由fab提供。

3、其描述的单元信息与物理库的单元一一对应。

4 布图(floorplan)和布局(Place)

4.1 布图(floorplan)

主要内容:芯片大小规划、输入输出单元规划、大量硬核(hard core)或模块(block)规划。

目标:

- 确定芯片面积。

2)确保时序收敛。

展平式设计的延迟预估:通过WLM估算负载电容(通过线负载根据门的扇出(FO)估算互连线长度,进而估算线延迟。

层次化设计:芯片顶层设计、子模块分割、顶层组装。

时序预估:整个芯片的延迟预估和子模块约束产生。需要进行时序预算,对时钟树上的延迟进行预估和分配。

3)保证芯片的稳定。

电源规划 - 满足布线要求。尽量减小互连线长度减少延迟。

4.2 电源规划

电源网络设置、数字模拟混合供电、单电源和多电源供电电源网络设置。

4.3 布局(Place)

I/O单元布放和模块布放在布图阶段完成。主要标准单元的布局。

1、展平式布局:模块和标准单元的细致摆放和优化。

2、层次化布局:先分配子模块,子模块按展平式摆放,顶层组装。

目标预估:

1)拥塞预估。布线通道不能超过现有的5%。

2)时序预估。仅建立时间(set up )预估,保持时间(hold time )预估在时钟树综合之后。

3)供电预估。引用VCD文件对芯片功耗、电压降、EM预估。

5 时钟树综合

5.1 时钟信号的产生

RC时钟,晶体振荡时钟[用于VLSI],锁相环倍频时钟(PLL)【一般用于SOC,可以实现不同频率输出】,锁延迟电路(DLL)【一般用于FPGA,良好的工艺变化不相关性,减小时钟抖动,在很宽的频带范围可以获得高性能的正交信号】。

5.2 时钟信号的特征参数

1、周期/频率:

create_clock和create_generated_clock定义

2、时钟延迟\滞(latency): 又称插入延迟(insertion delay)包含两部分,即时钟源(clock source)和时钟网络(clock network)插入延迟。前者从源到根,后者从根到树。

3、时钟信号不确定性(抖动): 确定抖动(DJ)和不确定抖动(RJ)组成。不可避免且与工艺相关,取决于时钟发生器结构。

4、时钟信号的偏差(skew): 同一时钟到达时钟域内的不同寄存器之间的时间偏差。衡量时钟树性能的重要参数,时钟树综合目的是减小偏差。由于走线长度不同引起,产生最小/最大插入延迟,两者之差为最大偏差。

5、 Tips: 减小偏差,插入buffer,功耗增加

5.3 时钟树综合方法

1、时钟分类: 真实和虚拟时钟。

真实:理想时钟(时钟树综合前)和传播时钟(时钟树综合后)

虚拟:非本模块的时钟,存在于整个设计系统,在当前设计中不存在。

2、时钟树结构:

时钟树起点为根节点,经过一系列分布节点到达寄存器输入端或其他时钟终点被称为叶节点。

H树、X树、平衡树、梳状或脊椎状时钟网

3、标准设计约束文件(SDC)——时序约束文件

主要三部分组成:时钟定义、输入延迟、输出延迟

顶层设计中还包含输入端口的驱动以及输出端口的负载

4、时钟树约束文件:可以由标准设计约束文件自动产生。其中定义了每一个要综合时钟树的名称、周期、时钟根节点。最大插入延迟、最小插入延迟、最大偏差(skew)、最大transition/slew。同时定义专供时钟树综合选用的buffer或inverter。

时钟树综合:根据上述文件中每个时钟定义的参数,时钟树综合工具从standra cell 开始计算到每个叶节点的延迟,根据最大偏差约束,插入buffer或者inverter,使延迟差满足要求。同时还会调用place工具对其正确摆放。预估一个互连线总延迟。

6 静态时序分析

主要包括RC参数提取和时序分析。

时序分析: 将某一段路径的时序与时序约束的要求进行比较。对寄存器,每一段待分析的时序路径由它的起点到终点表示。包括建立时间(setup) 和 保持时间(hold) 检查。

setup: 在时钟作用前沿(或后沿)到达前,同步输入信号必须保持稳定的那段时间以使信号不至于丢失。

hold: 在时钟作用前沿(或后沿)到达后,同步信号必须保持稳定的那段时间以使信号不至于丢失。

二、Innovus RAK学习

版权声明:下述部分内容为CSDN博主「kevindas」的原创文章,遵循CC 4.0 BY-SA版权协议。

原文链接:https://blog.csdn.net/kevindas/article/details/118462203

基本指令

1、innovus.cmd / innovus.log / innovus.logv的区别?

innovus.cmd:记录innovus执行的命令,来帮助后续创建脚本;

innovus.log:记录innovus执行的命令和log,命令会以

< CMD >的前缀标识;

innovus.logv:相对于innovus.log,记录了更多的信息,v即verbose的意思。

2、按Q编辑属性

2、使用空格键可以在多个重叠的目标之间快速切换。

3、使用Auto Query功能(左下角的Q是开关)查询目标信息时,多个目标重叠,使用N和P来往后或往前切换目标。

4、当目标选中后,使用 F8(可能需要两次F8)来将对象的属性打印在终端上。

5、使用help set*Mode查询相关命令;使用help setNanoRouteMode来查询具体命令的使用。或者使用man来查找帮助。

6、当Net被选中时,logic terminal上会以‘X’来标志input,'O’来标志output。

7、Find/Select Oject 查找某个物体

8、Design Brower 浏览整个设计

包含文件类型

.fp 保存布图信息。

.globals 包含各种库,网表,MMMC文件和其他设计信息的指针。

.mode 保存类型文件。(setPlaceMode,setOptMode,setNanoRouteMode)等。

.place 文件保存标准单元布局。

.route 保存布线信息。

.pref.tcl 保存用户的具体设计信息和展示偏好。

veiwDefinition.tcl 包含MMMC的设置文件。

mmc/ 包含各种约束模式。

Import Design

Place_opt_design

1、菜单栏 File-Load-FloorPlan 和以下命令等价:

source DATA/leon.globals

init_design#(不加参数时读入由veiwDefinition.tcl定义的view)

2、File—Load—Floorplan 选择 DATA/leon.power.fp 文件,或者使用命令:

loadFPlan DATA/leon.power.fp

4、在进行PR前需要先指定工艺,innovus会根据工艺设置capacitance filters 和extraction effort level。

setDesignMode -process 45

5、设置时序分析模式

Tools-Set Mode-Specify Analisis Mode

Single: 静态时序分析工具只会在指定的一种工作条件下检查建立时间和保持时间。 因此只吃一种库。

Best and worst case: 对于最好-最坏分析模式(BC-WC Mode),静态时序分析工具会同时在PVT环境中最好的和最坏工作环境下检查建立时间和保持时间。 吃2种库:max库和min库,分析setup时用max库,分析hold时用min库。

On-Chip Varation:

(1)OCV:是指在同一个芯片上, 由于制造工艺等原因造成的偏差。如电压降造成局部供电的差异,晶体管阈值电压的差异,晶体管沟道长度的差异,局部热点形成的温度系数的差异,互连线不同引起的电阻电容差异。

(2)分析准则:“快的更快,慢的更慢”。在检查建立时间时,使用max库计算数据路径延时(包括发射时钟的延时、建立时间),使用min库计算捕获时钟延时;在检查保持时间时,使用min库计算数据路径延时(包括发射时钟延时),使用max库计算捕获时钟的延时(包括保持时间)。

(3)OCV分析模式过于悲观,因为在同一个芯片内,不同地方器件参数的变化不会同时跨度最好边界条件(使用最好时序库)和最坏边界条件(使用最坏时序库)。为了对芯片内部参数差异更好的建模,使用时序减免(Timing derate)来达成:一次读入一个边界条件,再使用时序减免来建模同一个芯片内的差异。

set_timing_derate -early 0.9

set_timing_derate -late 1.1

通过以上减免值的设置,STA工具在计算时序延时中,最

快路径会基于单一时序库计算结果再减少10%的延时值,最慢路径会基于单一时序库的计算结果再增加10%的延时值。在实际工程设计中,不同的生产工艺的timing derate 的设定是通过实际工程经验总结得到的。

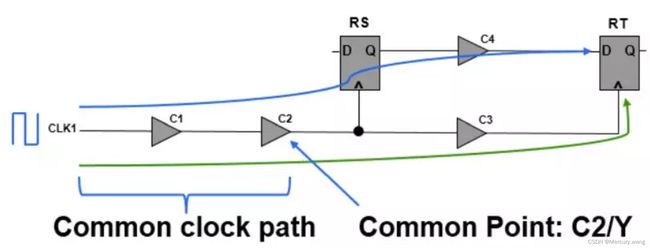

CRPR/CPPR:

S公司:CRPR:clock reconvergence pessimism removal, 时钟重汇聚悲观移除

C公司:CPPR:clock path pessimism removal,时钟路径悲观移除

即剔除公共clock path上的悲观度。

拿setup 分析为例,通常会设一个late 的derate 值(大于1的值)到launch clock path 上,同时会设一个early 的derate 值(小于1的值)到capture clock path 上,这就使得common clock path 在被当做launch clock path 和capture clock path 时的delay 有了差别,但是对于同一段path 在一个固定时间内,它的delay 值一定是固定的,不可能忽大忽小,所以在STA 分析时,需要把由于derate 引起的common path 上delay 的差值剔除掉,这就是所谓的CRPR/CPPR。

https://www.cnblogs.com/wt-seu/p/12582343.html

使用命令:

setAnalysisMode -analysisType onChipVariation

-cppr both

6、使用下面命令可以效率更高跑完timing:

setDontUse *XL true

setDontUse *X1 true

7、placment 和Pre-CTS

place_opt_design命令同时完成了placement和pre-CTS优化,功能上相当于下面两个命令:

placeDesign

optDesign -preCTS

但是place_opt_design提供了更好的runtime和PPA(性能,功率,面积)。

在进行上述命令前可以更改或者查看当前place和opt的模式:

s/getPlaceMode

s/getOptMode

8、执行place_opt_design命令前,可以通过Unified Metrics(Stylus) 提取相关过程的报告。

9、check_design命令是后续flow的必备条件,可以使用-type命令明确要检查的flow种类。当check_design存在error时,后续flow将终止运行。检查会在placement之前进行。

Running Early Global Route

Early Global Route 是全局布线和布线轨道排列的组合。跑两次。第一次通过限制金属布线层数从9到3检查布线拥塞;第二次使用全部九层金属完成原型设计。

1、Route-Early Global Route

2、Change-Route Layer:max:to Metal3(3)

3、关掉Net,打开Overlayer可以看到前期全局布线的拥塞部分为红色菱形框的部分。里面内容显示了拥塞具体情况。

H/V:#-top/#-bottom

H:水平方向的拥塞 V:竖直方向的拥塞

#-top:该区域需要的布线轨道数目。

#-bottom:可使用的布线轨道数目

Congestion Map:

eGR-3D:V/H:number 拥塞数目

通过innovus.log也能看到拥塞信息。或者使用命令:

reportCongestion -hotspot # 打印拥塞信息

Extracting RC Data

芯片延迟主要包含器件延迟和互连线延迟。器件延迟在时序库中已经预先精确算出。主要提取互连线的RC参数进行延迟的准确计算。

主要在在Pre-Route (估算)和Post——Route(实际提取)两个阶段进行。

RC提取模式可以预先设置。

相应命令:

extractRC

rcOut -spef leon.spef -rc_corner rc_worst

Running Timing Analysis

1、Timing-Report Timing

2、生成时间报告:

leon_preCTS.cap :max capacitance violations

leon_preCTS.fanout: max fanout violantions

leon_preCTS.slk: slack report for each endpoint

leon_preCTS.summary: timing summary

leon_preCTS.tran: max transition violations

leon_preCTS_all.tarpt: timing report for all path groups

leon_preCTS_in2out.tarpt: report for input to output paths

leon_preCTS_clkgate.tarpt: report for clock gating paths

leon_preCTS_in2reg.tarpt: report for input to register paths.

leon_preCTS_reg2out.tarpt: report for register to output paths.

leon_preCTS_reg2reg.tarpt: report for register to register paths.

或者使用下述命令:

report_timing #使用默认最差路径

pop_snapshot_stack#截取报告

creat_snapshot -name pre_CTS#导入到pre_CTS文件

3、 Time -Debug Timing

打开Timing Browser 进行debug

双击Path List 中的path 可以打开路径分析界面。

Running Clock Tree Synthesis (CTS)

1、定义 non-default rule(NDR) 【比默认rule两倍宽和间距的rule】来给时钟走线

create_route_type

-name clkroute -non_default_rule 2w2s

-bottom_preferred_layer Metal5

-top_preferred_layer Metal6

set_ccopt_property route_type clkroute

-net_type trunk

set_ccopt_property route_type clkroute

-net_type leaf

2、定义buffer,反向器和时钟门单元来使用:

creat_ccopt_clock_tree_spec -file ccopt.spec

source

3、通过CCOpt给出CCOpt 描述文件

4、跑CCOpt -CTS 建立时钟树

Running Post_CTS Timing Optimization

时钟树已经综合完成,可以分析基于真实时钟树的延时和偏差。

1、timeDesign -postCTS

2、optDesign -postCTS

3、timeDesign -postCTS -hold

4、optDesign -postCTS -hold (存在大量保持时间违例时执行,否则在post_route 修复)

Running CCOpt Clock Tree Debugger(CTD)

CTD用来分析和debug时钟树的结果。

Running Nano Route

全局布线和详细布线。目的阻止信号的串扰(信号完整性分析),使时钟收敛。

Post -Route Timing and SI Optimization

布线完成,分析真实时序路径。

利用QRC工具提取RC参数,然后进行时序分析

Verifying the Design

1、Verify Geometry: 验证物理设计规则,用于20 nm及以上的设计。20 nm以下的设计使用 Verify DRC

2、根据验证报告打开 Tools-Violation Browser debug

Save Design

Save GDS

Save testcase:保存成压缩文件,可以restore:

innovus -init testcase.tcl

————————————————