从零开始的小白pr学习之旅--day2 数字后端流程(一)

个人认为,在开始后端工作的时候,抛开别的,首先要思考的就是我有什么,我要做什么,我要怎么做,我要做到什么程度。有了这个思路,下面将描述下我对数字后端工作每个阶段的简单理解。

1.Data Prepare

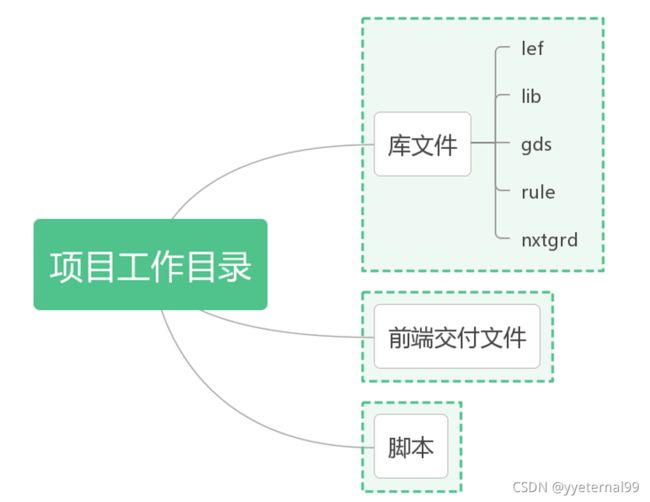

这一阶主要是对手头所拥有的文件,资料做一个整理。个人觉得这是后端工作重中之重的一个环节。大概要整理的内容如下图

首先是库文件,项目所用到的某一厂家的某一制成,会有相应一套完整的库文件。需要在其中选择项目要用到的,并把它们按照固定的分类规整的放置好。比如要用到的lef,包括tlef,stdcell的lef,mem的lef,ip的lef。根据要跑的corner,选择合适的lib,ss的lib,ff的lib等等。stdcell的gds以及其它ip的gds,日后要做的drc lvs的rule等等等等。

其次是前端交付的数据,例如网表,sdc。我个人觉得需要将每一版前端交付的数据按照日期放好,既是做个备份,同时也是留个心眼。当第二版数据来的时候也好有个对比。就比如前端告诉我新版本的网表优化了,面积小了。这时候我只需要打开网表看一眼行数,和之前的版本的网表行数做个对比。如果网表行数上新版都比旧版多很多,那我直接就可以反馈给前端网表可能有误,都不需要读入工具跑一下了。

最后就是积累的各种辅助性的脚本,参考文件之类的。

上述过程就是对“我有什么”做一个整理。正所谓磨刀不误砍柴工,当把手头的数据规规整整的放置好之后,日后需要什么就在专门的地方去取,会省特别多特别多的时间。可能大公司在这方面做得很完善,根本不需要我们去考虑,但是我还是觉得我这种小白应该“未雨绸缪”一下,万一哪天这些没准备好,我起码有个思路。我去整理的时候可能一次整理的不全面,日后还要返工临时去找一些文件,但经历这样一个过程,经验不就积累下来了么。

2.Initial Design

Initial design就是把输入文件读入到工具当中。最核心的两个输入件就是网表和物理库lef。只要有这两个输入件,那么就可以开启工具进行fp了。lib库和sdc即是时序方面的输入件,有了它们,时序分析相当于有了依据。基本上这几项内容齐全了,就可以继续后续的所有流程了。

我有什么?我有这些输入件,我要做什么?我要将这些输入件读入工具。我要怎么做?上一阶段已经把这些数据准备好了,我只需要把具体路径给工具就好了。我要做到什么程度?我需要保证输入件完完整整的读入工具,这时候就要去看log文件了。看看工具报了什么error,什么warning,是不是跟输入文件相关的,是不是报了某些文件缺失的,通过读log的方式可以保证输入件的齐全完整。

所以你看!当data prepare做的很完善的时候,这一步是不是简单的不能再简单了。网表,sdc,lib,lef都已经分门别类的规整好了,只需要写个路径就OK了。

3.Preplace

Preplace这一阶段我个人理解是后端工作最难做的两个环节之一。另一个是cts。

Preplace要做的第一件重要的事就是规划整个设计的布局,也就是floorplan。fp主要是合理规划mem,ip这些macro的位置。fp的好坏影响着后续环节的进行。好的fp会使得后续环节的走线清晰,逻辑分布均匀,时序通畅。糟糕的fp会让每一步寸步难行。

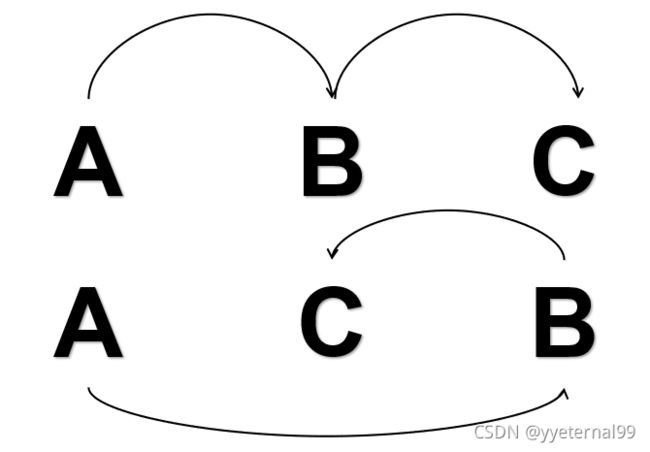

那么如何做出一个好的fp呢。以我目前的认知来看fp的一个重要依据是数据流。数据流怎么理解呢,其实就是数据从哪里来,到哪里去的一个过程。真正的项目数据不会是简单的从A到B的,而我们后端工程师也不太需要专门去搞清楚整个项目的原理,怎么搞明白数据流这就要和前端交流了。比较难搞的是,有的时候可能没有人给你理清数据流,这时候需要参考一些说明书之类的自己去搞清楚。为什么一定要按数据流摆fp呢?其实就是减少数据来回打折的现象。让路径尽可能短。数据本身由A到B再到C,fp按照moduleA moduleB moduleC的顺序摆,数据是一路通畅的。但是如果按moduleA moduleC moduleB的顺序摆,那么数据从A到B天然就会多走一段路,既造成了绕线资源上的浪费,也造成了时序问题。

有了数据流就能将整个设计细化。我的一个思路是,先固定那些和端口有交互的module,这些和端口交互的module往往都是数据输入或者输出的地方。把这些moudule的macro放置在相应的端口附近,其实就相当于确定了头和尾。当这些module的位置确定后,再去摆放和这些module有交互的其它module。如果有某个module和其它多个module都有交互,那么肯定倾向于将该module摆在一个到其它module距离均衡的地方去。这样一步一步的每个module都会有个大致的位置了,fp基本也就完成了。

好的fp不是一步到位的,需要根据后续place的结果,来判断fp的合理性。根据place结果可以发现fp中的不足,再返回到fp,调整module的相对位置。来来回回多次,最终会得到一版完善的fp。fp是个经验性的工作,如果有无限的时间,甚至可以不需要数据流,单纯的一版一版对比place结果就可以选出最好的fp。innovus工具也可以在图形界面,通过看各module间的走线数量确定各模块的位置。但是往往项目时间都很紧,因此需要数据流作为fp的指引,减少迭代的次数。

我有什么?我有数据流,我迭代的不同版本的数据,innovus工具的飞线信息。我要做什么?我要摆出一版走线短,拥塞低,时序好的fp。我要怎么做?我需要根据数据流确定大致的fp,根据每版结果细调fp,这样一版一版的迭代以达到一个时序,拥塞都相对较好的fp。

以上只是笼统的说了下fp的过程,具体的细节以后的帖子中会详细的总结的。

Preplace要做的第二件重要的事就是电源的规划。电源可太重要了,这方面要学习的内容也特别多,这方面的知识我也很是欠缺。我就以我目前所接触到的大致说说电源规划的流程。我会把一个项目的电源分为三个部分,stdcell电源,core区域电源,以及mem,ip的电源。

首先要明白一点,一个项目的绕线资源用于两个部分,电源的绕线资源,和数据信号的绕线资源。如果电源占用太多绕线资源,那么数据信号将无充足的绕线资源,就会有大量的short问题。如果数据信号占用太多的绕线资源,那么电源可能会不够充足,这将影响到芯片的整体性能。所以电源和数据信号的绕线资源要合理分配。假如说项目总共可使用12层metal,那么一般来说最高层的metal12,metal11,metal10,将会被完完全全用于电源,因为高层金属厚度大电阻小,最适合做电源。最底层的metal1会被用于stdcell电源。stdcell的pin也是metal1,而stdcell pin是通过metal2连接出去的,stdcell又是遍布在整个芯片中的。这样看来用于数据信号绕线资源的只有metal2的一部分以及metal3到metal9。电源都是通过最顶层一层一层传到最底层的,为了保证电源的可靠性,metal3到metal9的一部分也会被用于做power,所以实际上绕线资源会更少。所以规划电源既要保证电源的充足,也要给数据信号留裕量。一般都是开始的时候电源会打的相对密,到后面阶段如果绕线资源足够,那么自然很好,如果绕线资源不够,可以适当删除一些电源线,让给数据信号。

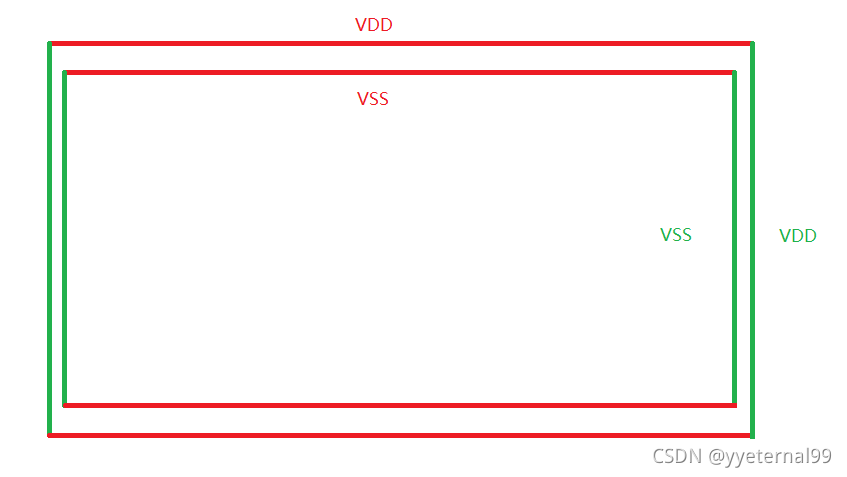

其次,电源如何去打呢。stdcell的电源不必多说。core区域电源最常见的结构就是ring+stripe。ring如下图,就是连成一个环的电源。一般芯片的电源IO会分布在芯片的每条边上。通过ring环将电由外部输入到芯片内。ring环起到了均衡各点输入,避免某些区域输入点密集某些输入点稀疏造成的IR DROP。ring环一般是由最高层金属构成,我这里用红色和绿色代表最高的两层金属。当然ring环也可以由多层金属构成,这样更强劲。具体的画法日后我也会详细总结。(最近没法在家里打开工作用的服务器,只能用画图来画个简图)

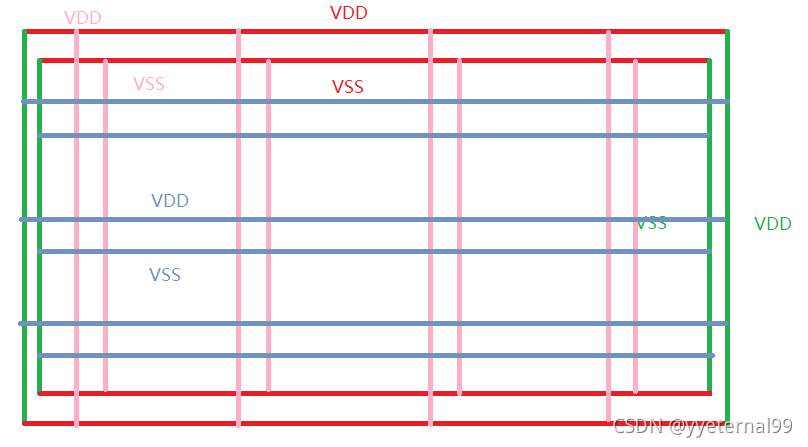

stripe如下图,就是一根根电源线,画出来就和条纹一般,接在ring环上,然后遍布整个core区域。我这里特意用不同颜色代表不同层的金属,每层都如此一层一层由高层到底层。形成了密布的电源网络。所以电源网络就是由不同层金属线一层层交织而成的网络结构。

mem和ip的电源其实和core区域电源打法相似。只不过由于mem一直处于存储读写的状态,对电源需求高,所以mem上的电源一般会画的特别密。 mem上的电源层次会根据mem的pin的金属层决定,一般会使用比pin层次高一些的金属。mem的摆放一般都会采用堆叠的形式,所以电源还要考虑mem pin的连线问题,得保证电源线不会阻碍mem pin的连接。一些ip会对电源有特殊要求,比如需要在ip周围也做一个类似ring环的结构。这在ip的使用手册上都有描述,根据手册上的要求指导照着打就好了。

Preplace的要做的第三件重要的事(其实是杂七杂八好几件事)插入物理cell,包括welltap,boundrycell,gfiller,decap等等。添加blockage,某些区域不能摆放cell要加hard blockage;mem沟道不希望摆除了buffer,inv外的cell需要加soft blockage;根据上一版place结果得知某个区域cell density太高,需要在preplace阶段在这个区域加partial blockgage。某些区域需要预留一部分走线资源添加route blockage。检查fp的摆放是否合理有无摆出core外的macro,有无重叠的macro,等等。检查输入件是否齐全,检查有无drc,有无power的short。

以上内容做完Preplace就算完成了,所以Preplace人工介入的地方特别多,需要注意的细节也特别多,这是需要一次又一次的尝试去积累经验的。

不知不觉已经码了4000多字了,这次的总结就先到这了,下次再简单说说后续的环节。