基于 FPGA+DSP 的冲击波超压测试系统设计与实现-系统测试(二)

5 系统功能测试及仿真

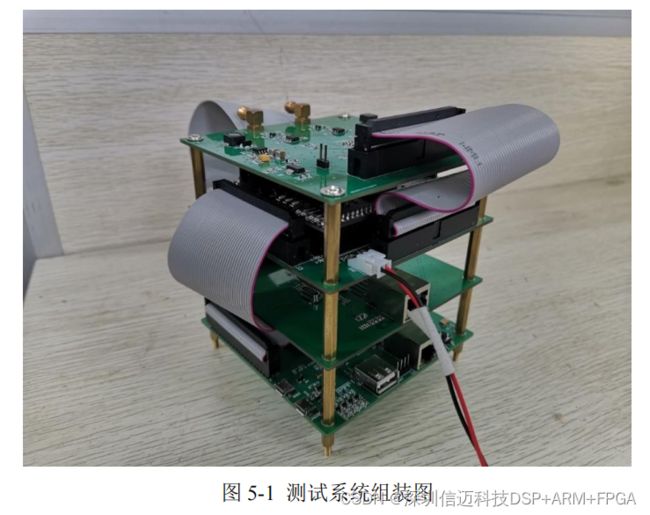

在完成系统硬件电路板的设计和软件程序的开发后,本章分别对 A/D 采集模块、

DDR3 SDRAM 存储模块的读写波形进行了测试,并对千兆网卡传输模块通过 Wireshark

软件进行抓包测速,调试成功并确认无误后将各模块组装起来对系统进行整体测试,试

验系统功能能否达到要求。数据采集系统组装图如图 5-1 所示,从上往下依次为 AD9238

模数转换模块、 FPGA 模块、千兆网卡模块和 DSP 模块,后期可根据试验要求进行模块

扩展。

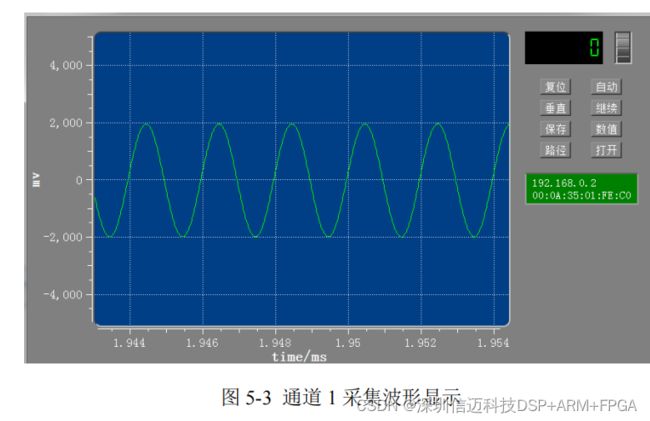

验证 A/D 模块的直流性能之后,将安捷伦信号发生器的输出接口同 A/D 模块通道 1

的 SMA 接口连接,发送峰峰值为 4V (

-2V~+2V ),频率为 500KHz 的正弦波信号, FPGA

控制 AD9238 以 65M/s 的速度对信号进行采集,信号发生器端被测信号的设置如图 5-2

所示。

如图 5-3 所示为信号发生器发送频率为 500KHz 的正弦波时 A/D 模块通道 1 所得的

采集结果。

5.4 系统整体测试

冲击波超压测试系统设计完成后,为综合评估其整体性能,进行了总体测试。由于

冲击波测试环境复杂,本文选择在静态环境下进行冲击波信号的测量来验证系统可行性,

通过使用信号发生器产生某型弹的静爆冲击波波形(通过试验获得),然后使用所设计

的系统进行信号采集,通过此种方法测试,便于重复性试验验证系统的可靠性,且经济

成本低。

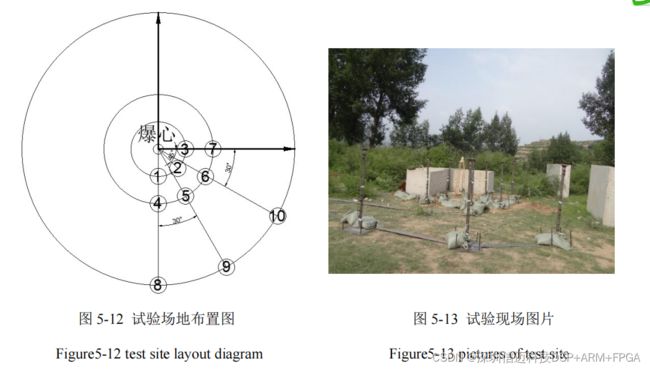

为获得某型弹爆炸时的冲击波波形,进行了现场测试实验,并采用瞬态信号采集仪

采集到了准确的信号波形,现对该试验做如下简单阐述。如图 5-12 所示为试验场地设备

布置图,试验共有 10 个测点,将弹药放置在中心支架上,以弹药的投影为爆心,从夹

角 30 °、 45 °、 60 °和 90 °四个径向方向布设测点,测试半径分别为 1m 、 2m 和 5m,

将所选用的 120B15 、 102B16 系列传感器通过夹具固定在支架顶端呈扇形分布,如图 5-

13 所示为试验现场图。

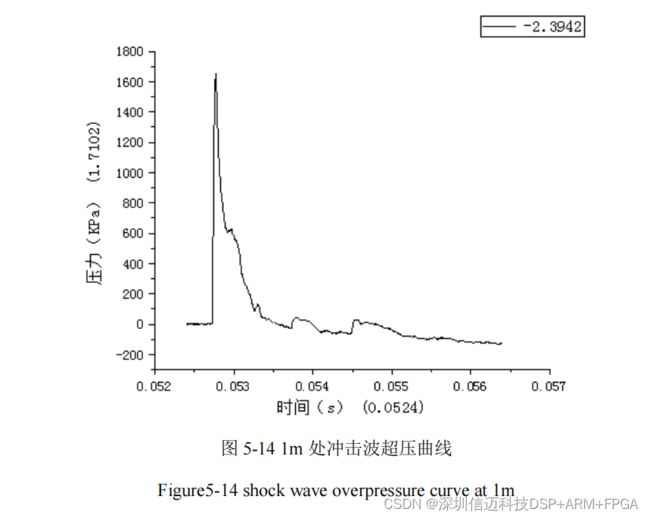

从图中可以看出,测得的数据曲线毛刺较少,该曲线上升沿陡峭,超压峰值高(约

为 1.65MPa ),正压作用时间短,负压低,压力衰减过程呈指数衰减,具有明显的冲击波

信号特点,验证了所选择传感器的性能,通过使用该型号传感器能够得到正确的测试结

果。

( 1 )试验准备阶段:

为检验测试系统的工作稳定性和可靠性,将所采集的冲击波数据导出至上位机,将

各采样点数据转换为电压值输入至信号发生器,使信号发生器产生冲击波信号,方便对

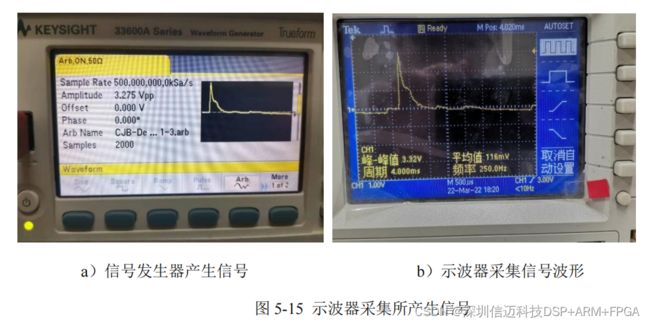

系统进行重复性试验。如图 5-15 所示为信号发生器端产生的冲击波信号,由图可知,信

号振幅为 3.275V ,示波器采集的冲击波曲线同信号发生器输出的波形一致,信号发生器

输出正常。

(2)试验过程:

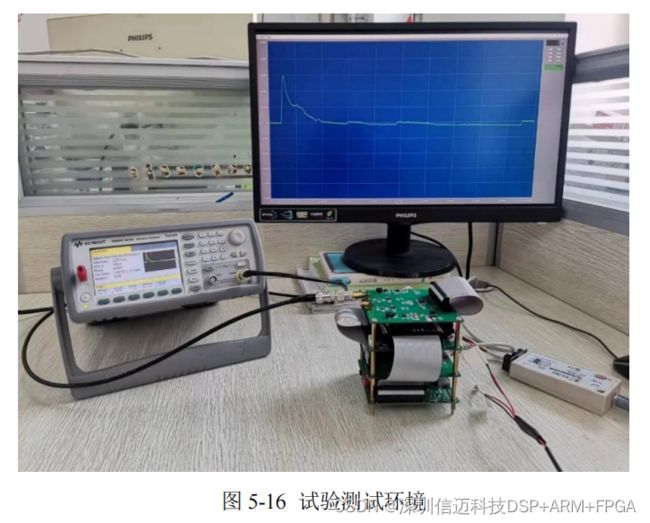

在保证各模块可以正常工作的基础上,将数据采集系统拼装,进行系统功能的测试,

对系统检查无误后将其上电,通过仿真器将程序烧录至系统,信号发生器的输出通道与

A/D 模块的一个通道连接,同时通过千兆网卡连接至上位机, FPGA 控制 A/D 模块以

65M/S 的速度对信号进行采集,打开上位机端的示波软件观察波形,采集环境如图 5-16

所示。

如图 5-17 所示为采集到的冲击波曲线,由图可知采集到的信号无毛刺,波形清晰明

朗,同信号发生器端的信号波形一致。

参考链接:

omapl138 fpga三核高速数据采集处理核心平台方案_深圳信迈科技DSP+ARM+FPGA的博客-CSDN博客