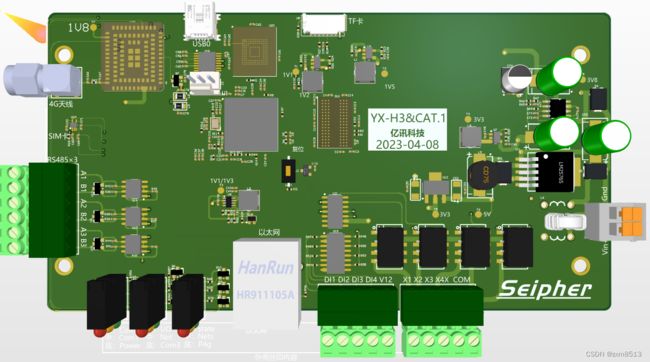

AD六层板布线经验累积

目录

1、布局:

2、创建电源类PWR

3、高速部分可以加屏蔽罩,

4、EMMC和NANDFLASH采取兼容放置(创建联合)

5、HDMI设计

6、就近原则摆放

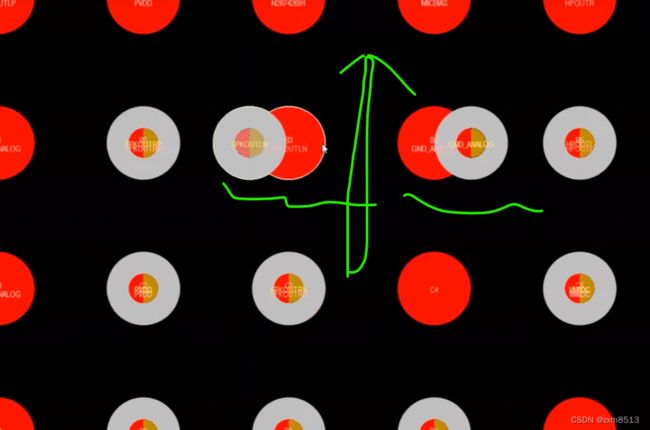

7、AV端口

8、模拟信号(1字型或L型走线)

9、WIFI模块

10、局部模块化布局

11、整板的电源

12、叠层设定

13、其它规则

14、网络分类

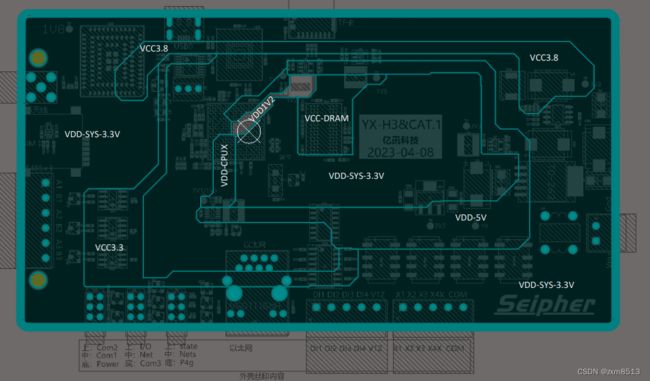

15、布设电源分割层的分区

16、制作供电平层的说明文件(visio),便于布线使用

17、埋盲孔的作用

18、布线过程中出现的问题汇总

1:pcb导入

2:drc设置

3:丝印调整(器件位号改小,放到器件的中心)

4:快捷键设置(如果设置了无效,可能是被占用了,顶部鼠标右键设置)

5:板框的设置(一般在机械层),板框定义

6:布局布线的禁布区设置(板框的内缩外扩)

7:器件的摆放和布局(过孔辅助定位)原点的设置

1、布局:

交互式布局设置,进入交互式布局;

模块化布局思路:顺时针或者是逆时针方向布局

2、创建电源类PWR

选中飞线:Alt+鼠标左键向左上方滑动框选,添加电源类(不同电压等级)

DDR高频,不能受到干扰 (布局留有足够的等长空间)

射频不能也不能受到干扰

3、高速部分可以加屏蔽罩,

屏蔽模块之间的干扰(WIFI,电源,DDR),最好是矩形的罩子(一般1mm),避免接触到过孔

常用存储器DDR(超出5-6mm)

DDR:无排阻的时候,600到800mil(推荐800)电容电阻一般总体布局完成才摆放

4、EMMC和NANDFLASH采取兼容放置(创建联合)

小电容(容值大小)一般靠近IC管脚(电容接近管脚,电阻次之)

如果原理图上器件有特殊要求的要注意摆放位置

5、HDMI设计

要首先考虑静电问题,信号一进入就要消除静电干扰,器件放在背面时要插口距离至少3mm

RJ45和变压器要尽量靠近

6、就近原则摆放

usb:优先考虑静电器件,电源先经过静电器件再通过电容滤波

电容滤波遵循先大后小

7、AV端口

插件考虑静电处理

8、模拟信号(1字型或L型走线)

不控制阻抗,走线包地处理

9、WIFI模块

最重要的是天线,在角落或者边缘,(内置天线板载,外置天线:放在屏蔽罩外面),一字型或者L型布局,走线短

10、局部模块化布局

优先时钟走线(尽量靠近,pai型走线),就近原则摆放

布电源的时候,先找主干道,输入输出,转换的流向

11、整板的电源

局部模块化布局,注意静电器件,同类型的电源并排放置,根据飞线调整位置,放置的时候先大后小,找到输入输出主干道(主控)

电感之间要垂直摆放

晶体一般都是pai型布局

布局总结:先固定的器件摆放,再主控和DDR

12、叠层设定

先选定层数,再确定层叠结构(顺序)

四层结构:signal、gnd(plane)、power(plane)、signal

六层板结构:signal、gnd(plane)、sig2、sig3、power(plane)、signal

依据层叠原则(注意各种方案的适用范围,有什么缺点?),相邻信号层之间不能相互平行,尽量错开

六层板可以采用以下结构:

1)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),Siganl_3(Inner_3),POWER(Inner_4),Siganl_4(Bottom)。

方案1 采用了4 层信号层和2 层内部电源/接地层,具有较多的信号层,有利于元器件之间的布线工作,但是该方案的缺陷也较为明显,表现为以下两方面:① 电源层和地线层分隔较远,没有充分耦合。

② 信号层Siganl_2(Inner_2)和Siganl_3(Inner_3)直接相邻,信号隔离性不好,容易发生串扰。

(2)Siganl_1(Top),Siganl_2(Inner_1),POWER(Inner_2),GND(Inner_3),Siganl_3(Inner_4),Siganl_4(Bottom)。

方案2 相对于方案1,电源层和地线层有了充分的耦合,比方案1 有一定的优势,但是Siganl_1(Top)和Siganl_2(Inner_1)以及Siganl_3(Inner_4)和Siganl_4(Bottom)信号层直接相邻,信号隔离不好,容易发生串扰的问题并没有得到解决(可以通过布线交叉进行优化)。

(3)Siganl_1(Top),GND(Inner_1),Siganl_2(Inner_2),POWER(Inner_3),GND(Inner_4),Siganl_3(Bottom)。

方案3 减少了一个信号层,多了一个内电层,虽然可供布线的层面减少了,但是该方案解决了方案1 和方案2 共有的缺陷。① 电源层和地线层紧密耦合。② 每个信号层都与内电层直接相邻,与其他信号层均有有效的隔离,不易发生串扰。③ Siganl_2(Inner_2)和两个内电层GND(Inner_1)和POWER(Inner_3)相邻,可以用来传输高速信号。两个内电层可以有效地屏蔽外界对Siganl_2(Inner_2)层的干扰和Siganl_2(Inner_2)对外界的干扰。

综合各个方面,方案3 显然是最优化的一种,同时,方案3 也是6 层板常用的层叠结构。在有些时候,某一个方案并不能满足所有的要求,这就需要考虑各项设计原则的优先级问题。遗憾的是由于电路板的板层设计和实际电路的特点密切相关,不同电路的抗干扰性能和设计侧重点各有所不同,所以事实上这些原则并没有确定的优先级可供参考。但可以确定的是,设计原则2(内部电源层和地层之间应该紧密耦合)在设计时需要首先得到满足,另外如果电路中需要传输高速信号,那么设计原则3(电路中的高速信号传输层应该是信号中间层,并且夹在两个内电层之间)就必须得到满足。

13、其它规则

阻抗计算:走线线宽的阻抗控制(也可以用通用的线宽,后续交由板厂微调处理)

层叠设置:信号层是正片层,非信号层是负片层(记得取消镜像的√),层叠的名称尽量简短(20H原则(70%):为了抑制边缘辐射效应,电源平面相对于地平面内缩(Pullback Distance)1mm(40mil)(电源60mil,地20mil),抑制70%的电场)(#号)(Pullback Distance)

取消:“Stack Symmetry”关联。

规则设置:先设置class:常用的网络类,差分类,Xsingle类

PWR类:所有的电源网络(MPU供电主电部分两倍线宽),可以关闭飞线(可以进行颜色设置(单击右键并且“显示替换”))

间距规则:大概5mil,如果板子密度不大可设置6mil,

线宽规则:添加电源线宽(PWR)加粗,信号线大概5mil,有计算阻抗可以用计算结果

过孔规则:和BGA相关,孔和盘的关系:2*n±2mil,n是孔直径(8mil往下风险高)

阻焊规则:紫色部分,推荐2.5mil防止绿油覆盖(油墨绝缘)

铺铜规则:PlaneConnect推荐全连接,反焊盘连接( PlaneClearance)(没有网络时的油墨)一般推荐7mil,正片层的铜皮设置(PloygonConnect):全连接散热快(机器贴(回流焊)消费类产品),十字焊盘连接(过流能力差,适合手工焊接)

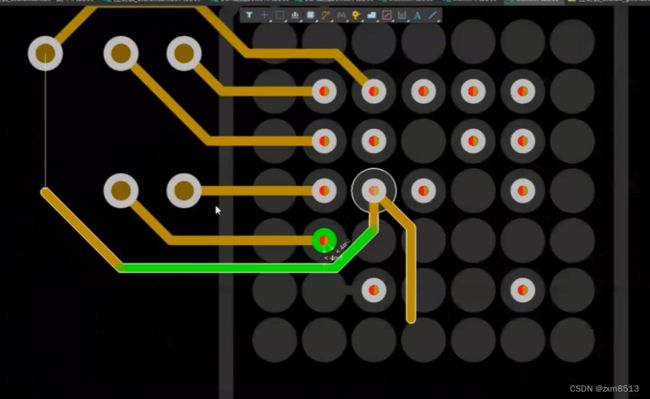

BGA扇孔:测量BGA间距(Ctrl+M)(距离1/2)设置原点(EOS),GG设置格点,放置过孔测试(RP),还原格点(1mil)单独设置VIA间距,可以用自动扇孔工具(UFO)

eMMC的BGA间距很小,可以直接连通NC PIN走出来。

DDR:电容平均分配(小的靠近管脚)(总分,再分),串阻放在CPU和DDR中间。

14、网络分类

自动扇出功能

一般情况下电源类的线宽和过孔范围比较宽,信号线的规则比较单一,因此,可以总设一类电源类,其它的通过配置查询条件实现:not InNetClass('Power') ,如下图所示:

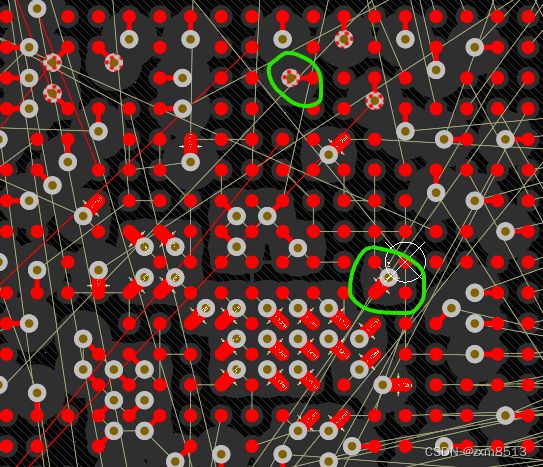

自动扇出的问题,比如电源地有很多都扇出没必有,可以根据实际情况合并一些扇出点,删除一些扇出孔。扇出效果如下图所示

15、布设电源分割层的分区

在Nets列表下,选择不同的网络,在右侧显示不同的电源系统,根据范围设置分区,间距适中20mil。

16、制作供电平层的说明文件(visio),便于布线使用

17、埋盲孔的作用

埋盲孔主要是应用在有的BGA的脚太密,空隙太小的情况下在BGA下埋孔,0.4、0.5、0.6,盲孔可以埋在焊盘正中间,也可以埋在偏一点的都可以。一般BGA之外都是用通孔。

一般0.65直径以上的一般不需要埋盲孔,用通孔,以下的一般需要埋盲孔。

18、布线过程中出现的问题汇总

1、如果有的BGA引脚出现DRC告警的话,可能是由于多层活其它设置造成的,清空层叠管理器,重新导入原理图,应该可以消除莫名的DEC错误。