SAR ADC系列16:CDAC上机实践+作业

目录

作业和上机实践:

通过仿真确定桥接电容Ca的尺寸

采样技术和CDAC相结合

电容校正

为什么在100...0和011...1之间最差:电容的瓶颈在MSB上面

为什么INL最差也发生在中间Code

其他问题

频谱混叠

上级板采样网络时序问题

共模相关问题

关于Vcm的问题

作业和上机实践:

- 假设单位电容C0的标准差为σ,4个C0组成的电容的标准偏差=?相对标准偏差呢?

答:4个C0的标准差=sqrt(4)*σ,相对标准差=σc/sqrt(4) - 假设单位电容C0的标准差为σ,C1和C2都等于1个C0,C1/C2的相对标准差=?

答:C1/C2的相对标准差=sqrt(2)*σc - “电容越大匹配越好,所以其标准偏差越小” 这句话正确与否?

答:不对,电容越大,匹配越好,是指其相对标准差小,但是绝对的标准偏差较大 - “单调性开关切换策略” 和 “Sanyal开关切换策略” 中比较器输入共模如何变化?

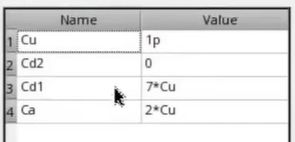

答:单调开关策略输入共模不断降低的,Sanyal开关策略的Vcm是想先上升在下降的,最终较为稳定。 - 10 bit CDAC,采用6+4结构,即MSB6位,LSB4位,要求桥接电容Ca=2Cu,求LSB部分寄生电容Cd2的大小

答:LSB的L=4,LSB阵列电容C=(2^4-1)*Cu,Ca/Cu = 2 = 1/(2^4-1)*CLt/Cu 则CLt=2*(2^4-1)*Cu = (2^4-1)*Cu + Cd2 则Cd2=2^4-1 。 - 分段结构CDAC,MSB上极板的寄生电容Cd1是否影响ADC的线性度?

答:MSB的上级板寄生电容Cd1不影响线性度,只影响CDAC的增益。 - 以下几种CDAC开关切换策略,哪些策略的比较器输入共模在转换过程中不变?

答:传统的开关切换,和 Vcm_Based切换 的输入共模Vcm不变。 - 从能耗的角度看,“VCM-Based开关切换策略”和“单调开关切换策略”哪个更优?

答:Vcm_Based更好一点

通过仿真确定桥接电容Ca的尺寸

1.不带冗余,并且,LSB寄生电容为0

此时,Ca=Cu,即桥接电容Ca的一个Cu抵一个LSB阵列电容(不含寄生)。

2.不含冗余,但是LSB存在上级板寄生电容

桥接电容Ca的一个Cu抵一个LSB阵列电容(不含寄生),寄生Cd1若为LSB阵列电容=(2^L-1)*Cu ,则LSB阵列总电容(含寄生)=两个LSB阵列电容(不含寄生),这Ca = 2*Cu。

即:桥接电容Ca加倍,LSB阵列总电容CLt也要加倍,LSB_DAC电容不变则寄生电容Cd1改变。

实际中,为了匹配,Ca必须为整数个Cu,然后凑Cd1,提取后仿看看Cd1为多少,Cd1不够的话,还需要人为补齐。具体数值迭代仿真几次

3.含冗余

MSB_low(8) = 2*LSB_high(4),权重2倍。这个冗余的Cc2可以看成是LSB寄生电容,Ca=2Cu,配平Cd1,使LSB_CDAC + Cc2 +Cd1 = 2*LSB_CDAC 。即Cd1 + Cc2 = LSB_CDAC。

仿真确定Ca的时候,用上面的方法,在MSB_low和LSB_high 加脉冲信号,看V1=2*V2 。也可以像图示的方法一样,将C7C8和Cc2连在一起(8),这样和 MSB_low(8)权重一样,这样只要V1=V2即可。

采样技术和CDAC相结合

复习:上级板采样精度不高,但是结构简单,尤其是和某些CDAC切换策略非常搭配,

下级板采样精度高,但是结构复杂,需要非交叠时钟。

虽然说上级板采样和某些CDAC很搭,但是并不是说下级板采样就不能用,举例如下:两种采样技术和单调开关切换策略结合。现实应用中,自由取舍。

1.上级板采样技术 和 单调开关切换策略 相结合

采样完直接进行比较,省一组MSB电容,省置位时间和功耗。开关也简单一点

2.下级板采样技术 和 单调开关切换策略 相结合

采样完成后需要将电容下级板复位,所有开关动作,浪费功耗和时间,开关复杂度稍高一点,但是采样精度高

电容校正

从MSB到LSB,电容时以权重1/2减小,失配以sqrt(2)增加;电容权重减小的速度,比失配增加的速度快。虽然MSB的电容绝对失配大,但是他的失配归一化最小,相当于,低位电容,对失配不是那么敏感,允许的失配范围更大,出来的code精度更高。

因此,要校正,必须先校正高位电容MSB,如果由于随机失配而产生DNL、INL,其瓶颈一定在MSB上面。

为什么在100...0和011...1之间最差:电容的瓶颈在MSB上面

对于传统的全差分的CDAC:

从匹配的角度:当P阵列和N阵列的MSB存在mismatch,则第一次编辑判1的的地方就不是绝对的1/2Vref了,因此MSB的匹配很重要。

从随机失配的角度:DNL最差的情况一定发生在Code一半的时候,MSB失配大,允许的失配更小。

对于全差分CDAC:

从匹配的角度:采样完成直接比较,不需要猜1,MSB的精度得到保证,次高位的匹配重要。

从随机失配的角度:同上,MSB依旧重要,但是和传统的相比,MSB对匹配度的影响降低了。

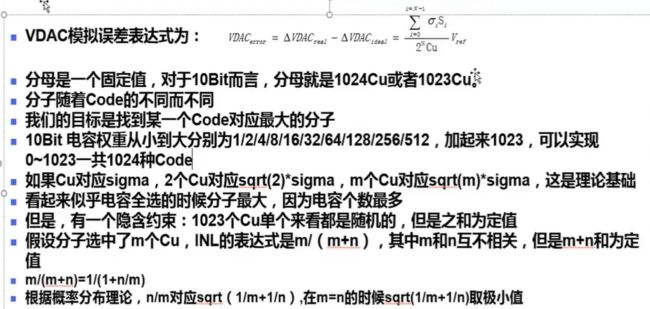

为什么INL最差也发生在中间Code

其他问题

对于全差分的结构CDAC,CDAC电容面积瞬间减半?不一定(有争议)

首先看看CDAC的电容由什么决定:(1)KT/C噪声;(2)mismatch

最终单位电容取值是取较大的那个,对于全差分结构,有人说省了一个MSB,电容面积减半。但是,可能电容值下降了,导致不满足KT/C噪声。因此,节省不一定是一半的电容。

(不确定啊,存在争议)

有人有问题,单端结构CDAC能够省电容,错误的

首先,如果是传统的切换策略,差分结构确实比单端的电容翻倍。如果是采样完直接相比,差分结构不需要2*MSB,折算下来,和单端的电容数量面积是一样的。

从Noise的角度,假设单端电容总数为C,Noise0 = KT/C 。差分两个阵列,一边一个1/2*C,则每一边的噪声都为2*KT/C,总的 Noise1 = 4*KT/C = 4*Nosie0。差分Noise增大了

从信噪比的角度,单端信号Vin,信号功率Pin0(Vin平方),信噪比 Pin0/Noise0。 差分信号为2*Vin,信号功率为4*Pin0,即,信号功率X4倍,噪声X4倍,信噪比不变 = 单端。

因此,单独并不能省面积和信噪比,而差分结构好处多多,抑制欧次谐波、省MSB啊、最差的Code在次高位啊等等。

频谱混叠

谐波与基波的关系:fin = M*fs/N,信号是基波 fs/N 的整数倍,谐波是信号的整数倍,所以谐波也是基波的整数倍。

时域的相乘等于频域的卷积,频谱搬移,默认大家了解信号与系统知识了啊。采样定理需要fs>2*fin才能无失真还原,而当 fin>1/2*fs 时,会发生频谱混叠。此时DFT输出的信号频率不等于输入信号频率,把fin搬移了。

三次谐波频谱混叠(3*fin)

------------更新-----------------------

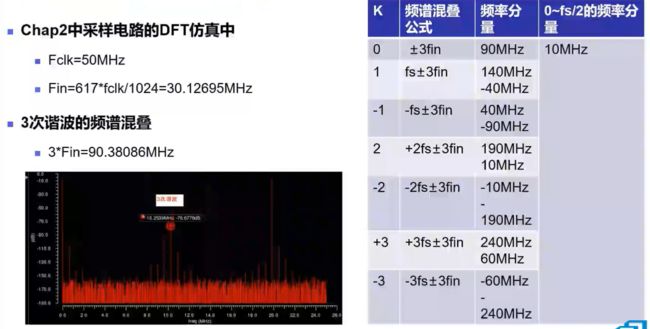

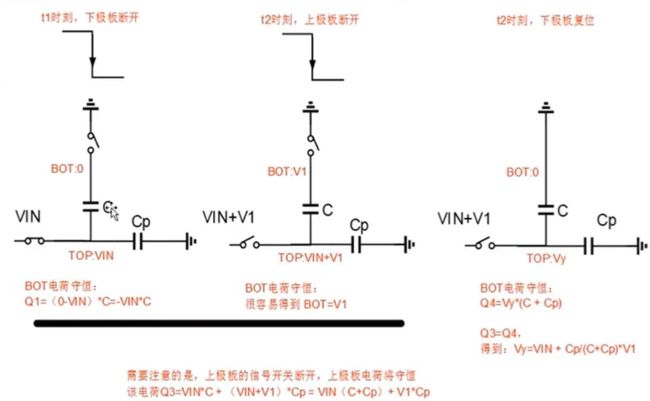

上级板采样网络时序问题

如果先断开上级板的话:——这样是不行的。

1.CDAC下级板有寄生

首先明确,电荷守恒是针对某一个点来说的,不是针对整个电容,是一个极板一个极板的分析。然后,提个建议,对哪个点进行电荷守恒分析,就把哪个点的电压写在前面。

采样阶段:采样开关和切换开关都导通,BOT=0;TOP=VIN;

t1时刻下级板断开:BOT开始电荷守恒Q1,BOT = 0,则CP两端都为0,没有电荷可忽略;对C分析,Q1 = (0 - VIN)*C = -VIN*C。

t2时刻上级板断开:TOP开始电荷守恒,同时BOT也是电荷守恒状态。假设t1和t2之间,TOP变化了V1,则 TOP=VIN+V1,因为BOT一直电荷守恒,TOP变则BOT也变,但是此时BOT连接两个电容 C和Cp 。假设 BOT=Vx,对BOT分析:Q2 = (Vx - VIN -V1)*C + (Vx-0)*Cp (电容分压);BOT的 Q1=Q2 可以得到,Vx = V1*C /(C+Cp) ;对TOP分析:Q3 = (VIN +V1 -Vx)*C = VIN*C+ Cp/(C+Cp)*V1*C 。

切换阶段下级板复位:BOT = 0,(Cp又可忽略);TOP还是电荷守恒,Q4 = (Vy-0)*C ;Q4 = Q3 则,Vy = VIN + V1*Cp/(C+Cp) ;实际通过电容分压,TOP电荷守恒,BOT从Vx变为0,只有C没有其他电容,直接耦合到TOP点,使TOP点电压下降Vx,即TOP=Vy=VIN + V1 -Vx = VIN + V1*Cp/(C+Cp) 。

很显然,这样是不行的,因为采了一个四不像,和Cp有关。

2.CDAC上级板有寄生

很显然,这样也是不行的。

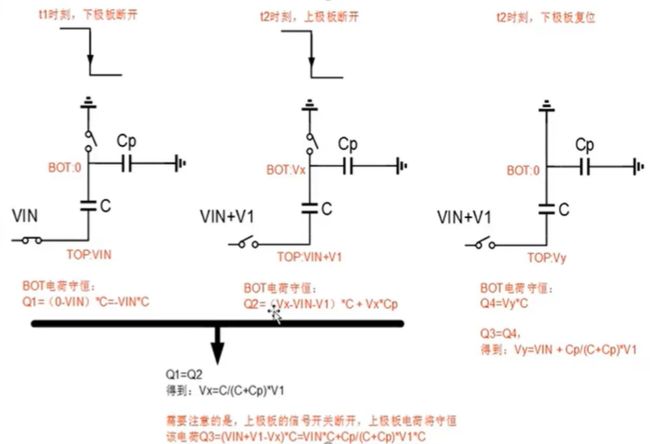

共模相关问题

假设三个开关连到三个共模上(可以不相同,一般Vin的共模为1/2*Vdd,)

采样阶段:上级板开关断开瞬间,TOP电荷守恒,Q1=(Vcm1 - Vin)*C ;

保持阶段:下级板开关导通,TOP电荷守恒,Q2=(TOP2 - Vcm2)*C;

Q1 = Q2 ,得出 TOP2 = Vcm1 - Vin +Vcm3 ;

假设Vin为Vcm2:

即:上级板是一个,共模 = Vcm1 - Vcm2 + Vcm3,幅度 = amp ,的交流信号。

上级板最大值 = (共模) + amp,最小值 = (共模) - amp ,

在输入满量程的情况下,amp = Vref/2

为了保证TOP共模在0~Vdd之间,需要确保TOP的共模(Vcm1-Vcm2+Vcm3) 在 Vref/2 ~(Vdd-Vref/2) 之间 。

-------------更新-------------------------

关于Vcm的问题

首先:一般在先进工艺下,想28nm,14nm,7nm这样,Vdd都低于1V了,但是管子的Vth并没有变化。

此时,电路中想用一个1/2*Vdd的Vcm变得很困难。简单来说,这个Vcm的开关,就不能用传输门,因为Vcm接近Vth,P管和N管接近不导通状态,阻抗贼大。如果用Bootstrap的话,速度又跑不太快,既然用先进工艺,肯定是想要速度快,但是时钟快了,Bootstrap开关噪声啊、馈通啊等效应就明显了。一般只能用单个MOS管,单个MOS管的话,Vcm也是接近Vth,不是很理想,所以Vcm电压一般在先进工艺下不适用。

这里说的的Vcm是当做CDAC的reference来用的,CDAC的reference想要等于1/2*Vdd,一般采用电容分压Vdd和gnd得到。这样的话,功耗又大了起来,对于电源buffer也有一定的要求。

本来用Vcm_Based策略是想要省功耗,分压得到1/2*Vdd的Vcm功耗稍大,能用,但是不算太好的方法。

具体怎么分压的看我前面的文章。