- 跨境侵权TRO,和解金要赔偿多少?

跨境卖家们,遇到店铺被TRO(临时限制令),最揪心的除了资金冻结,就是“和解金到底得掏多少”!今天,赛贝凭借多年跨境维权的实战经验,从冻结金额、销售数据、过往案例、律所风格这四大关键维度,来给大家讲讲TRO和解金应该怎么预估!1、冻结金额:对方的“基础参考线”在TRO和解的博弈中,冻结金额就像是对方手中的一把“标尺”,直接衡量着你的“家底厚薄”。通常情况下,冻结金额越高,对方越会认为你资金实力雄厚

- 云原生环境下的安全控制框架设计

TechVision大咖圈

云原生Kubernetes安全云原生安全安全框架设计零信任微服务安全

在这个容器满天飞、微服务遍地跑的时代,安全问题就像打地鼠游戏一样,刚按下一个又冒出三个。今天我们来聊聊如何在云原生环境中构建一套靠谱的安全控制框架。文章目录引言:云原生时代的安全新挑战云原生安全面临的核心挑战安全控制框架设计原则框架核心组件详解安全控制策略实施最佳实践与案例分析总结与展望引言:云原生时代的安全新挑战还记得以前那种"铁桶阵"式的安全防护吗?外面围一圈防火墙,里面的服务器老老实实待在机

- 随心

空青海

难过了就哭吧,也许……对有些人来说眼泪是有价值的、但是对于我来说眼泪就是发泄情绪的一种方式。哭过就好。不算什么懦不懦弱图片发自App

- 长篇小说丨珍珠湾57

蒋坤元

这天夜里,素素和明珍睡在一张床上。这一间屋子里有两张床,另一张床则由明龙睡的。那年代,乡下并不富裕,所以明珍兄妹两人还是睡在一个房间。明珍说:“今天委屈你了,让你与我挤一张小床。”素素说:“我习惯没床睡觉的。”“啊,你睡觉在地上吗?”“我睡在船上。”“如果刮风下雨还睡在船上吗?”“一年365天都睡在船上。”“你真是以船为家。”“所以,我看你这个房间心里感觉还是蛮宽敞的。”而明龙在床上也睡不着。明珍

- 【AI大模型:架构实战】35、企业级AI中台全链路架构设计与实战指南:从数据管理到智能服务

无心水

人工智能AI大模型系统实战AI大模型高手AI大模型企业落地CSDN技术干货AI中台AI入门

在企业智能化转型过程中,AI能力的规模化复用与高效管理成为核心挑战。AI中台作为连接技术与业务的桥梁,通过标准化能力输出、集中化资源管控和全链路治理,解决了"重复建设、资源浪费、安全失控"等痛点。本文基于2025年最新实践,详解企业AI中台的架构设计、关键技术实现、落地路径及避坑指南,助力企业构建支撑千级AI应用的"智能中枢"。一、AI中台核心定位与整体架构企业级AI中台并非简单的技术堆砌,而是以

- Python+requests+pytest接口自动化测试框架的搭建

天才测试猿

python自动化测试软件测试测试用例职场和发展pytest测试工具

点击文末小卡片,免费获取软件测试全套资料,资料在手,涨薪更快框架的设计思路首先要明确进行接口自动化需要的步骤,如下图所示:然后逐步拆解需要完成的工作:1)了解分析需求:了解接口要实现的功能2)数据准备:根据开发文档确定接口的基本情况,知晓接口的url、请求方式、入参等信息,然后根据业务逻辑以及入参来预期接口的输出需要有一个配置文件来存储接口的一些基本信息;需要有一个方法能读取配置文件;需要有一个e

- 老书虫强烈推荐小说舔狗舔到最后,她又丢钱又丢命小说-小说赵庭深沈熹微是完整版在线阅读

花朵文库

老书虫强烈推荐小说舔狗舔到最后,她又丢钱又丢命小说-小说赵庭深沈熹微是完整版在线阅读主角配角:赵庭深沈熹微小说别名:沈熹微感染艾滋死的那天,是裴云霄结婚的日子。【戳我继续阅读】孟清然这会儿趴在桌上,被一群人众星捧月的围着。她胃痛,大家都在关心她。最关心她的人,当然是裴云霄。他是孟清然的男朋友。每次考试排名,第一第二都是他俩,裴云霄对其它人冷淡,对孟清然很好。别人眼里,他们就是天造地设的一对。是金童

- 杨蕊今日份总结

羊鑫

2020年1月15日周三今天早上早早起床,出门是有点冷,不过还得保持好心情,因为今天孩子要来上课!今天上午孩子还挺多的!大部分都是小男生,跟调皮,不过有的孩子也很听话,懂事儿,先是复习了短横,学了长横和几个字,孩子们真的挺认真的,我也告诉他们让他们回家按照什么样的方式去写字,练字,告诉他们一点一点的努力才能变出想要的未来…下午只有5个孩子,人少学的也多,告诉他们上课就好好上课,下课就放松放松,劳逸

- 踏访西门岩子山(原创文学064)

风雅颂歌

周末,是我们远足爬山的快乐时光。距离普洱县城西边约1公里,有座山西门岩子山,海拔1838.3米,与县城相对高差518.8米,属典型的喀斯特地形地貌,原为火山,险峻挺拔,气势磅礴,云雾萦绕,山峦叠翠,雄伟壮丽。山中多有榕树,与岩石伴生,其根紧缚峭岩,如蟠龙抱石,似山石大盆景天然成就于山中。岩石陡峭,拔地而起,山势如壁,耸入云天。每当晨曦初照,薄雾缭绕,常出现飞霞焕彩、色彩斑斓的瑰丽景色,更为奇特的是

- Visual Autoregressive Modeling: Scalable Image Generation via Next-Scale Prediction

zzfive

生成模型论文阅读kotlin开发语言android

论文链接:VisualAutoregressiveModeling:ScalableImageGenerationviaNext-ScalePrediction文章目录简介预测下一个token自回归模型范式分析VAR详解分词实现细节幂律缩放定律零样本泛化能力结论简介本文提出的视觉自回归建模/VAR这种新范式,其将图像的自回归学习重新定义为从粗到细的“下一个尺度预测”或“下一个分辨率预测”,与常规的

- 大模型聊天模板

文章目录何为聊天模板聊天模板具体长什么样为什么会出现聊天模板何为聊天模板相信大多数本地离线使用过(特别是训练或微调过)LLM、VLM的人知道“Chattemplate/聊天模板”这个概念,但可能并没有对其有较多的了解。本文主要整合网络收集的知识,结合少数使用“聊天模板”的经验对其进行简要说明,希望可以帮助到大家。如果了解Alpaca、ShareGPT等数据集会知道,数据集都是结构化形式,其中会有各

- 2022-07-09

Serendpy

有些路,不走下去,你就不会知道前面的风景有多美。人生的路,你只有走下去,才会知道它有多么精彩!请您坚定执着的走好选择的每一步,因为每一个不曾起舞的日子,都是对生命的辜负。生活中的人们,就要拿得起,放得下,走得正,行得稳。跌倒了,重新站起;失利了,重新开始。没什么大不了,没什么可自责,只要用心的面对生活,每一天都将会呈现精彩,每一天都将给你带来快乐!

- 羽毛球拍3u和4u 5u的区别

氧惠爱高省

羽毛球拍是羽毛球运动必备的装备之一,它的主要功能是帮助玩家击打羽毛球,而且还有帮助玩家调整击球方向、力度的作用。羽毛球拍的种类很多,主要有单板、双板和四板三种。其中单板羽毛球拍最为常见,适用于大多数玩家,四板羽毛球拍则更适合于专业运动员使用。购物、看电影、点外卖、用氧惠APP!更优惠!氧惠(全网优惠上氧惠)——是与以往完全不同的抖客+淘客app!2023全新模式,我的直推也会放到你下面,送1:1超

- 宝贝的讨价还价

蓝色逍遥398

2019年1月28日晴星期一“猪爸,我要不要背诵伯父布置的诗啊?”早上九点多,宝贝给我发来微信。昨天,猪媽和我忙完贴墙纸的活儿之后,便带着宝贝和爷爷一起去往伯父家,将宝贝送去伯父家小住几日。这已经成为姐妹俩每逢寒暑假的固定项目,俩小家伙为此都盼着这一刻的到来。因为伯父家在学校里,安全系数相对来说要高,且宝贝和妹妹活动的区域会更广更大,所以猪媽虽然有些不舍,但这可是宝贝盼望的,所以也只能同意。每次去

- 系统崛起☞【分手后,我觉醒了日抛金手指】颜晶晶陆鸣轩⊙﹏⊙全文一更到底完整阅读!

妞妞爱读书1

“恭喜,你怀孕了!”医生面带微笑的对颜晶晶说出这句话。颜晶晶却如遭雷劈。她都不知道自己是如何从医院离开的。等她从浑浑噩噩中清醒时,已经回到了出租屋中。这个月,可真是她的黑色灾难月。月初时,交往两年多的男朋友突然说要去执行危险任务,可能有去无回,所以和她提了分手。没错,颜晶晶的男朋友是一名军人。肩宽腿长,八块腹肌,还超帅!她对人家一见钟情,然后花费了点心思才将人追到手。虽然总是聚少离多,但颜晶晶真的

- 速度在情节中的规则57/1000

妙妹妹

小慧继续站在了游泳池里面,他感觉到这个天地之中都会有人会有人一定会有人小慧说我们一定会感觉到你。我感觉到你好像好像在这里面出现的时间有一些长了,你可以不可以不要在这里面站着,然后说我不在这里面站,那我在哪里找你?那个人说你们在这里面站着,你自然可以去很远的地方站着呀,那里会有一个人和那人等着你,那个人是谁?没有人知道,大家只知道的只是有人在远处也等待着小慧,小慧也在这里等待着那个人,最后他们决定去

- 柳璃雅王逸(妻心如铁,我爱已殇)爽文好看小说-最新章节柳璃雅王逸(妻心如铁,我爱已殇)

时光里文馆

《妻心如铁,我爱已殇》主角:柳璃雅王逸天简介:老婆的白月光让人打断了腿,她怀疑是我做的。柳璃雅将我带到她白月光挨打的那座废弃工厂里,命人将我打的奄奄一息。“记住,我绝对不会允许有人伤害王昊,那怕你是我的老公,都不行!”说完,她便带着人扬长而去,只留下躺在血泊中的我。我绝望的盯着她的背影。一周之后,柳璃雅带人回来,可我的尸体早已经让野狗撕碎了。第二天,柳璃雅刚到公司。“柳总,下面的人说,有好几份文件

- 如何优雅解决缓存与数据库的数据一致性问题?

亲爱的非洲野猪

缓存kafka分布式javalock

在高并发系统中,缓存是提升性能的“利器”,但随之而来的“缓存与数据库数据不一致”问题,却常常让开发者头疼。比如用户刚更新了资料,刷新页面却还是旧数据;或者订单状态明明已支付,缓存却显示未付款——这类问题不仅影响用户体验,严重时甚至会引发业务故障。今天就来聊聊如何从“更新策略”“异常处理”“实战方案”三个维度,搭建一套可靠的缓存一致性管控体系。一、核心更新策略:根据业务选对“姿势”缓存与数据库的同步

- 2023-01-27

多持

抗癌成功纪实:阳光总在风雨后“小蔡姐,为什么你那么快乐啊?”年轻人看到我步履轻盈、满面春风地出现在办公室,常常羡慕地问我。的确,现在我在单位与同事们相处融洽,工作也轻松愉快;在家中先生体贴能干,孩子懂事孝顺,最关键的是我有随缘从容的心态和健康的身体。不知内情的人根本无法想象,两年前与死神擦肩而过的那个癌症患者,和如今健康的我是同一人。至今想来,那段炼狱般的日子仍令我不寒而栗。2019年4月的一天,

- 107悟第23天2022-04-21

Diana_58d9

1、好事情事件:今天去看闺蜜,闺蜜腰椎不好,精神也不好,整个人都没精神,我很开心(1)提醒我以后要经常与好朋友保持连接(2)今天虽然没有支持到她,以后还有机会(3)我的状态也会对她有触动(4)每个人的家庭情况不同,她有自己的原生家庭(5)她这个情况只是暂时的(6)人生都会有起伏(7)让我更有动力好好学习成长,帮助更多的人幸福具体用到的是哪一个知识点来转化好事情的,怎么理解?没有两个人是一样的;只有

- 从头学前端-HTML简介

liangblog

笔记前端htmljavascript

HTML简介:先说下什么是网页:网页是网站中的页面,通长是HTML格式的文件,单个或多个页面就组成了一个网站;现在的技术发展到一般都是单页应用,在一个页面中,通过页面跳转的方式,访问不同数据页面;网页基本都是通过浏览器访问;网页主要有图片,文字、链接、视音频等元素组成;使用不同的标签引入元素;最终生成的文件和展示的方式一般都是html或htm文件;什么是HTMLHTML是超文本标记语言《Hyper

- 成功日记(Day492)

狮子座的兔子姑娘

1、跟老师出诊。~4.5h。2、和z鹤学弟聊天。~1h。3、整理笔记。~0.5h。4、看了l玲公众号好几篇文章,打赏了她,并且和她聊聊天。~0.5h。5、写了一篇日记,算是对最近生活的梳理。感悟:发现自己已经离不开日记了。包括成功日记和心里话日记。心情:还可以。

- 入院第一天

101酷狗

今天是入院的第一天。按照计划,应该昨天入院。结果因为新冠疫情,核算检测没有拿到结果,所以拖到今日才入院。各种检查,排队,等待。一早和明天来照顾我的陪护大姐在医院碰头。一个看起来很清洁、干练、热心肠的大姐。年纪应该比我小些。由于没有核算检查结果,她只能明天拿到结果后才能进病房。现在病房非常的清静。旁边一个清秀的姑娘,也是明天手术。手不释卷的样子,我很是喜欢。忍不住猜想,如果我右手边的姑娘也是个爱学习

- Elasticsearch 聚合查询源码解读与架构方法论

北漂老男人

Elasticsearchelasticsearch架构大数据搜索引擎全文检索

Elasticsearch聚合查询源码解读与架构方法论01.引言Elasticsearch的聚合查询(Aggregation)是大规模分布式数据分析的核心能力。理解其源码结构与设计方法论,不仅有助于高效使用聚合,也能为自定义扩展、性能优化、集群运维等提供理论与实践基础。本文将从源码结构、核心模块、关键实现、行级注释与方法论出发,系统剖析聚合查询的底层原理。02.源码结构与核心模块2.1聚合相关源码

- 思索影响之日久生情

conquer_jhf

今天是日更打卡第143天,说长不长,说短不短。当打卡快90天的时候,我就特别期盼100天,我把第100天准备要写的内容都提前想好了,自然是要简单总结一下这100天都写了什么,有没有什么收获。过了100天,又觉得时间慢了些,才一百零几,慢慢的也就坚持到现在了。这可能就是日久生情吧。12月的主题是:“一起写吧”的影响,我是要好好斟酌一下。大概有以下这么几方面!一、岁月的痕迹(生活琐事)参与日更打卡以前

- 记【第0046次】

拾有启发

【早起】第2个在早起群打卡,打卡时间是4:46,被楼下喊醒了,要早早的去做核酸。睡眠打分73分,夜间睡眠时长4小时27分(从0:11睡到4:39),这个时长有点低。快速眼动比例偏低。昨天,没有写日记,因为,又吵了起来:原因是前天晚上没聊开,还在纠结,纠结的不行不行了,像个病人,担心会做出傻事的病人。晚上问:将家里药箱里的药都吃掉会不会死掉?所有的行为像个病人,就当病人对待吧。【运动】一次。晚上20

- 2018-11-24

李茂旭

昨晚说好的跟他爸一起睡,但是不到十点就跑到我房间求着要跟我睡,说他爸的呼噜声太大了,睡不着。今天晚上他爸还叫他,他说什么也不去了,也不搭理他。下午把作业都做完,说明天让我陪他看电影的我答应了,很长时间没陪他看了,满足一下他吧。

- 2020-3-28晨间日记

赖着不走

今天是什么日子起床:上午11:00就寝:半夜2:30天气:下着雨17度太舒服了心情:好像睡了很久纪念日:减肥第34天任务清单昨日完成的任务,最重要的三件事:1.今日事今日毕。2.跟进目标进度。3.学习是一种态度。改进:依然是时间掌握习惯养成:减肥对身体健康好周目标·完成进度文案资料收集提供具体方案等待下周一开会学习·信息·阅读閱读工具书写文章健康·饮食·锻炼运动是一个很好的选择减少淀粉摄取无糖饮料

- 往生茧 | 痴情郎 惆怅客

安徽农业大学

痴情郎,惆怅客“我是人间惆怅客,知君何事泪纵横,断肠里忆平生。”一篇《浣溪沙》,给予了纳兰性德“惆怅客”之名,词中隐隐表现出的清冷的孤单为世人感慨。我不知道他是在何种的环境以何种心情写下这词,我知道的是人中龙凤、才华横溢的纳兰性德,也有他自己心灵的忧伤和寂寞。纳兰性德,清代词人,原名纳兰成德,避太子保“成”讳改名为性德,字容若,号楞伽山人。清朝康熙时期武英殿大学士、一代权臣纳兰明珠之子。容若自幼饱

- PowerPCB(PADS)常见问题全集

weixin_33774308

数据库

来自:http://hi.baidu.com/huxianfangyuan/blog/item/01bdff730259c5168701b08d.html1、走线很细,不是设定值`有时将预拉线布好线后,所布的线变成了一根很细的线而不是我们所设定的线宽,但是查看它的属性也还是一样的最小线宽显示值的设定大于route线宽。setup--preferences--global--minimumdispl

- 桌面上有多个球在同时运动,怎么实现球之间不交叉,即碰撞?

换个号韩国红果果

html小球碰撞

稍微想了一下,然后解决了很多bug,最后终于把它实现了。其实原理很简单。在每改变一个小球的x y坐标后,遍历整个在dom树中的其他小球,看一下它们与当前小球的距离是否小于球半径的两倍?若小于说明下一次绘制该小球(设为a)前要把他的方向变为原来相反方向(与a要碰撞的小球设为b),即假如当前小球的距离小于球半径的两倍的话,马上改变当前小球方向。那么下一次绘制也是先绘制b,再绘制a,由于a的方向已经改变

- 《高性能HTML5》读后整理的Web性能优化内容

白糖_

html5

读后感

先说说《高性能HTML5》这本书的读后感吧,个人觉得这本书前两章跟书的标题完全搭不上关系,或者说只能算是讲解了“高性能”这三个字,HTML5完全不见踪影。个人觉得作者应该首先把HTML5的大菜拿出来讲一讲,再去分析性能优化的内容,这样才会有吸引力。因为只是在线试读,没有机会看后面的内容,所以不胡乱评价了。

- [JShop]Spring MVC的RequestContextHolder使用误区

dinguangx

jeeshop商城系统jshop电商系统

在spring mvc中,为了随时都能取到当前请求的request对象,可以通过RequestContextHolder的静态方法getRequestAttributes()获取Request相关的变量,如request, response等。 在jshop中,对RequestContextHolder的

- 算法之时间复杂度

周凡杨

java算法时间复杂度效率

在

计算机科学 中,

算法 的时间复杂度是一个

函数 ,它定量描述了该算法的运行时间。这是一个关于代表算法输入值的

字符串 的长度的函数。时间复杂度常用

大O符号 表述,不包括这个函数的低阶项和首项系数。使用这种方式时,时间复杂度可被称为是

渐近 的,它考察当输入值大小趋近无穷时的情况。

这样用大写O()来体现算法时间复杂度的记法,

- Java事务处理

g21121

java

一、什么是Java事务 通常的观念认为,事务仅与数据库相关。 事务必须服从ISO/IEC所制定的ACID原则。ACID是原子性(atomicity)、一致性(consistency)、隔离性(isolation)和持久性(durability)的缩写。事务的原子性表示事务执行过程中的任何失败都将导致事务所做的任何修改失效。一致性表示当事务执行失败时,所有被该事务影响的数据都应该恢复到事务执行前的状

- Linux awk命令详解

510888780

linux

一. AWK 说明

awk是一种编程语言,用于在linux/unix下对文本和数据进行处理。数据可以来自标准输入、一个或多个文件,或其它命令的输出。它支持用户自定义函数和动态正则表达式等先进功能,是linux/unix下的一个强大编程工具。它在命令行中使用,但更多是作为脚本来使用。

awk的处理文本和数据的方式:它逐行扫描文件,从第一行到

- android permission

布衣凌宇

Permission

<uses-permission android:name="android.permission.ACCESS_CHECKIN_PROPERTIES" ></uses-permission>允许读写访问"properties"表在checkin数据库中,改值可以修改上传

<uses-permission android:na

- Oracle和谷歌Java Android官司将推迟

aijuans

javaoracle

北京时间 10 月 7 日,据国外媒体报道,Oracle 和谷歌之间一场等待已久的官司可能会推迟至 10 月 17 日以后进行,这场官司的内容是 Android 操作系统所谓的 Java 专利权之争。本案法官 William Alsup 称根据专利权专家 Florian Mueller 的预测,谷歌 Oracle 案很可能会被推迟。 该案中的第二波辩护被安排在 10 月 17 日出庭,从目前看来

- linux shell 常用命令

antlove

linuxshellcommand

grep [options] [regex] [files]

/var/root # grep -n "o" *

hello.c:1:/* This C source can be compiled with:

- Java解析XML配置数据库连接(DOM技术连接 SAX技术连接)

百合不是茶

sax技术Java解析xml文档dom技术XML配置数据库连接

XML配置数据库文件的连接其实是个很简单的问题,为什么到现在才写出来主要是昨天在网上看了别人写的,然后一直陷入其中,最后发现不能自拔 所以今天决定自己完成 ,,,,现将代码与思路贴出来供大家一起学习

XML配置数据库的连接主要技术点的博客;

JDBC编程 : JDBC连接数据库

DOM解析XML: DOM解析XML文件

SA

- underscore.js 学习(二)

bijian1013

JavaScriptunderscore

Array Functions 所有数组函数对参数对象一样适用。1.first _.first(array, [n]) 别名: head, take 返回array的第一个元素,设置了参数n,就

- plSql介绍

bijian1013

oracle数据库plsql

/*

* PL/SQL 程序设计学习笔记

* 学习plSql介绍.pdf

* 时间:2010-10-05

*/

--创建DEPT表

create table DEPT

(

DEPTNO NUMBER(10),

DNAME NVARCHAR2(255),

LOC NVARCHAR2(255)

)

delete dept;

select

- 【Nginx一】Nginx安装与总体介绍

bit1129

nginx

启动、停止、重新加载Nginx

nginx 启动Nginx服务器,不需要任何参数u

nginx -s stop 快速(强制)关系Nginx服务器

nginx -s quit 优雅的关闭Nginx服务器

nginx -s reload 重新加载Nginx服务器的配置文件

nginx -s reopen 重新打开Nginx日志文件

- spring mvc开发中浏览器兼容的奇怪问题

bitray

jqueryAjaxspringMVC浏览器上传文件

最近个人开发一个小的OA项目,属于复习阶段.使用的技术主要是spring mvc作为前端框架,mybatis作为数据库持久化技术.前台使用jquery和一些jquery的插件.

在开发到中间阶段时候发现自己好像忽略了一个小问题,整个项目一直在firefox下测试,没有在IE下测试,不确定是否会出现兼容问题.由于jquer

- Lua的io库函数列表

ronin47

lua io

1、io表调用方式:使用io表,io.open将返回指定文件的描述,并且所有的操作将围绕这个文件描述

io表同样提供三种预定义的文件描述io.stdin,io.stdout,io.stderr

2、文件句柄直接调用方式,即使用file:XXX()函数方式进行操作,其中file为io.open()返回的文件句柄

多数I/O函数调用失败时返回nil加错误信息,有些函数成功时返回nil

- java-26-左旋转字符串

bylijinnan

java

public class LeftRotateString {

/**

* Q 26 左旋转字符串

* 题目:定义字符串的左旋转操作:把字符串前面的若干个字符移动到字符串的尾部。

* 如把字符串abcdef左旋转2位得到字符串cdefab。

* 请实现字符串左旋转的函数。要求时间对长度为n的字符串操作的复杂度为O(n),辅助内存为O(1)。

*/

pu

- 《vi中的替换艺术》-linux命令五分钟系列之十一

cfyme

linux命令

vi方面的内容不知道分类到哪里好,就放到《Linux命令五分钟系列》里吧!

今天编程,关于栈的一个小例子,其间我需要把”S.”替换为”S->”(替换不包括双引号)。

其实这个不难,不过我觉得应该总结一下vi里的替换技术了,以备以后查阅。

1

所有替换方案都要在冒号“:”状态下书写。

2

如果想将abc替换为xyz,那么就这样

:s/abc/xyz/

不过要特别

- [轨道与计算]新的并行计算架构

comsci

并行计算

我在进行流程引擎循环反馈试验的过程中,发现一个有趣的事情。。。如果我们在流程图的每个节点中嵌入一个双向循环代码段,而整个流程中又充满着很多并行路由,每个并行路由中又包含着一些并行节点,那么当整个流程图开始循环反馈过程的时候,这个流程图的运行过程是否变成一个并行计算的架构呢?

- 重复执行某段代码

dai_lm

android

用handler就可以了

private Handler handler = new Handler();

private Runnable runnable = new Runnable() {

public void run() {

update();

handler.postDelayed(this, 5000);

}

};

开始计时

h

- Java实现堆栈(list实现)

datageek

数据结构——堆栈

public interface IStack<T> {

//元素出栈,并返回出栈元素

public T pop();

//元素入栈

public void push(T element);

//获取栈顶元素

public T peek();

//判断栈是否为空

public boolean isEmpty

- 四大备份MySql数据库方法及可能遇到的问题

dcj3sjt126com

DBbackup

一:通过备份王等软件进行备份前台进不去?

用备份王等软件进行备份是大多老站长的选择,这种方法方便快捷,只要上传备份软件到空间一步步操作就可以,但是许多刚接触备份王软件的客用户来说还原后会出现一个问题:因为新老空间数据库用户名和密码不统一,网站文件打包过来后因没有修改连接文件,还原数据库是好了,可是前台会提示数据库连接错误,网站从而出现打不开的情况。

解决方法:学会修改网站配置文件,大多是由co

- github做webhooks:[1]钩子触发是否成功测试

dcj3sjt126com

githubgitwebhook

转自: http://jingyan.baidu.com/article/5d6edee228c88899ebdeec47.html

github和svn一样有钩子的功能,而且更加强大。例如我做的是最常见的push操作触发的钩子操作,则每次更新之后的钩子操作记录都会在github的控制板可以看到!

工具/原料

github

方法/步骤

- ">的作用" target="_blank">JSP中的作用

蕃薯耀

JSP中<base href="<%=basePath%>">的作用

>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>>

- linux下SAMBA服务安装与配置

hanqunfeng

linux

局域网使用的文件共享服务。

一.安装包:

rpm -qa | grep samba

samba-3.6.9-151.el6.x86_64

samba-common-3.6.9-151.el6.x86_64

samba-winbind-3.6.9-151.el6.x86_64

samba-client-3.6.9-151.el6.x86_64

samba-winbind-clients

- guava cache

IXHONG

cache

缓存,在我们日常开发中是必不可少的一种解决性能问题的方法。简单的说,cache 就是为了提升系统性能而开辟的一块内存空间。

缓存的主要作用是暂时在内存中保存业务系统的数据处理结果,并且等待下次访问使用。在日常开发的很多场合,由于受限于硬盘IO的性能或者我们自身业务系统的数据处理和获取可能非常费时,当我们发现我们的系统这个数据请求量很大的时候,频繁的IO和频繁的逻辑处理会导致硬盘和CPU资源的

- Query的开始--全局变量,noconflict和兼容各种js的初始化方法

kvhur

JavaScriptjquerycss

这个是整个jQuery代码的开始,里面包含了对不同环境的js进行的处理,例如普通环境,Nodejs,和requiredJs的处理方法。 还有jQuery生成$, jQuery全局变量的代码和noConflict代码详解 完整资源:

http://www.gbtags.com/gb/share/5640.htm jQuery 源码:

(

- 美国人的福利和中国人的储蓄

nannan408

今天看了篇文章,震动很大,说的是美国的福利。

美国医院的无偿入院真的是个好措施。小小的改善,对于社会是大大的信心。小孩,税费等,政府不收反补,真的体现了人文主义。

美国这么高的社会保障会不会使人变懒?答案是否定的。正因为政府解决了后顾之忧,人们才得以倾尽精力去做一些有创造力,更造福社会的事情,这竟成了美国社会思想、人

- N阶行列式计算(JAVA)

qiuwanchi

N阶行列式计算

package gaodai;

import java.util.List;

/**

* N阶行列式计算

* @author 邱万迟

*

*/

public class DeterminantCalculation {

public DeterminantCalculation(List<List<Double>> determina

- C语言算法之打渔晒网问题

qiufeihu

c算法

如果一个渔夫从2011年1月1日开始每三天打一次渔,两天晒一次网,编程实现当输入2011年1月1日以后任意一天,输出该渔夫是在打渔还是在晒网。

代码如下:

#include <stdio.h>

int leap(int a) /*自定义函数leap()用来指定输入的年份是否为闰年*/

{

if((a%4 == 0 && a%100 != 0

- XML中DOCTYPE字段的解析

wyzuomumu

xml

DTD声明始终以!DOCTYPE开头,空一格后跟着文档根元素的名称,如果是内部DTD,则再空一格出现[],在中括号中是文档类型定义的内容. 而对于外部DTD,则又分为私有DTD与公共DTD,私有DTD使用SYSTEM表示,接着是外部DTD的URL. 而公共DTD则使用PUBLIC,接着是DTD公共名称,接着是DTD的URL.

私有DTD

<!DOCTYPErootSYST

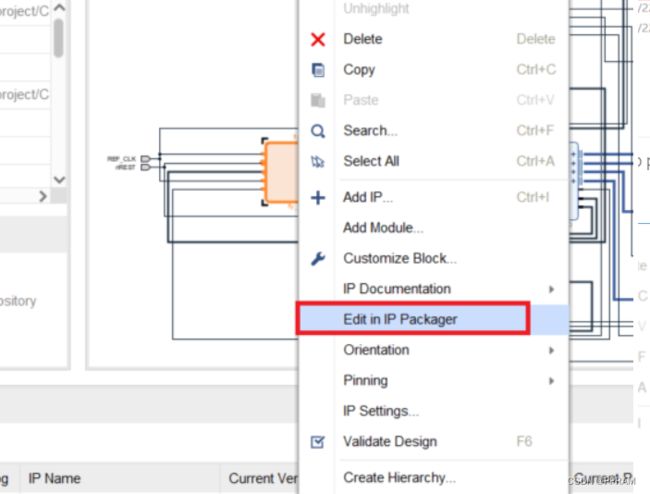

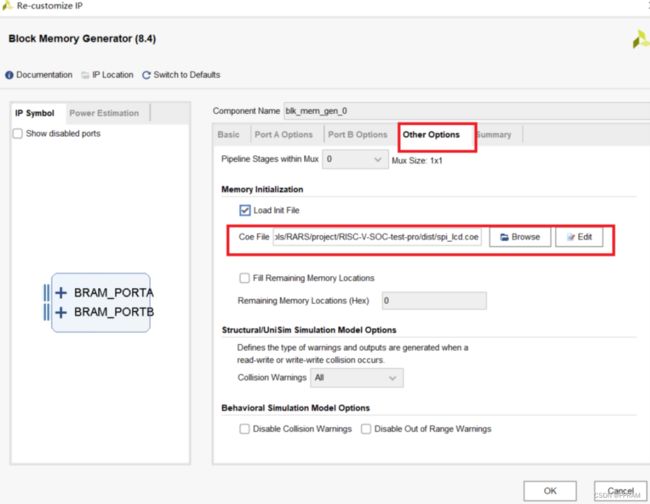

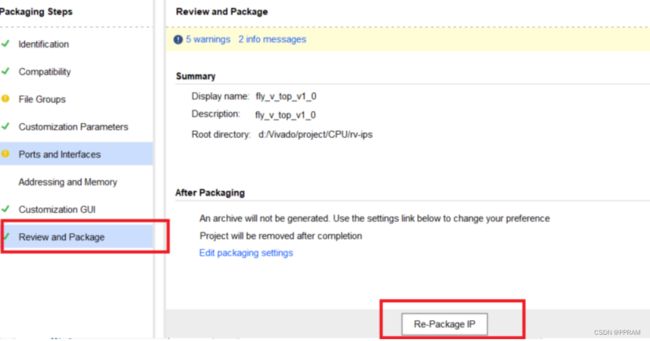

![]()

![]()

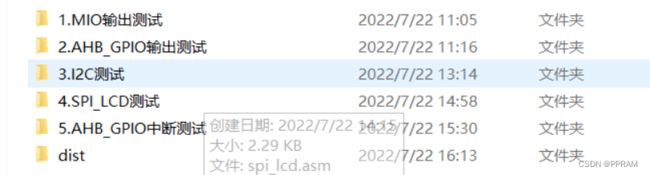

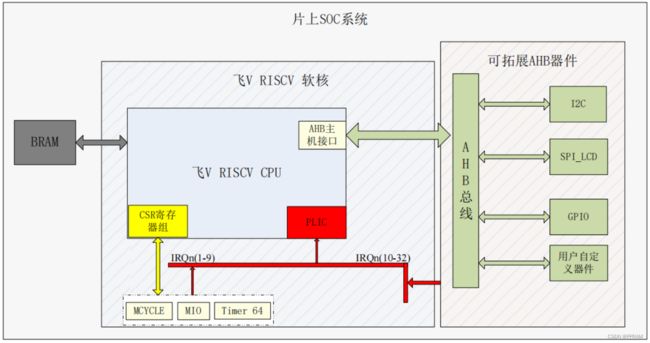

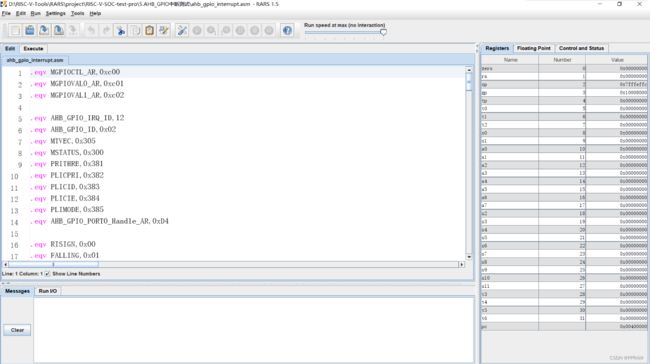

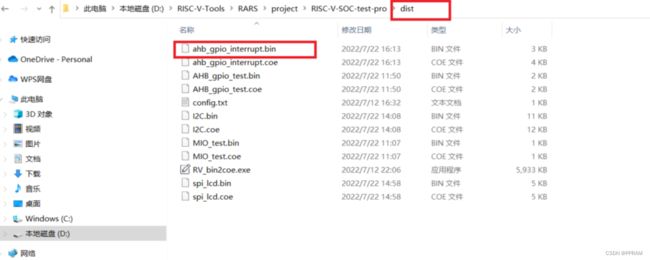

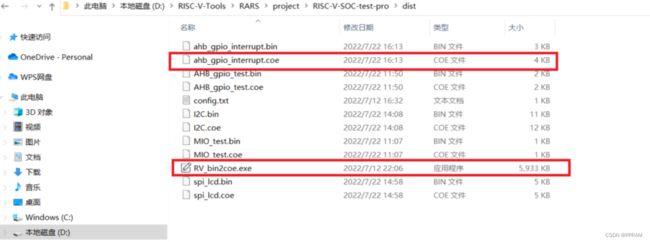

SOC测试例程

SOC测试例程

![]()

•软核部分

•软核部分![]()

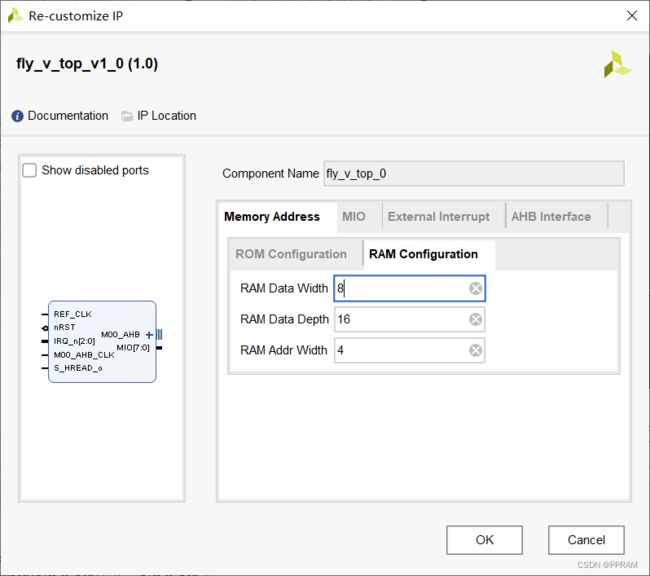

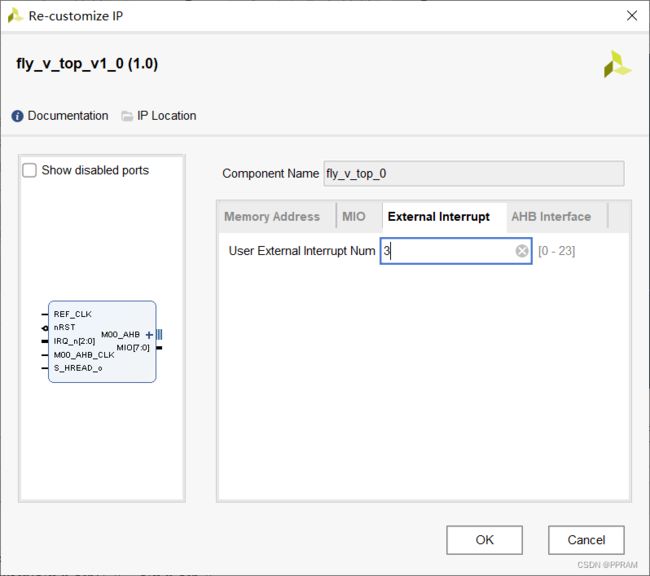

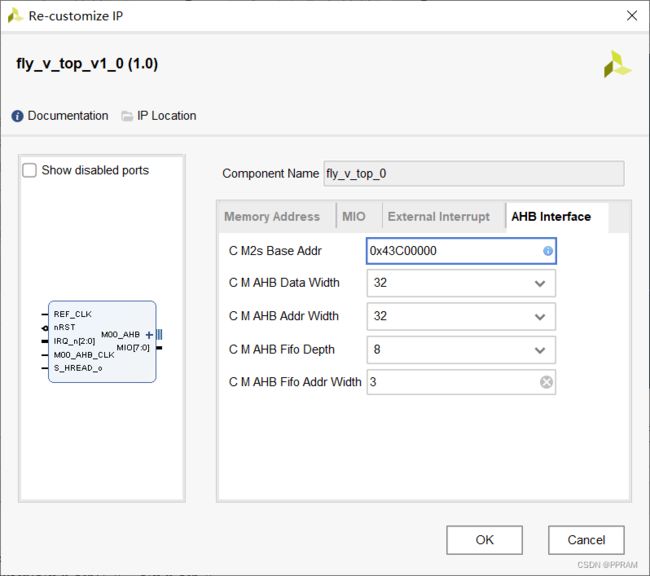

IP核参数设置中,memory address界面用于配置CPU的ROM与RAM。

IP核参数设置中,memory address界面用于配置CPU的ROM与RAM。