CMOS与TTL(上):PN结、MOS管、三极管

如果只看一个芯片的外观,是无法区分TTL和CMOS的。因为它们是按照芯片的制作工艺来分类的。

CMOS内部集成的是MOS管,而TTL内部集成的是三极管。

工作原理

P型半导体(空穴)

P型半导体是在纯净的硅晶体中掺杂了三价硼,此时硼原子最外层缺少了一个电子,我们用空穴代替这个缺少的电子。空穴吸引电子,对外显正电。我们称之为P型半导体。

P取自Positive的首字母,正的、积极的。

需要注意的是,P型半导体里面并不全是空穴,它里面也有自由电子的存在,但没有N型半导体里面那么多。

N型半导体(电子)

N型半导体是在纯净的硅晶体中掺杂了五价磷,此时磷原子多了一个自由电子,自由电子带负电,我们称之为N型半导体。

N取自Negative的首字母,负的、消极的。

如果我们给N型半导体通电,他是可以导通的,因为它内部有多余的自由电子,无论正接还是反接都可以导通。

漂移运动

上面叙述的两种半导体在外加电场的情况下,会作定向运动。这种运动称为电子与空穴(统称“载流子”)的“漂移运动”,并产生“漂移电流”。

根据静电学,电子将作与外加电场相反方向的运动,并产生电流(根据传统定义,电流的方向与电子运动方向相反,即和外加电场方向相同);而空穴的运动方向与外加电场相同,由于其可被看作是“正电荷”,将产生与电场方向相同的电流。

两种载流子的浓度越大,所产生的漂移电流越大。

扩散运动

由于某些外部条件而使半导体内部的载流子存在浓度梯度的时候,将产生扩散运动,即载流子由浓度高的位置向浓度低的位置运动。

pn结的形成

p型、n型半导体由于分别含有较高浓度的“空穴”和自由电子,存在浓度梯度,所以二者之间将产生扩散运动。即:

- 自由电子由n型半导体向p型半导体的方向扩散

- 空穴由p型半导体向n型半导体的方向扩散

载流子经过扩散的过程后,扩散的自由电子和空穴相互结合,使得原有的N型半导体的自由电子浓度减少,同时原有P型半导体的空穴浓度也减少。在两种半导体中间位置形成一个由N型半导体指向P型半导体的电场,称为“内电场”。

平衡状态(零偏置)

pn结在没有外加电压情况下,跨结形成了电势差导致了平衡状态。该电势差称为内建电势(built-in potential)。

pn结的n区的电子向p区扩散,留下了正电荷在n区。类似地,p型空穴从p区向n区扩散,留下了负电荷在p区。进入了p区的电子与空穴复合,进入了n区的空穴与电子复合。其效果是扩散到对方的多数载流子(自由电子与空穴)都耗尽了,结区只剩下不可移动的带电离子,失去了电中性变为带电,形成了耗尽层(space charge region)。

图A:零偏置热平衡下的pn结。电子与空穴的浓度分别用蓝线、红线表示。灰色区域是电中性。亮红色是正电区域,亮蓝色区域是负电性。底部显示电场。静电力作用于电子与空穴,以及其扩散取向。

耗尽区的电场与电子与空穴的扩散过程相反,阻碍进一步扩散。载流子浓度确定的平衡态在图A中表示为红线与蓝线。

图B:pn结在零偏置与热平衡状态下。底部绘出了电荷密度、电场、电压。

耗尽层的多数载流子已经全部耗尽,留下的电荷密度等于净掺杂水平。当平衡达到时,电荷密度近似显示为阶梯函数,耗尽层与中立区的边界相当陡峭。(见图B的Q(x)图)。耗尽层在pn结两侧有相同量的电荷,因此它向较少掺杂的一侧延展更远(图A与图B的n端)。

正向偏置

若施加在p区的电压高于n区的电压,称为正向偏置(forward bias)。

在正向偏置电压的外电场作用下,N区的电子与P区的空穴被推向pn结。这降低了耗尽区的耗尽宽度。这降低了pn结的电势差(即内在电场)。随着正向电压的增加,耗尽区最终变得足够薄以至于内电场不足以反作用抑制多数载流子跨pn结的扩散运动,因而降低了pn结的电阻。跨过pn结注入p区的电子将扩散到附近的电中性区。所以pn结附近的电中性区的少数载流子的扩散量确定了二极管的正向电流。

反向偏置

若施加在n区的电压高于p区的电压,这种状态称为pn结反向偏置(reverse bias)。

在半导体中,电子和空穴作为载流子。数目较多的载流子称为多数载流子;在N型半导体中多数载流子是电子,而在P型半导体中多数载流子是空穴。数目较少的载流子称为少数载流子;在N型半导体中少数载流子是空穴,而在P型半导体中少数载流子是电子。

由于p区连接电源负极,多数载流子(空穴)被外电场拉向负极,因而耗尽层变厚。n区也发生类似变化。并且随反向偏置电压的增加,耗尽层的厚度增加。从而,多数载流子扩散过pn结的势垒增大,pn结的电阻变大,宏观看二极管成为绝缘体。

反向偏置时形成极其微弱的漂移电流,电流由N区流向P区,并且这个电流不随反向电压的增大而变化,称为“反向饱和电流”(reverse saturation current)。这是因为反向电流是由少数载流子跨pn结形成的,因此其“饱和”值取决于少数载流子的掺杂密度。由于反向饱和电流很小,pn结处于截止状态,所以外加反向电压时,pn结相当于断路。

反向崩溃

当反向电压逐渐增大时,反向饱和电流不变。

但是当反向电压达到一定值时,pn结将被击穿。

在pn结中加反向电压,如果反向电压过大,位于pn结中的载流子会拥有很大的动能,足以和中性粒子碰撞使中性粒子分离出价电子而产生空穴-电子对。这样会导致pn结反向电流的急剧增大,发生pn接面的击穿,因为被弹出的价电子又可能和其他中性粒子碰撞产生链式反应,类似于雪崩,这样的反向击穿方式成为雪崩击穿(Avalanche breakdown)。掺杂浓度越低所需电场越强。当掺杂浓度非常高时,在pn结两端加入弱电场就会使中性粒子中的价电子脱离原子的束缚,从而成为载流子。导致pn结的击穿。这样的击穿被称作齐纳击穿(Zener breakdown)。掺杂浓度越高所需要的电场越弱。一般小于6V的电压引起的是齐纳击穿,大于6V的引起的是雪崩击穿。

伏安特性

pn结的最大特性为单向导电性,反映到伏安特性曲线如右图。当正向电压达到一定值时,pn结将产生正向偏置,pn结被导通(图中蓝色部分);当反向电压在一定范围内时,pn结产生微弱的反向饱和电流(图中绿色部分);当反向电压超过一定值时,pn结被击穿(图中黄色部分)。

三极管

NPN型双极性晶体管可以视为共用阳极的两个二极管接合在一起。在双极性晶体管的正常工作状态下,发射结(基极与发射极之间的PN结)处于正向偏置状态,而集电结(基极与集电极之间的PN结)则处于反向偏置状态。

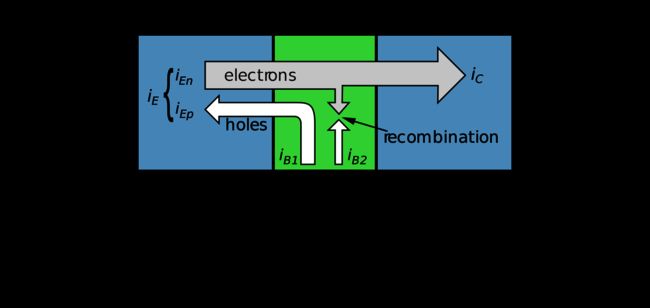

图中左边的蓝色区域为发射极,中间绿色区域为基极,右边蓝色区域为集电极。

灰色的箭头为电子的流动方向示意,发射极注入的大部分电子移动到了集电极,少部分在基极与空穴复合。白色箭头为基极的多数载流子空穴的流动方向示意。NPN型双极性晶体管处于正向放大区的条件是:在发射结上具有正向偏置,而集电结具有反向偏置。

可以把三极管转化成这样一个模型以便理解:

BE之间是一个二极管和一个电流表,CE之间是一个可调电阻和一个电流表,中间还有一个小人,小人时刻看着电流表1的读数,然后通过调节可调电阻的大小,保证电流表2的读数=电流表1的读数x放大倍率。

MOS管

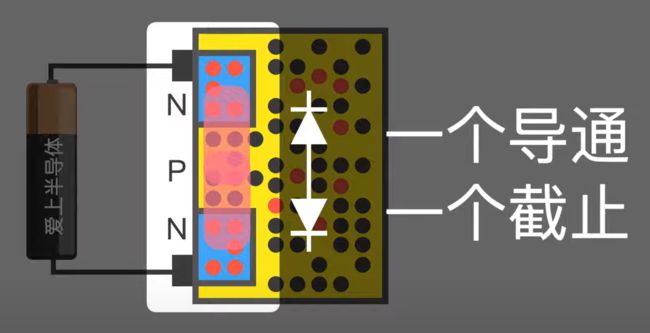

将两个N型半导体引出两个金属电极,分别作为mos管的漏极和源极,我们给他接上电,此时mos管是截止的。

因为他们之间形成了两个二极管,而且方向相反。此时mos管截止。

为了能让他导通,在P区加了很薄的二氧化硅绝缘层,然后又在绝缘层上面制作了一层金属板,形成了栅极。当我们给栅极也接上电,这时候金属板上就有了电场。就可以把P区里面的电子吸引到绝缘层附近,而把空穴赶走。电压越大,吸引过来的电子也越多。

当自由电子吸引的足够多时,就形成了N沟道,N沟道就是N型半导体之间的沟道。此时N沟道取代了原来P型半导体之间的空穴,使得原来半导体之间的PN结不复存在。

为了便于理解,我们可以把这个区域看作一整块N型半导体。

所以在栅极施加电压之后,它就导通了。当我们把栅极电压去掉,N沟道就消失了,此时mos管必然会截止。

mos管的两个特性:

- 栅极阻抗非常高

- 因为有绝缘层的存在,它几乎完全关闭了电子的通道,造成他的输入电阻可达上亿欧姆,所以它的输入几乎不取电流。这也是现在芯片内部集成的都是mos管的原因之一。

- mos的栅极容易被静电击穿

- 由于栅极阻抗非常大,感应电荷很难释放。产生的高压很容易就把这一层薄薄的绝缘层给击穿,造成mos管永久损坏。

NMOS

将NMOS的G极连接单片机的一个IO口,当单片机输出高电平时,等效于开关闭合。

NMOS等效模型

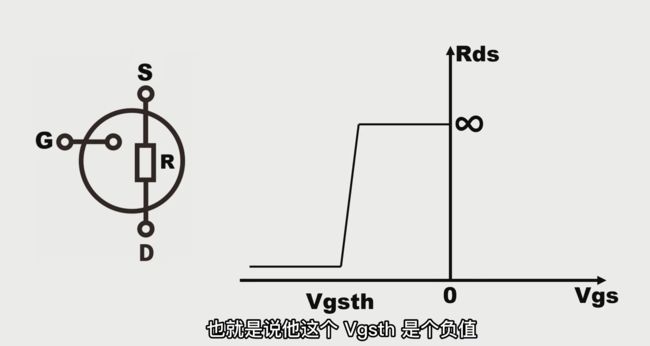

PMOS

PMOS的等效模型

PMOS的Vgsth是一个负值,Vsource要大于Vgata的时候,PMOS才能被打开,这与NMOS是正好相反的

PMOS与NMOS相反。

NMOS中G极高电平导通,PMOS中G极低电平导通。

NMOS放到灯泡下面,PMOS放到灯泡上面(高电平的一端)。

NMOS中D极在上,S在下,PMOS中S极在上,D极在下。

对于灯泡、电机这种无源功率器件,我们可以利用NMOS作为下管控制,对于芯片这种有源器件,一般利用PMOS作为上管控制更加合适。

如果NMOS接在上面

那么当NMOS打开的时候,DS之间的电阻就接近于0,那么S的电压就是5V。此时如果还要维持NMOS的打开状态,Gata的电压必须要大于Vsource+Vgsth,差不多就是10V左右,而系统里最高的电压就是5V,显然无法继续维持NMOS的打开状态。那么此时NMOS就是陷入一个不确定的状态。这就是为什么NMOS不能放在上面的原因。

对于灯泡来说,放在上面和放在下面有没有区别

对于灯泡来说,放到上面和放到下面确实没有什么本质的区别。

但是如果把灯泡换成芯片,那就有区别了。

如果MOS管在下面,我们可以看到这个芯片的负极,也就是GND它没有直接接地。GND和地之间隔了一个MOS管,这样在NMOS打开的时候,这个芯片就没办法跟其他的芯片良好地共地,可能会有一个通信混乱的问题。同时在NMOS关闭的时候,又因为芯片的VCC一直连着电源,电流就有可能直接通过io口流出去。这样可能让芯片进入一个未知的状态。所以使用芯片的话,使用PMOS作为上管,把芯片放在下面就比较合适了,这样子既可以使芯片的GND良好地接地,就可以完全掐断VCC的电源

能不能利用PMOS作为上管来控制灯泡?

因为刚才有说到,对于灯泡来说,放到上面和放到下面确实没有什么本质的区别。

因为工艺的问题:

| Rdson | NMOS |

|---|---|

| 价格 | NMOS |

| 品种 | NMOS>PMOS |

出于成本和易用性的考虑,能用NMOS还是尽量用NMOS

三极管与MOS管区别

MOS管是电压控制的元件,而三极管是电流控制的元件。

| 三极管 | NMOS管 |

|---|---|

|

|

三极管的BE之间可以理解为存在一个二极管,这也就产生了一个电流的通路。当给三极管施加高电平时,BE之间就会产生持续的电流,只有存在这个持续的电流时,三极管才会被打开。当把这个高电平拿走,电流就瞬间消失了,三极管也会被关闭。维持三极管打开的必要条件就是BE之间存在持续的电流。所以三极管被称为电流控制元件。

对于MOS管来说,G跟S之间是不存在通路的,它们之间仅仅存在一个寄生电容,当给Gata施加高电平时,除了一开始给这个寄生电容充电的电流之外,并不存在其他的电流。只要维持GS的电压差,MOS管就可以打开。甚至因为这个寄生电容的存在,即便撤走了IO的高电平,你会发现灯泡依旧是亮的,直到这个电容上的电荷慢慢放光,MOS管才会关闭。

到这里,应该能发现MOS管的优势:省电。保持MOS管的打开状态并不需要额外的电流,而三极管需要。

MOS管的第二个优势是导通阻抗小(还是省电)。MOS管导通之后,DS之间可以等效为一个电阻,而且这个电阻可以很轻松地做到小于10mΩ。此时即便通过10A的电流,也就只会产生0.1V的压降以及1W的功耗。二三极管导通之后,CE之间就等效为一个二极管,就会产生一个固定的0.4V左右的压降,此时如果通过的电流还是10A。那么三极管的功耗就达到了4W。所以现在大部分的低压功率器件都使用了MOS管做控制。