【开源硬件篇】STM32F103C8T6核心板

STM32F103C8T6核心板

文章目录

-

- STM32F103C8T6核心板

-

- 一、STM32F103C8T6芯片

-

- 1.1 STM32F103C8T6简介

- 1.2 芯片引脚说明

- 二、去耦电路

-

- 2.1 原理图设计

- 2.2 原理分析

-

- 2.2.1 结论

- 2.2.2 去耦效果图

- 2.2.3 放置距离问题

- 2.2.3 放置位置问题

- 2.3 PCB设计示例

- 三、晶振电路

-

- 3.1 原理图设计

- 3.2 原理分析

- 3.3 PCB设计示例

- 四、SWD下载电路

-

- 4.1 原理图设计

- 4.2 原理讲解

-

- 4.2.1 JTAG介绍

- 4.2.2 SWD模式

- 4.2.3 SWCLK为什么需要经过10K电阻下拉至GND?SWDIO为什么需要经过10K电阻上拉至3.3V?

- 4.3 PCB设计参考示例

- 五、电源指示电路

-

- 5.1 原理图设计

- 5.2 原理讲解

- 5.3 PCB设计参考示例

- 六、复位电路设计

-

- 6.1 原理图设计

- 6.2原理讲解

- 6.3 PCB设计参考示例

- 七、BOOT电路设计

-

- 7.1 原理图设计

- 7.2 原理分析

- 7.3 PCB设计参考示例

- 八、外围IO口电路设计

-

- 8.1 原理图设计

- 8.2 PCB设计参考示例

一、STM32F103C8T6芯片

1.1 STM32F103C8T6简介

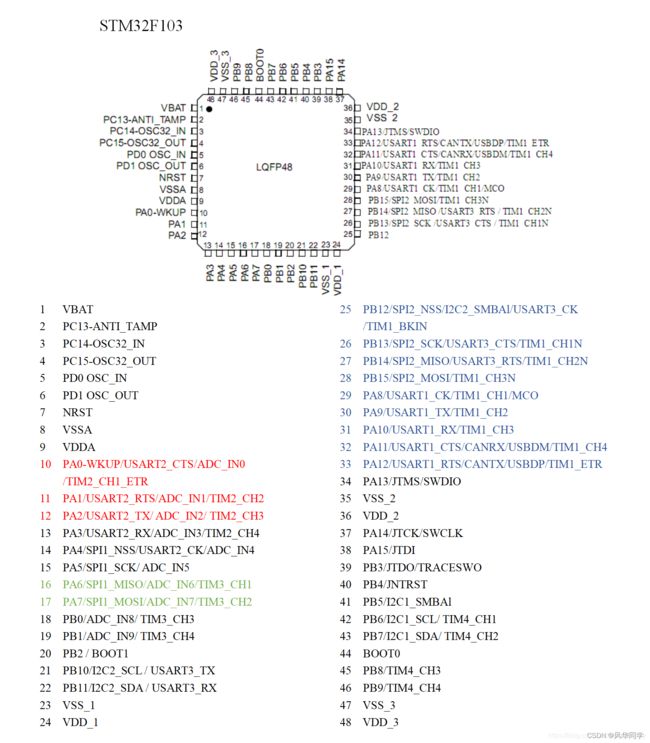

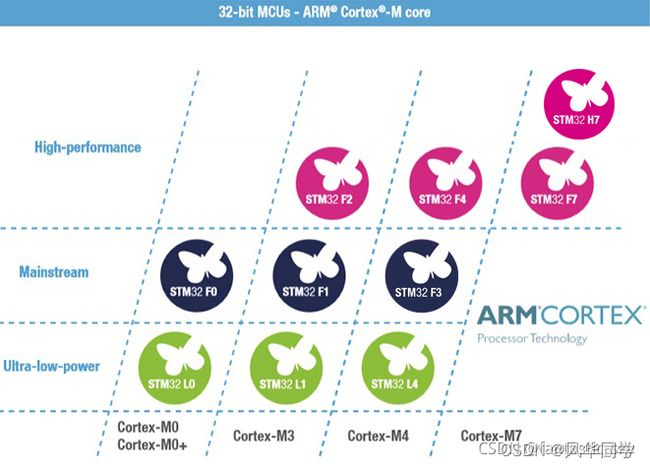

STM32F103C8T6是一款由意法半导体公司(ST)推出的基于Cortex-M3内核的32位微控制器,硬件采用LQFP48封装。

具体参数为:

- 64K x 8bit的Flash

- 20K x 8bit的SRAM

- 37个GPIO,分别为PA0-PA15、PB0-PB15、PC13-PC15、PD0-PD1

- 2个12bit ADC合计12路通道,外部通道:PA0到PA7以及PB0到PB1。内部通道:温度传感器通道ADC_Channel_16和内部参考电压通道ADC_Channel_17

- 4个16bit定时器/计数器,分别为TIM1、TIM2、TIM3、TIM4

- 2个看门狗定时器(独立看门狗IWDG、窗口看门狗WWDG)

- 1个24bit向下计数的滴答定时器systick

- 2个IIC,2个SPI,3个USART,1个CAN

- 内部8MHz时钟HSI最高可倍频到64MHz,外部8MHz时钟HSE最高可倍频到72MHz

Cortex-M3是ARM公司推出的基于ARMv7架构的MCU内核,ST公司在此内核的基础上完成了USART、DMA、GPIO等外围电路的设计。

ST系列家族:

相同系列的内核一般相同,如F1系列都采用Cortex-M3内核开发,但根据Flash大小不同可将STM32分成小容量产品(<64K)、中等容量产品(介于64K-128K)、大容量产品3个部分

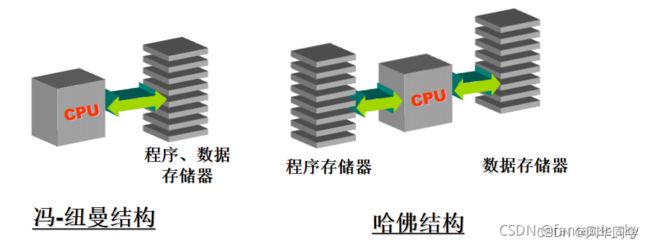

Cortex-M3摒弃了冯· 诺依曼结构(普林斯顿结构),采用了将指令存储和数据存储分开的 的哈佛结构(Harvard Architecture ),这样一来Cortex-M3同时拥有了独立的32-bit指令总线和32-bit数据总线,数据访问将不再占用指令总线,同时读取指令和数据后提升了MCU运行速度。

Cortex-M3是一个 32 位处理器内核,正因如此,STM32才被称作为32-bit微控制器,他拥有32条地址总线,也就是说最大寻址空间为4Gbyte。此外,Cortex-M3的寄存器是32 位的,存储器接口也是 32 位的

1.2 芯片引脚说明

二、去耦电路

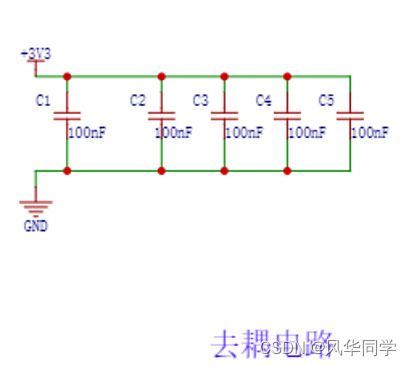

2.1 原理图设计

2.2 原理分析

2.2.1 结论

-

在电源管脚上放置一个104(0.1μF)的电容能够有效抑制电源上的噪声,也就是能够对电源噪声去耦;

-

“电源 – 去耦电容 – 地”三点一线的距离越近,则去耦的效果越好

-

相同材料的电容,即便电容容量减少为1/10,去耦的效果并不会有什么明显变化,我们对于高频去耦用同样封装的器件,容值为0.01μF、0.1μF、1μF效果相差不大

-

同样容值,贴片(SMD)封装的电容比穿孔的电容效果更好,原因就是穿孔电容的管脚等效的电感要大很多,影响了去耦的效果;

2.2.2 去耦效果图

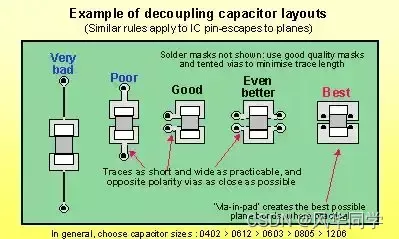

2.2.3 放置距离问题

-

容值最小的电容,有最高的谐振频率,去耦半径最小,因此放在最靠近芯片的位置。

-

容值稍大些的可以距离稍远,最外层放置容值最大的。但是,所有对该芯片去耦的电容都尽量靠近芯片

2.2.3 放置位置问题

针对于高速的PCB设计时,电容最好是放置在芯片的同一侧,去耦的效果更好;而如果是MCU类型的去耦电容,那么放置背面和正面的区别不大。

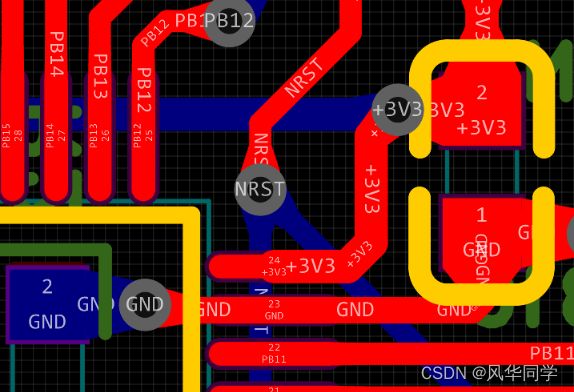

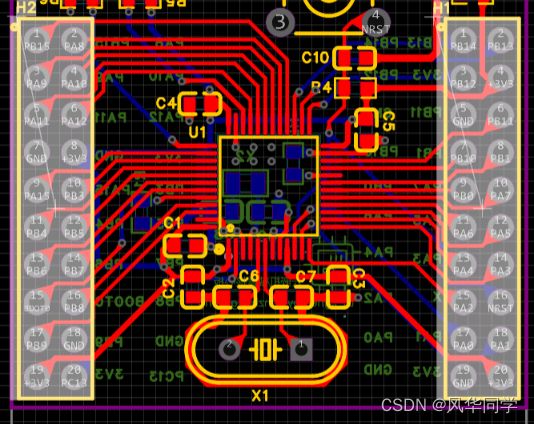

2.3 PCB设计示例

三、晶振电路

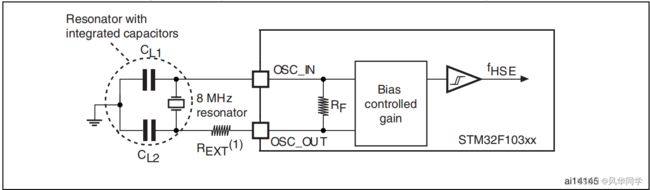

3.1 原理图设计

晶振的选择:

可知:

CL = CL1 x CL2 / (CL1 + CL2) + Cstray

Cstray的值为2pf~7pf的范围

我们这里选择的是16pf的CL

然后我们一般设置CL1 = CL2,而选择Cstray为5pf

之后根据计算可得,CL1 = CL2 = 22pf,所以我们8MHZ晶振的匹配电容就选择为22pf

而对于32.768KHZ的外部晶振而言,根据STM32芯片数据手册中关于外部低速晶振的描述,强烈建议使用具有负载电容CL <= 7 pF的谐振器。切勿使用负载电容为12.5 pF的谐振器。

因此我们选择CL = 6pF,Cstray=2pf,所以选择CL1 = CL2 = 8pF

3.2 原理分析

STM32内部自身就有三个时钟源,这个看过32手册时钟树的都会有一定的了解,在32芯片的时钟树中需要有五个时钟源,我们PCB需要放置的便是外部高速时钟和外部低速时钟。

高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为4MHz~16MHz。一般设置的为8MHZ的晶振,用于系统的主频使用

低速外部时钟,接频率为32.768kHz的石英晶体,用于驱动RTC时钟

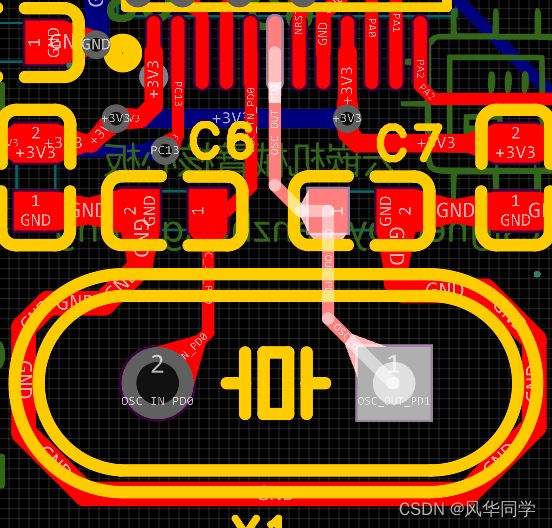

3.3 PCB设计示例

我们可以注意到,晶振旁边使用GND布线包围,最好也在围绕的GND线上打孔,这是为了将晶振隔离开。而且晶振所在区域的顶层以及底层最好不要走线,因为这会影响到信号线的信号。

四、SWD下载电路

4.1 原理图设计

4.2 原理讲解

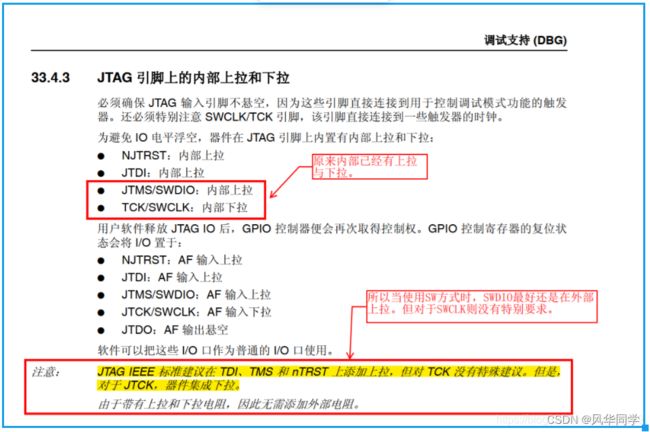

4.2.1 JTAG介绍

我们比较常用的是Jlink下载器 ,这种下载器有一个缺点就是使用的Jtag 20PIN接口,太多的PIN会导致一些小型的PCB板很拥挤,也会增加布线的难度。 而使用SWD接口下载调试,只需要要使用4个PIN: GND, RST, SWDIO, SWDCLK ,而且下载速度可以达到10M/s,优势显而易见。

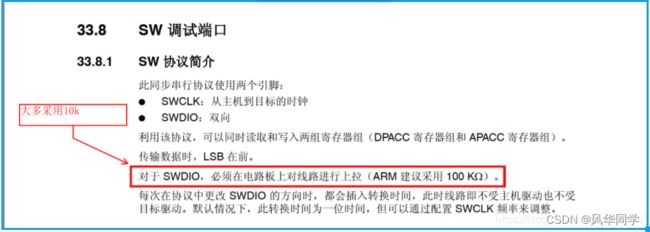

4.2.2 SWD模式

SWD 模式比 JTAG 在高速模式下面更加可靠。 在大数据量的情况下面 JTAG 下载程序会失败, 但是SWD 发生的几率会小很多。基本使用 JTAG 仿真模式的情况下是可以直接使用 SWD 模式的, 只要你的仿真器支持。

4.2.3 SWCLK为什么需要经过10K电阻下拉至GND?SWDIO为什么需要经过10K电阻上拉至3.3V?

SWDIO,在芯片内部已经有上拉,但在电路板上必须再一次上拉(100k或者10k电阻)

SWCLK,在芯片内部已经有下拉,在电路板上没有特殊要求进一步下拉。

4.3 PCB设计参考示例

这里我们的电阻应该尽量靠近我们的SWD下载口,以便更好实现上下拉效果

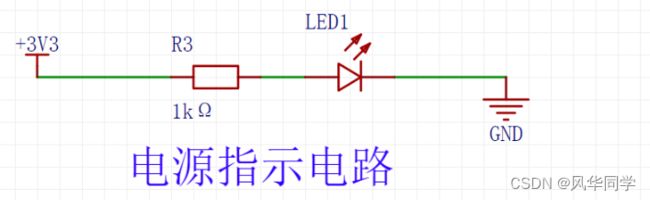

五、电源指示电路

5.1 原理图设计

5.2 原理讲解

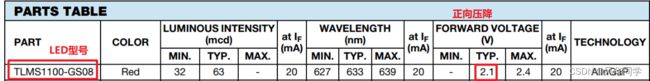

LED为发光二极管,正向导通,具有正向压降,这里要根据数据手册去查看LED灯的正向压降。比如我选择了以下的LED灯(立创商城的物料编号为:C511086):

由数据手册可知,其正向压降的最大值为2.4V,典型值为2.1V,所以当LED正常工作时,LED灯的压降最大为2.4V,此时R3的分压为0.9V.

一般来说,电流为3mA~10mA时LED灯正常点亮,最大额定的电流为20mA,在额定电流内,流过LED灯的电流越大,LED灯越亮。

这里我们选择I = 10mA,故R3 = U / I = 0.9V / 10mA = 90R。考虑到我们物料一般100R的电阻比较多,所以可以选择100R的电阻代替。

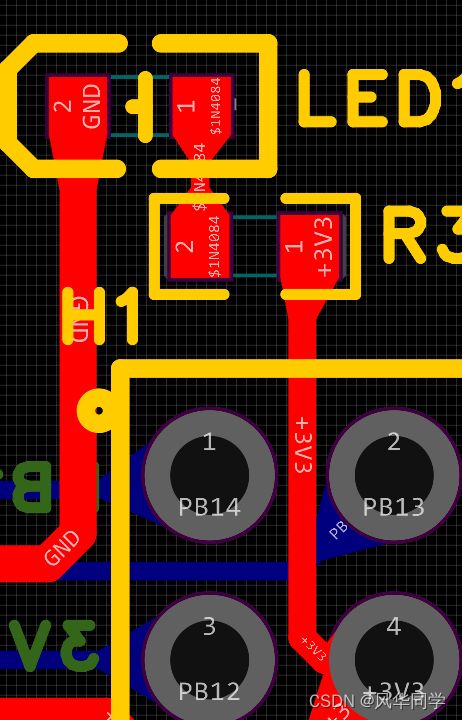

5.3 PCB设计参考示例

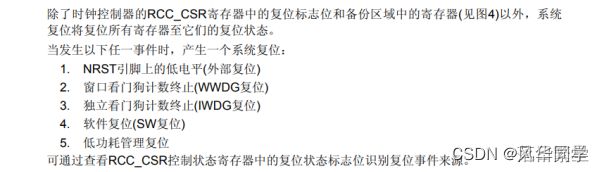

六、复位电路设计

6.1 原理图设计

6.2原理讲解

当NRST引脚被拉低时,会产生复位信号,我们可以通过这个对我们的单片机进行复位操作。

在电路图中:

-

当单片机重新上电的时候,此时电容C14充电导通,RESET的电压为低电平,进行系统复位,,一段时间后,电容C9充电完成断开,RESET的电压为高电平,单片机保持稳定,不会复位

-

当按键按下时,按键会保持20~50ms的导通,nRST与地端导通,此时电压为低电平,进行系统复位。

6.3 PCB设计参考示例

这里我们滤波电容尽量靠近我们的元器件,能够很好地消除按键按下的时候的电压抖动,保证芯片复位的准确性。

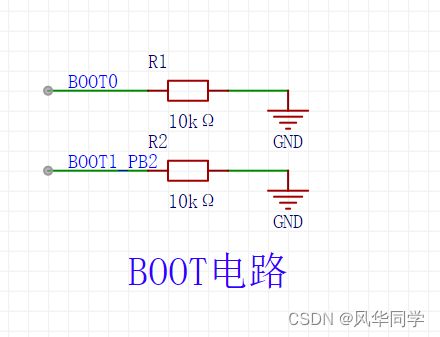

七、BOOT电路设计

7.1 原理图设计

7.2 原理分析

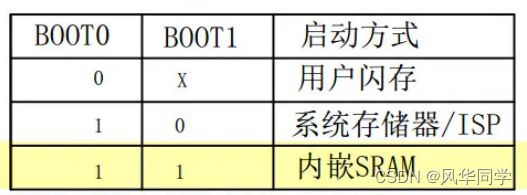

STM32的BOOT0和BOOT1控制的是芯片的启动方式,其支持内部FLASH启动、系统存储器启动、内部SRAM启动。

- 用户闪存 = 芯片内置的Flash。

- SRAM = 芯片内置的RAM区,就是内存

- 系统存储器 = 芯片内部一块特定的区域,芯片出厂时在这个区域预置了一段Bootloader,就是通常说的ISP程序。这个区域的内容在芯片出厂后没有人能够修改或擦除,即它是一个ROM区,它是使用USART1作为通信口

一般使用JTAG或者SWD调试下载程序,会下载到闪存里,所以可以直接将BOOT0引脚和BOOT1引脚置为低电平。

接10K的原因是因为BOOT0和BOOT1在没有接任何外设的情况下处于高阻态的状态,通过10K的上下拉电阻可以起到一个很好的限流作用,同时可以保护内部的IC芯片

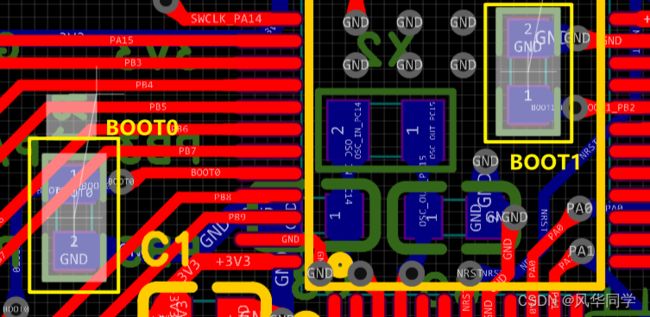

7.3 PCB设计参考示例

这里我们将BOOT0和BOOT1的下拉电阻放置到PCB的背面,这样就可以避免干扰我们的走线。

八、外围IO口电路设计

8.1 原理图设计

我们一般使用排针将未使用的引脚引出。推荐大家使用双排针,尽量少使用单排针,这样稳定性会更强一点,可以避免拔插排针的时候出现弯曲的情况。

同时,建议把BOOT0引出来,这样便于后面设计ISP一键下载电路,这样就可以通过使用一根USB数据线就可以下载程序。

最后的话,建议至少引出两组3V3和GND,即每一边的排针都有一组电源,便于我们PCB的布线

8.2 PCB设计参考示例

引脚的外围排针尽量放置在板子的两侧外围,避免干扰我们芯片周围元器件的摆放

上述的原理图以及PCB设计已经开源至立创开源平台上,大家可以下载进行参考设计专属自己的STM32F103C8T6最小系统板,链接为:https://oshwhub.com/panzhongsheng/bi-she-STM32F103C8T6hu-xin-ban

如果觉得写的还不错的话,麻烦大家点赞收藏加关注哦,你们的支持是我创作的动力,下一期会开源STM32F103C8T6系统板,希望大家持续关注哦!!