Integrated LogicAnalyzer v6.2 (Vivado ILA使用方法)

Chapter 1 Overview

1.1 Feature Summary(功能摘要)

FPGA设计中的信号连接到ILA核时钟和探针输入(图1-1)。这些连接到探针输入的信号以设计速度进行采样,并使用片上块RAM(BRAM)进行存储。核参数指定每个探针输入的探针数量、跟踪样本深度和宽度。与ILA核的通信是使用连接到FPGA的JTAG接口的自动实例化调试核集线器进行的。

图1-1:ILA核符号

注:从probe3到prob1022的数值范围在图1-1中用椭圆(…)表示。

将设计加载到FPGA后,使用Vivado®逻辑分析仪软件设置ILA测量的触发事件。触发发生后,样本缓冲区被填充并上传到Vivado逻辑分析器中。您可以使用波形窗口查看此数据。

常规FPGA逻辑用于实现探针采样和触发功能。片上块RAM存储器存储数据,直到软件上传为止。无需用户输入或输出即可触发事件、捕获数据或与ILA心通信。

1.1.1ILA Probe Trigger Comparator(ILA探针触发比较器)

每个探针输入连接到能够执行各种操作的触发比较器。在运行时,比较器可以设置为执行=或!=比较。这包括匹配级别模式,例如X0XX101。它还包括检测边沿转变,例如上升沿(R)、下降沿(F)、任一边沿(B)或无转变(N)。触发比较器可以执行更复杂的比较,包括>、<、≥和≤。

重要事项:比较器是在运行时通过Vivado逻辑分析器设置的。

1.1.2 ILA Trigger Condition(ILA触发条件)

触发条件是对每个ILA探针触发比较器结果进行布尔“与”或“或”计算的结果。使用Vivado逻辑分析器,您可以选择是“与”探测触发比较器探测还是“或”它们。当满足所有ILA探测比较时,“与”设置会引发触发事件。当满足任何ILA探测比较时,“OR”设置会引发触发事件。触发条件是用于ILA跟踪测量的触发事件。

1.2 Applications(应用)

ILA核心设计用于任何需要使用Vivado逻辑分析仪进行验证或调试的应用程序。

1、单击 IP Catalog

2、在Search(搜索框)中搜索:ILA

3、在Debug下面选择->ILA(Integrated Logic Analysis)->双击

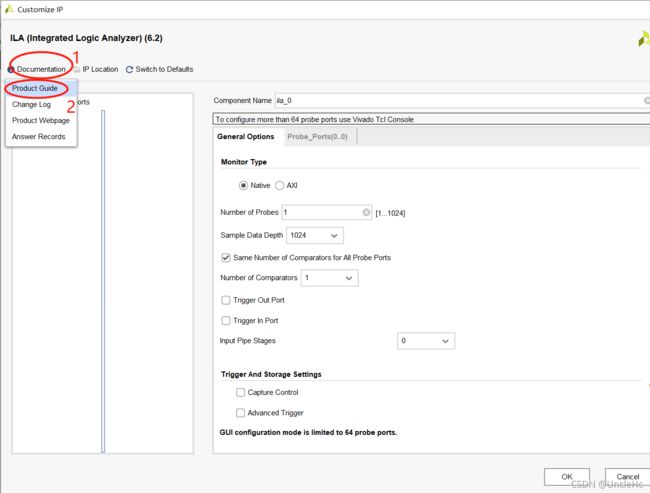

1、单击Documentation

2、在下拉选项中选择Product Guide->单击

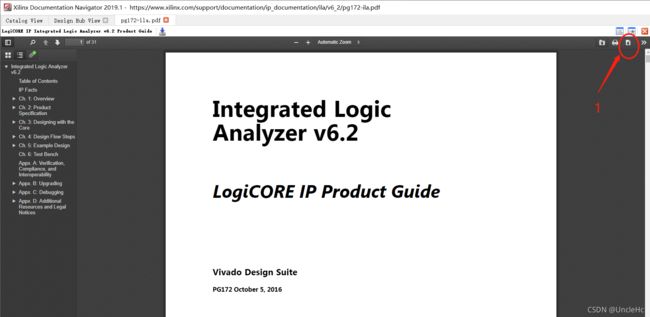

单击Product Guide 之后,会自动跳转到官方IP文档,我们可以直接阅读,也可以下载保存。

1、单击下载按钮,可以将IP文档下载下来。

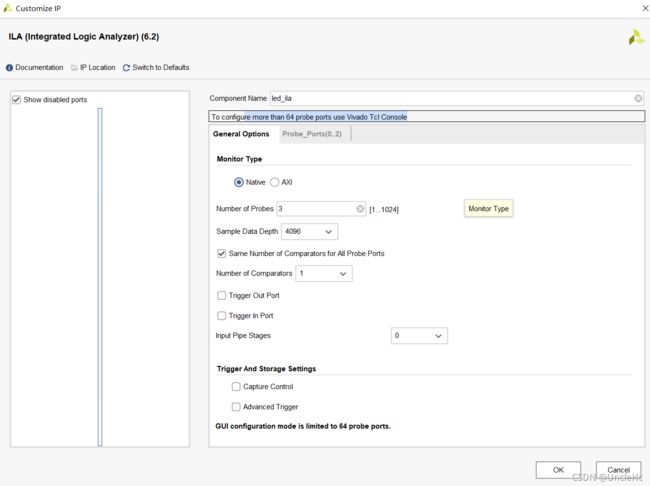

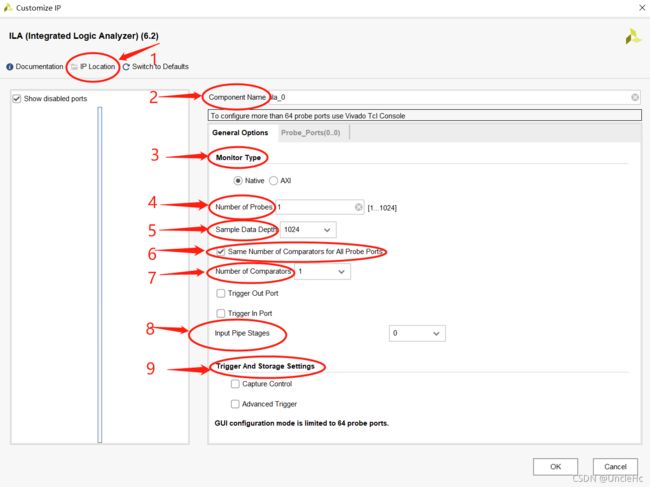

2.3、ILA 界面简介

2.3.1、General Options 界面

1、IP Location->单击之后,可以看见创建IP 存储的位置。

2、Component Name->ILA IP的名称,在这里可以使用默认名称,也可以根据自己的风格进行更改。我在这里把这个IP 更改成led_ila。

3、Monitor Type ->这个选项指定调试那种类型的接口。两种选择“Native”和“AXI”。对于初学者而言,这里选择“Native”就可以了。

4、Number of Probes->探针的数量。我们可以把这个理解成示波器的探头,1就对应1个探头,2就对应2个探头…以此类推。这里提供的选择范围在[1,1024]。在实际使用的过程中,我们根据需要观测信号的数量来合理选择探头的数量。在这里,我选择3个探头。

5、Sample Data Depth->采样数据的深度,可以在右边下拉菜单中选择合适的深度。你就把这个理解为容量相同的储物格。储物格越多,存储的物品也就越多,对应到数据上来说,就意味着你能接收并且看到更多的数据。因为我FPGA资源剩余比较多,这里我选择4096。

6、Same No. of Comparators for all Probes ->选中为所有已启用的端口和接口启用相同数量的比较器。 此 IP 版本允许您在基本和高级触发模式下使用此选项。 这里选择默认配置就可以了。

7、No. of Comparators ->比较器数量。选择以启用适用于所有已启用探针的比较器数量。

Trigger Out Port -> 触发输出端口 – 选中以启用可选的触发输出端口。

Trigger In Port – >选中以启用可选的触发器输入端口。

8、Input Pipe Stages-> 选择要为探针添加的寄存器数量。 此参数适用于所有探头。选择默认配置就可以了。

9、

torage Qualification – 选中以启用跟踪捕获的限定符。

Advanced Trigger 高级触发——选中以启用基于状态机的触发排序。

ILA 参数配置之后的界面下图所示

1、Probe Width->探针的位宽。这里设置的探针位宽尽量和你观测的信号位宽保持一致。我这边观测三个信号,分别是sys_rst_n, led,cnt->对应的位宽分别为1,、1、32。

2、Number of Comparators->比较器的数量,这里不能被更改(前一个界面已经设置过了)。

3、Probe Trigger or Data-> 这里保持默认配置就可以。

设置之后->单击ok,ILA IP 配置完成。