【ARM AMBA AXI 入门 1 - AXI 握手协议】

文章目录

-

- 1.1 AXI 双向握手机制简介

-

- 1.1.1 信号列表

- 1.1.2 双向握手目的

- 1.1.3 握手过程

- 1.2 数据通路的握手要求

-

- 1.2.1 读数据通路

- 1.2.2 读地址通路

- 1.2.3 写数据通路

- 1.2.4 写地址通路

- 1.2.5 写回复通路

- 1.2.6 全信号

- 1.3 不同数据通路间的约束关系

-

- 1.3.1 读操作约束关系

- 1.3.2 写操作约束关系(AXI3.0版)

- 1.3.3 写操作约束关系(AXI4.0版)

1.1 AXI 双向握手机制简介

AXI 标准协议有五路独立的数据通道,这些通道都只支持单向传输,五路通道分别为:

- 读地址通道:主机在读地址通道上写入想要读取的数据的地址以及控制信息;

- 读数据通道:从机在接收到地址后,将该地址上的数据通过读数据通道发送给主机;

- 写地址通道:主机在写地址通道上写地址和控制信息;在写地址操作结束之后,即主机确保从机已经获得了此次传输的地址和控制信息后,才开始在写数据通道上写数据;

- 写数据通道;

- 写回复通道:从机在写回复通道上,将此次写传输的状态回复给主机。

每一路数据通道都遵循双向握手机制,即使用 VALID 和 READY 信号作为控制信号来传输数据,只有 VALID 与 READY 同时为高的时候,才可以正常的发送数据,而通常情况下:

- VALID 信号用来表示什么时候 “地址、数据、和 控制信号” 是有效的;主设备置高 VALID 信号表示主设备已经将数据,地址或者控制信息放到的写总线上,并保持。

- READY 信号则用来表示什么时候从设备准备好采集数据了; 从设备置高 READY 信号表示从设备已经做好接收的准备。

主设备可以通过 VALID 信号置起来控制发送速度的同时,从设备也可以通过 READY 信号的置起与否控制接收速度,反压主设备的发送速度。

当双方的信息同时为高,时钟上升沿到达后,一次数据传输完成,在 1 到 N 次时钟上升沿后,双方传完了要传的信息后,两信号同时拉低。

1.1.1 信号列表

AXI 标准协议中,双向握手信号共10个,无论是主设备还是从设备,这10个信号都对应于5个输入信号,5个输出信号。

| 数据通路 | 握手信号对 |

|---|---|

| 写地址通路 | AWVALID, AWREADY |

| 写数据通路 | WVALID, WREADY |

| 写回复通路 | BVALID, BREADY |

| 读地址通路 | ARVALID, ARREADY |

| 读数据通路 | RVALID, RREADY |

1.1.2 双向握手目的

握手:目的是控制数据在总线上的流动和采样;

双向:目的是主设备和从设备都可以控制总线数据流动。于AXI总线 而言,无论是主设备还是从设备,都可以控制数据的传输。

1.1.3 握手过程

握手的三种情况:

-

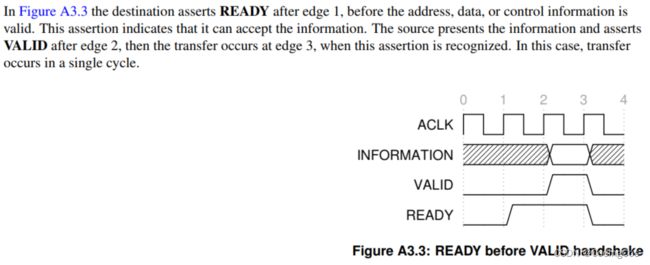

READY 信号先于 VALID 信号改变:这种情况下,如果我们将目光对向主设备,会发现,从设备在主设备发送数据前就做好了接受的准备,当主设备VALID后,时钟上升沿就完成了数据的传输;READY 信号与 VALID 不同,接收方在置起 READY 之后发现:其实我好像还挺忙,然后拉低 READY 信号。只要此时 VALID 信号没有置起,这种操作是完全可以。

-

READY 信号晚于 VALID 信号改变:VALID信号先拉高,表明数据正确,再往后READY拉高,表明可以进行采样。

协议规定:“VALID信号一旦拉高,除非READY信号拉高接收数据完成,不会主动变低”,

1.2 数据通路的握手要求

以下的叙述包含两个前提:

- 默认READY和VALID信号为低,有效时为高;

- 叙述中VALID等待READY的表达,实际的意思为在VALID拉高后的时钟上升沿,检测READY是否为高,若为高,完成握手,并不代表VALID与READY的拉高顺序。

1.2.1 读数据通路

在一个 Burst 读传输操作时,从设备在数据有效时置高 RVALID,一旦置高,RVALID 需要等待 RREADY 信号拉高,完成握手,进行数据传输。读数据通道上包括从机发送给主机的读数据以及读操作完成状态回复,数据的宽度可以是 8,16,64,128,256,512 或者是 1024bits。

1.2.2 读地址通路

主设备在地址信号和控制信号有效时置高 ARVALID,一旦置高,需要等待从设备的ARREADY信号置高,完成握手,进行数据传输。虽然名字为读地址通道,但实际上仍由主机写入地址,只不过是写入要读取数据的地址。

1.2.3 写数据通路

在 Burst 写传输时,主设备在写数据有效时置高 WVALID 信号,拉高后 WREADY 等待 WREADY 信号拉高,完成握手。一般来说,写数据都发生在写地址操作之后,但也不是绝对的,在有些情况下,可以先写数据。但是,所有情况下,写回复必然是在写数据之后,是对此次写数据的状态回复。

写通道有一点读通道所不具有的特性是有 STROBE 信号,用于标识写数据中有效的传输字节,即有些无效的数据,出于减少主机工作量的目的,或者在读写宽度不对称时,被放到写数据通道上和有效数据一起发送。而 STROBE 的信号的作用就是标识出这些无用的数据,告知从机不需要接收无用数据。

1.2.4 写地址通路

主设备在地址信息与控制信息有效时,拉高 AWVALID,拉高后 AWVALID 等待从设备拉高 AWREADY,完成握手,进行数据传输。

1.2.5 写回复通路

用于从机将写完成情况回复给主机。所有的写传输操作都需要在写回复通道上接收此次写传输操作的完成情况。值得注意的是写回复是针对一次突发传输的,而不是针对每一次的写数据操作的。(一次突发传输包括了多次写操作)。

1.2.6 全信号

AXI 总线中有两个全局信号:

ACLK,全局的时钟信号,所有的传输操作都发生在ACLK的上升沿;ARESETn,全局复位信号,低电平有效。

1.3 不同数据通路间的约束关系

在前文中,我们延伸出通道内的约束关系如下

VALID信号一旦拉高,除非READY信号拉高接收数据完成,不会主动变低

不同数据通路之间,同样的存在约束关系,这很好理解:写回复通路的信号传递一定晚于写数据通路,这就天然的构建起不同通路的先后顺序关系,假如不满足这种约束关系,AXI 协议就可能会发生死锁,即 deadlock 没有办法正确工作。

同时一个AXI slave 按功能进行区分的行为建模,无非是读与写两种操作,读操作与写操作的约束关系同样不同。

1.3.1 读操作约束关系

首先我们讨论的是读操作约束关系:

RVALID 和 RREADY 对应读数据通路的信号;

ARVALID 和 ARREADY对应读地址通路的信号;

读操作固定的约束关系为:数据通道必须要等待地址通道的数据传输完成才可以尝试握手操作。

1.3.2 写操作约束关系(AXI3.0版)

其次我们讨论的是写操作的约束关系

这里涉及到了三个数据通路,来考虑约束关系,唯一的一个硬约束关系为,BVALID需要等到写数据通路完成握手后才能置高。

初学者在这里往往会感到迷惑

比如说 BREADY 跟 WVALD 与 WREADY间有无关系?

BVALID 和 AWVALID与AWREADY有无关系?实际上是,只要设计中的线没有进行相连,就是没有关系,针对于AXI而言,甚至可以 BREADY 信号第一个拉高,再去考虑其他信号的关系,唯一需要满足的即为写回复通路与写数据通路之间的约束,剩下的信号都是自由的。

1.3.3 写操作约束关系(AXI4.0版)

AMBA4在兼容AMBA3的基础上更为严格,目的是希望从设备不会在接收到数据信号后还需要等待地址信号。

推荐阅读:

https://developer.arm.com/documentation/100806/0402/?lang=en

https://aijishu.com/a/1060000000134828

http://www.tlcement.com/37357.html

https://zhuanlan.zhihu.com/p/96804919