Verdi/Coverage tool 学习 第1节(入门篇)

目录

1. Verdi-Coverage 工具概述

2. VCS使用实例

3. VCS中的覆盖率分析

3.1 覆盖率类型

3.2 Coverage Database的产生

3.3 其他的vcs编译和仿真中的选项

3.4 有时需要Merge 多个Coverage 到一起

4. 查看Coverage的方法

4.1 使用URG 查看

4.2 使用verdi查看

4.3 使用DVE查看

1. Verdi-Coverage 工具概述

VCS对应的waveform工具有DVE和Verdi, DVE因为是原生的,所以VCS对DVE非常友好。但DVE已经过时了,其对uvm等新feature支持的不好。Verdi是Debussy公司的产品,现在已被Synopsys收购并着力发展,说以Verdi是未来的潮流。所以此文的dump fsdb波形和查看coverage都用verdi。具体来说VCS两步是:

1. 编译verilog文件成为一个可执行的二进制文件命令为:vcs source_files

2. 运行该可执行文件:./simv

2. VCS使用实例

此例子涉及task和$value$plusargs等verilog语法,忘记用法的话可以查阅资料再复习下。

具体vcs命令是:

vcs -sverilog -R -fsdb -ucli -do run_vcs.tcl -cm line+tgl+branch+assert -cm_name test1 +test_name=test1 tb_top.v

vcs -sverilog -R -fsdb -ucli -do run_vcs.tcl -cm line+tgl+branch+assert -cm_name test2 +test_name=test2 tb_top.v

顶层 tb_top.sv 文件内容如下:

module tb_top();

reg clk, rst, load;

wire [3:0] out;

always #5 clk=~clk;

reg [255:0] test_name;

initial

begin

clk=1'b0; rst=1'b0; load=0;

#30;

$value$plusargs('test_name=%s',test_name);

if(test_name=='test1')

test1;

else if(test_name=='test2')

test2;

#70;

$finish;

end

task test1;

rst=1'b1;

#10 load=0;

endtask

task test2;

rst=1'b1; load=1;

#10 load=0;

endtask

counter u_counter(.reset(rst),

.clk(clk),

.load(load),

.load_value(4'h8),

.q(out));

endmodule

module counter(reset,clk,load,load_value,q);

input reset,clk;

input load;

input [3:0] load_value;

output[3:0] q;

reg[3:0]q;

reg[3:0]count;

always@(posedge clk)

if(!reset)

q<=4'h0;

else if(load)

q<= load_value;

else if(q==4'b1111)

q<=4'b0;

else

q<=q+1;

endmodule

文件 run_vcs.tcl内容如下:

run_vcs.tcl:

config timebase 1ns

scope tb_top

run 1ns

call \$fsdbDumpfile('counter.fsdb');

call \$fsdbDumpvars(0,tb_top);

call \$fsdbDumpSVA;

# Run to completion

run

quitverdi -cov -covdir simv.vdb/ &

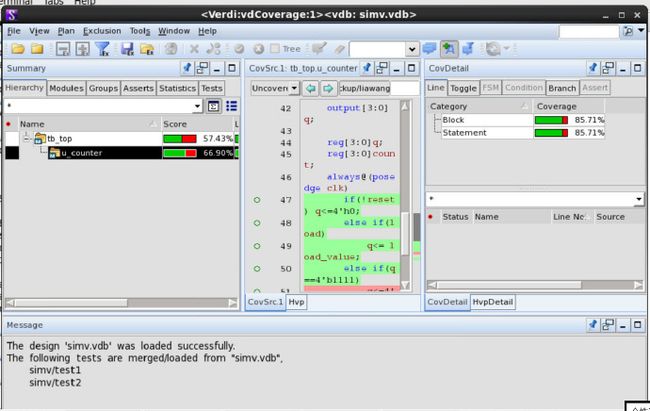

简单解释一下这里的选项:-sverilog是说支持sv语法;-R表示编译后立即执行;-fsdb表示dump fsdb文件 ;-ucli -do run_vcs.tcl表示要执行这个仿真tcl控制; -cm line+tgl+branch+assert表示 coverage覆盖line/toggle/branch/assert ;-cm_name test1表示生成coverage的一个test的目录名称test1(仿真后会生成simv.vdb/snps/coverage/db/testdata/test1);+test_name 表示要传递给TB一个test_name 参数。这个例子运行后,产生simv.vdb/snps/coverage/db/testdata/test1 和simv.vdb/snps/coverage/db/testdata/test2 两个 test的coverage文件,用verdi打开是这样的界面:

3. VCS中的覆盖率分析

3.1 覆盖率类型

VCS在仿真过程中,也可以收集Coverage Metric(覆盖率度量)。其中覆盖率类型有:

1)Code Coverage:包括line,condition, branch, toggle和FSM coverage。

2)Functional Coverage:包括covergroup,assert 。

3.2 Coverage Database的产生

包含所有的有关coverage的信息,默认放在simv.vdb文件夹下。db中的默认路径是,snps/coverage/db/testdata/line.verilog.data.xml(fsm/cond/tgl/branch等xml信息)。

3.2.1 在编译命令中:

vcs [cover_options] [compile_options] source.v

[cover_options]: -cm line+cond+tgl+fsm+branch+assert

-cm_dir 在compile options中改变simv.vdb文件夹的位置。

-cm_name 指定testname。主要改变testname在db中的命名。

3.2.2 在仿真过程中:

simv [cover_options] [run_options]

[cover_options]: -cm line+cond+tgl+fsm+branch+assert

[run_options] : 指定 runtime options。

3.3 其他的vcs编译和仿真中的选项

-cm_hier,在编过程中,指定收集coverage的scope。(格式可以包含正则表达式,语句可以+tree -tree -moduletree等)

-cm_assert_hier,在编译过程中,只是指定不收集coverage的assert hier。其中hier的表示,+/- module,+/- tree,+/-assert

-cm_count,在gui和urg report中,显示次数,比如toggle的次数。

-cm_glitch period,不收集一定范围的glitch的coverage。simulation option

-cm_start/stop,指定coverage收集的时间,simulation option coverage group相关的option;

-covg_disable_cg,关闭所有的coverage group的收集urg生成report中的option:

-dir,指定需要拿到的db的hier,

-dbname,指定输出的merge db的hier

-elfile,指定exclusive的file,这样更好计算coverage。

-elfilelist 忽略中每一个.el文件。(Specifies a file containing a list of exclude files)

-noreport,不输出最终的report,只是merge db

-format text/both,指定report的输出格式

-matric [line,cond,fsm,tgl,branch,assert]执行计算的coverage类型

-parallel,并行merge

-full64,以64bit的程序进行merge

-plan,-userdata,-userdatafile,-hvp_no_score_missing,指定hvp相关的生成信息。3.4 有时需要Merge 多个Coverage 到一起

实际工程中urg除了生成coverage报告,还经常要把几个仿真产生的vdb文件merge到一起,三个目的:

1. 实现比较高的coverage

2. 让verdi load coverage速度大大提高(我们几百个test下来,merge后load只要几分钟,而不merge需要半个到一个小时)

3. 不同level testbench跑出来的结果需要merge到一起(前公司用过把block的merge到system level)

这个merge+生成coverage命令大体是这样的

urg -full64 -metric line+tgl+cond+fsm+assert+branch -warn none -dbname .vdb -dir simv.vdb -elfile

注意:其中-dir之后的第一个vdb会被认为是base data,如果产生其他vdb的RTL与base不同,将不能被Merge进来

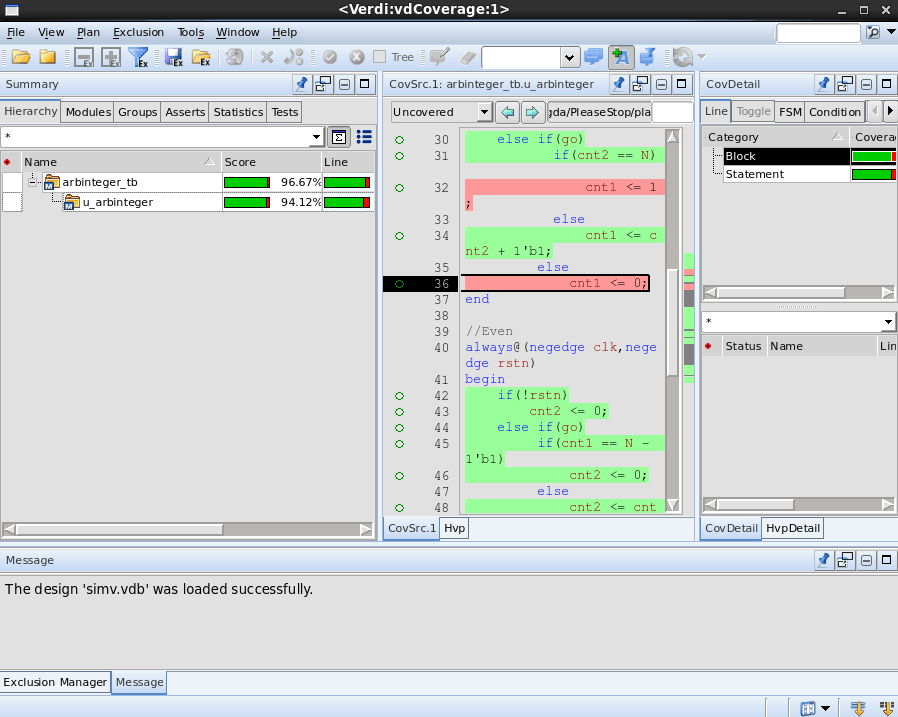

verdi查看coverage命令:**verdi -cov -covdir .vdb &**

如下是某个工程中使用的生成coverage并merge若干vdb文件到vcs_sim_exe_total.vdb的命令:

urg -full64 -parallel -show ratios -show tests -dir /proj/vcs_sim_exe_merge.vdb /proj/vcs_sim_exe _bak.vdb -hier /proj/dut_hier -elfilelist /proj/elfilelist.el -plan /proj/vplan/DUT.hvp -dbname /proj/vcs_sim_exe_total.vdb -report /proj/rpt/4332 -log /proj/gen_cov_dut.log

这里特别说明下这个选项: -hier /proj/dut_hier

-hier表示只针对dut_hier中定义的(URG has an option, -hier, that accepts a subset of the controls that can be used in the compile-time -cm_hier file.)spec说不太常用。

4. 查看Coverage的方法

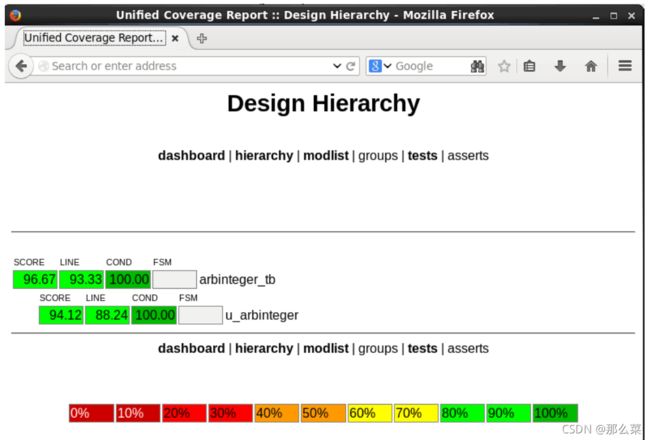

4.1 使用URG 查看

- 使用urg处理后查看:urg处理,默认生成urgReport目录。

- 具体命令: urg -full64 -dir simv.vdb

- urgReport目录下firefox浏览器查看tests.html

4.2 使用verdi查看

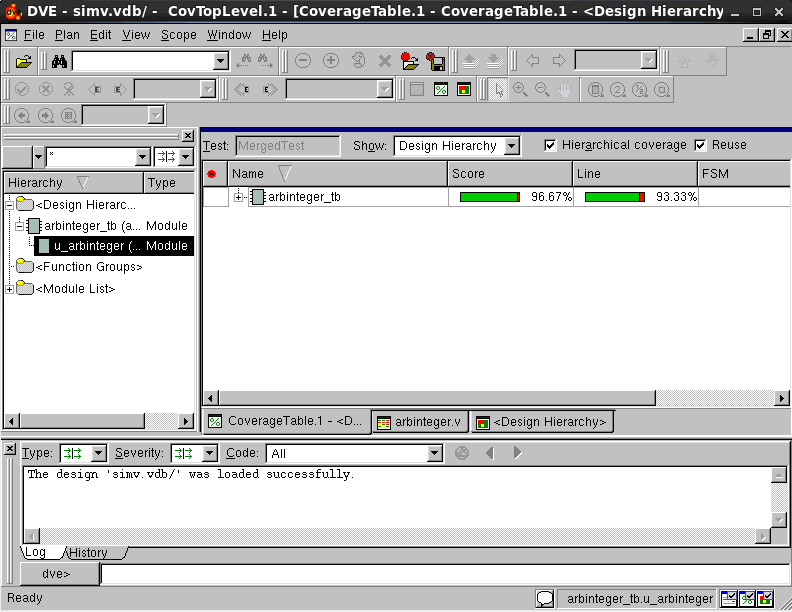

verdi -cov -covdir simv.vdb 4.3 使用DVE查看

dve -covdir simv.vdb感谢大佬的分享!!!

coverage report - 纟彖氵戋 - 博客园 (cnblogs.com)