AURIX TC3XX Cached PFLASH与Non-Cached PFLASH的区别

Cached ? Non-Cached?

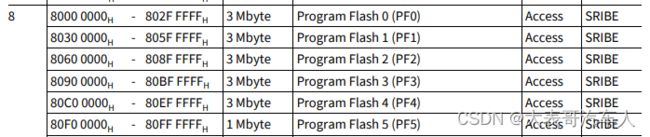

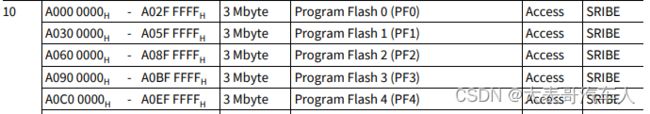

在阅读TC3XX的用户手册时,在内存映射表中,有两个segment都是Program Flash,而且大小都一样是3M,一个是segment 8

另一个是segment10

这难免让人产生疑惑,二者区别在哪?

通过搜索在infineon开发者论坛中发现有人在问类似的问题,我将该问题的解答分析一下。

同一块物理闪存存在于缓存区域和非缓存区域。主要的区别在于CPU访问它们的方式。

-

缓存地址访问:如果CPU通过缓存地址访问闪存,那么获取的数据会存储在CPU的缓存中。后续的任何访问都会使用缓存中的数据,而不是物理读取闪存。这可以显著加快程序的执行速度。

-

非缓存地址访问:如果使用的地址是非缓存的,那么读取操作总是物理执行的,也就是每次都直接从闪存中读取数据,而不使用CPU缓存。

需要注意的是,使用缓存数据的方法有一定的风险。如果你更改了闪存中的基础数据,但CPU缓存中的数据还未更新,那么CPU读取到的将是旧的数据。这可能会导致数据的不一致性。所以在处理闪存中的数据时,我们需要考虑到这种可能的情况,并设计出正确的数据同步或者更新策略。

二者的访问机制对比与安全机制的选择

进一步了解闪存读写的一些操作和可能的问题。

数据一致性的检查

最好在非缓存的闪存(Non-cached)上做检查,因为这样可以确保读取操作真正发生。因为如果使用缓存地址进行读取操作,那么如果闪存中的数据在读取到缓存后被修改,那么CPU缓存中的数据将会与实际的闪存中的数据不同,从而可能引发问题。

闪存的写入和擦除是通过reflashing完成的。但是,写入/擦除操作是通过DMU(数据管理单元)中的命令序列完成的。所以,如果CPU已经从闪存读取数据到其缓存,然后有一些操作reflash了PFlash,那么你会发现CPU缓存中的数据和PFlash中的数据不同。

需要注意的是,reflash需要花费大量的时间,所以在运行代码时,CPU可能会尝试加载其他数据到缓存,并且会注意到闪存不可用,因为它正在被更改。这里期望的是,进行这样操作的软件程序员会在代码中添加一些检查机制,但是也有可能出现没有做这样的检查。

因此,设计好的数据一致性策略和正确的程序检查机制在处理闪存数据时十分重要,以防止因数据不一致而引发的问题。

假设你的安全机制是想要检查闪存数据的安全性。因此,如果你从缓存地址运行,如果数据已经在缓存中,你所做的只是检查缓存内容是否正确 - 你不会检查到闪存本身路径的安全性。当数据进入缓存时,你已经证明了路径是正常的,但你并没有检查之后会发生什么。如果数据因为尚未在缓存中而必须被获取,那么你无论如何都不会获得速度提升,因为你仍然需要获取数据。

所以总结一下,对于一个安全机制,我会使用非缓存地址,以确保我们真正测试的是我们感兴趣的路径的安全性。

数据安全机制的选择

数据管理单元(DMU)会在需要的时候被用于重新编程闪存,所以在标准操作中,它不应该被运行。

当数据存储在缓存中时,应该受到ECC(错误检测和纠正)的保护(ECC值与数据一起存储)。因此,当从缓存中读取数据时,CPU将检查ECC并在出现不匹配时标记错误,因此缓存中的数据是受保护的。

ECC是一种用于检测和纠正单个数据位错误的技术。在数据被存储到缓存中时,会生成对应的ECC值。然后在读取缓存中的数据时,会重新计算ECC并与原来的ECC值进行比较,如果出现不匹配,说明数据在存储过程中或者存储期间发生了错误,CPU就会触发一个错误信号。

ESM(错误信号模块)旨在检查PFlash的内容 - 如果你从缓存中获取内容,那么你的安全机制将不再测试PFlash,你每次只是重新读取缓存的内容,假设所有的数据都在那里。

因此,如果你反复从缓存中读取,你可以看到你在缓存中是否有永久性或非永久性的错误,但你不会标记PFlash为损坏并刷新/替换一个字线。为了确保你真的在测试PFlash,我认为ESM必须使用非缓存地址。这确保你真的在检查PFlash本身是否被损坏,然后你可以使用结果来看你是否需要更换或刷新闪存。

对缓存的访问机制

闪存在物理上是相同的。所以当CPU使用缓存地址进行读取时,它首先会检查缓存内容,如果命中了,它就会从缓存中返回数据。如果没有命中,它会从PFlash中进行256位(BTR4)的读取,并把内容存入缓存。如果它在顺序执行一个程序,那么它很可能会去读取闪存中的下一个256位数据。还要注意,PFlash内置了一个预取机制 - 它会去获取下一个256位的数据,假设这就是CPU接下来需要的。

如果你从非缓存地址访问,那么缓存将不会被检查,它将直接从PFlash访问。然而,它会获取它需要的数据,而不是总是做一个BTR4/256位的读取。为了保持性能,PFI(PFlash接口)会将从PFlash读取的256位数据存储在本地缓冲区中,并从中提供获取,直到地址进入下一个256位,那时它将获取该数据(尽管如果有空闲的预取缓冲区,它可能会去获取下一个256位数据)。

CPU是否继续步进和获取将取决于程序和它预测接下来需要什么。

所以闪存在物理上同时存在于两个地址空间,而缓存则被用以提高CPU的访问速度。然而,你的安全机制是为了测试实际的PFlash,这就是为什么使用非缓存地址是一个更好的主意,因为这样你就可以确保你正在测试你打算测试的内容。并且,通过获取10个页面,你还可以确保你已经清空了所有可能的缓冲区,并且真正从闪存返回了数据。