LC3、MIPS32、RISC-V指令集架构整理

LC-3

寻址

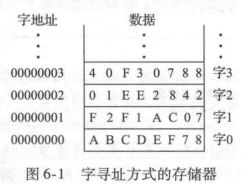

LC-3可寻址空间大小是2的16次方,寻址基本单位是16位。我们将这16位称为一个字,LC-3是字寻址。

寻址模式

立即数寻址、寄存器寻址、相对寻址、间接寻址、基址偏移

寄存器

临时存储空间——寄存器。LC-3中提供了一组通用寄存器。

寄存器的特性:

(1)记忆特性 :存储信息可读,大小是一个字(16bit)

(2)独立寻址 :LC-3中提供了8个GPR——R0、R1...R7

指令集

指令由操作码和操作数组成——操作码和操作数。

操作码

指令的 bit【15:12】。 指令可分为运算、数据搬移和控制。

数据类型——补码整数

条件码——N Z P

操作指令

LC-3只支持三种操作指令 ADD AND NOT

NOT 操作码 1001 在15-12,源寄存器 在8-6,11-9位目的寄存器,bit5-0全为1。

ADD 操作码 0001 AND操作码 0101 双操作数 他们都需要两个16位源操作数。ADD指令执行两个操作数的补码假发,AND执行按位与。 源操作数均为bit[8:6],目的操作数均为bit[11:9]。 均为寄存器寻址方式。

搬移指令

LC-3有7种搬移指令:LD、LDR、LDI、LEA、ST、STR、STI

load和store指令格式如下:

数据搬移需要两个操作数,其中一个必然是寄存器,另一个是内存或输入/输出设备。

bit【11:9】 标识操作数之一,即寄存器。若为load指令,则代表目的寄存器,若为store指令,则该寄存器内容将被写入内存。bit【8:0】是地址生成位。

PC相对寻址

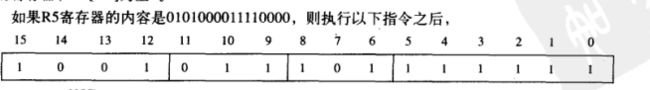

LD(opcode=0010)和ST(opcode=0011)采用PC相对寻址。bit[8:0]代表当前PC的偏移值。地址计算方法是先将bit[8:0]内容做16位作战,然后与PC相加。

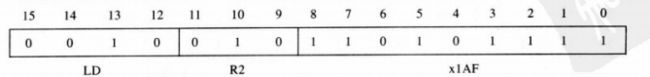

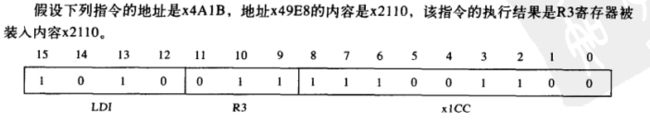

间接寻址

LDI(opcode = 1010) 和 STI (opcode = 1011)采用间接寻址模式。该地址存放的是另一个地址,存放的地址才是load或store操作数的真正地址。因此称为间接寻址。bit[11:9]标识了LDI的目的寄存器和STI的源寄存器。

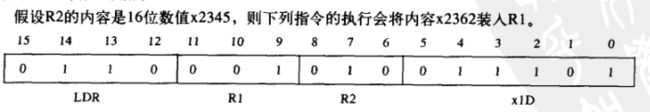

基址偏移寻址

LDR(opcode = 0110)和STR(opcode = 0111)采用基地址+偏移的寻址模式。操作数的弟子hi由6bit偏移量的符号拓展和基地址寄存器的内容相加而成。6-bit的偏移量来源于指令的bit[5:0]字段,而基地址寄存器则由指令的bit[8:6]字段标识。

6bit补码使用时先符号拓展为16位值,然后与基地址寄存器相加。

立即数寻址

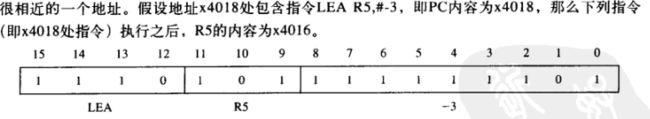

LEA有效地址装载指令 opcode = 1110.将增量PC与 bit[8:0]的符号扩展值相加并装入bit[11:9]指定的寄存器。

LEA指令用于对寄存器初始化,向寄存器装入一个地址的值。

控制指令

能够改变指令执行顺寻的指令。

包括五种:条件跳转、无条件跳转、子程序调用、TRAP、中断返回。

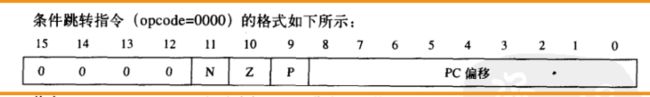

条件跳转指令 opcode = 0000

bit[11:9] 分别对应三个条件码 。所有会对寄存器进行写操作的指令都会设置这三个条件码——ADD AND NOT LD LDI LDR LEA

取指令和译码节拍正常进行,在取指令节拍之后,PC自动增量。地址计算节拍也与LD和ST指令相同。而在执行节拍,处理器将检测某个条件码是否为1.若任意一个为1,则PC内容重新修改。若三位都是1,则三个条件码都将被检测,PC内容必然要更新,即装入在地址计算阶段得出的地址。

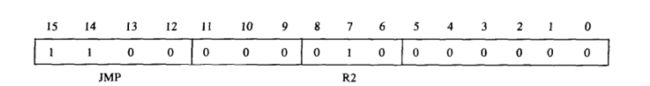

JMP指令 opcode = 1100

将寄存器bit[8:6]的内容装入PC寄存器

TRAP指令 opcode = 1111

改变PC内容。

指令周期控制方式

(1)FETCH

取指令节拍。PC寄存器提供访问内容的地址。在第一个时钟周期,PC内容通过全局总线被装入MAR,同时PC自加。在下一个周期 内存返回值被装入MDR,再下一个周期,MDR内容被转入IR寄存器。

(2)DECODE

IR的内容被译码,由控制逻辑产生对应的信号。控制指令的下面操作郭程根据操作码选择寻址模式。并进行操作

(3)EVALUATE ADDRESS

在下一个时钟周期,开始地址的相关计算。将寄存器和IR的内容进行操作,并通过MARMUX开关传入MAR。

(4)OPERAND FETCH

在下一个时钟周期,该地址内存单元的数据被转入MDR。

(5)EXECUTE

节拍,部分指令直接跳过

(6)STORE RESULT

存储结果。

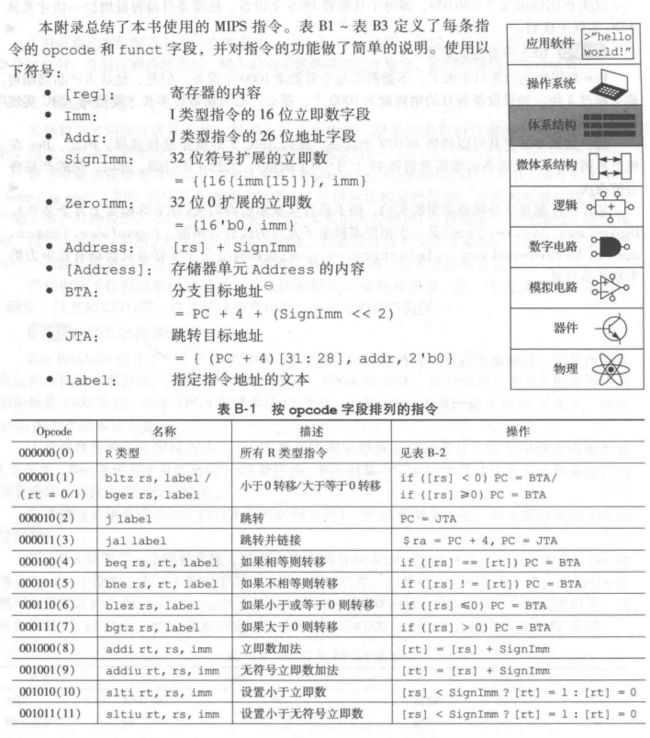

32位MIPS指令集架构分析

寄存器

MIPS体系结构有32个寄存器。寄存器越少访问速度越快。

MIPS使用18个寄存器存储变量 $S0~$S7和$t0~$t9。由$s开头的寄存器称为保存寄存器(saved register),存储如a,b,c的变量。其还有一个特殊用途——函数调用。$t开偷的寄存器为临时寄存器,存储临时变量。

存储器

MIPS使用字节寻址存储器

lw指令指定内存有效地址为基地址与偏移量的和。

MIPS使用存储字指令sw从寄存器向存储器写数据字。

使用方法:lw 目标寄存器 偏移量(基地址寄存器)

sw 寄存器 偏移量(基地址存储器)

字节存储器的两种组织方式——大端和小端。大端 第0个字节在MSB(最高有效字节;小端 第0个字节在LSB。

立即数

MIPS中 立即数使用16位补码表示,范围在[-32768,32767]

lw sw addi支持立即数

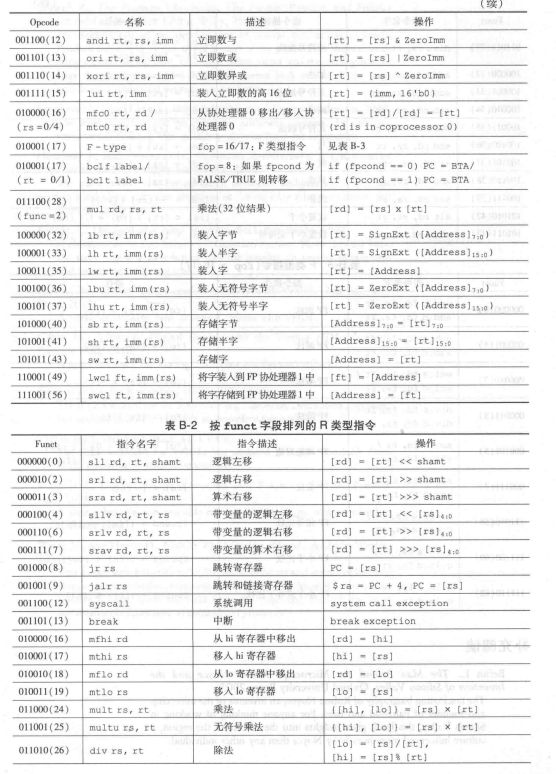

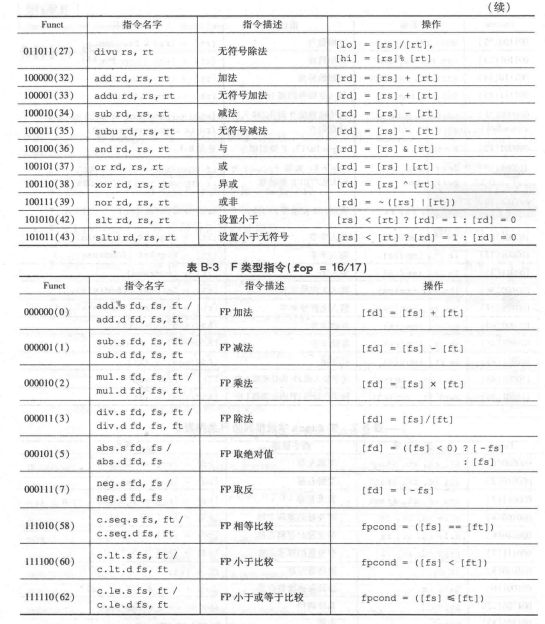

指令集格式

三个寄存器操作数 如add 、sub——————R类型

两个寄存器操作数和一个16位立即数————I类型

一个26位立即数,没有寄存器操作数————J类型

指令集分类

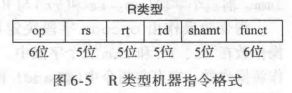

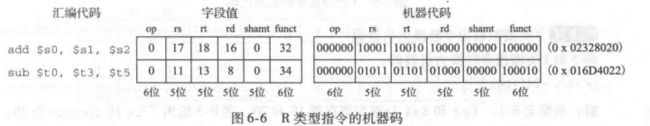

R类型(register-type)

包括3个寄存器操作数——两个为源操作数,一个为目的操作数

操作编码: op——操作码 funct——函数

R类型中op都是0,功能由funct定义。

源寄存器 rs rt

目的寄存器 rd

shamt 用于移位操作

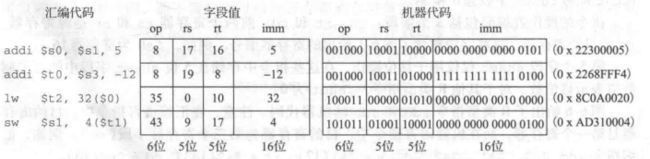

I类型(immediate-type)

立即数类型

指令的操作由op决定

操作数在rs、rt、imm三个字段产生。

rs和imm用作源操作数。rt有时用作源操作数,有时用作目的操作数

imm 立即数 为负时,16位有符号二进制补码数

NOTE: imme只有16位 但是却用于32位运算。32位中的高16 对于正立即数,前16位全0,负立即数前16位全1.(符号位拓展)但是在逻辑操作(andi、ori、xori)中,高位为0——0拓展。

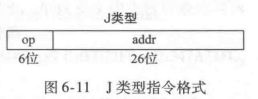

J类型(jump-type)

仅用于跳转指令。

addr 地址操作数。

操作指令由opcode决定。

因此,解释机器语言,首先看高6位是否为全0,是则为R,否则为I或J。

寻址方式

寄存器寻址——R类型

立即数寻址——部分I类型 如 addi lui

基地址寻址——存储器访问 如sw lw

PC相对寻址——条件分支指令

伪地址寻址——J类型。

26位编码JTA(jump target address 跳转目标地址)但是JTA最低两位总是0因为指令是字对齐的 。下一个26位JTA[27:2]由addr指出,最高位JTA[31:28]由PC+4的最高位得到。

指令周期控制方式

单周期

多周期

流水线

编程

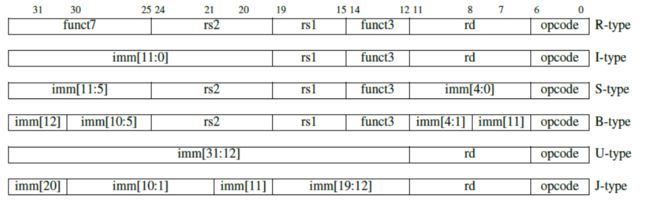

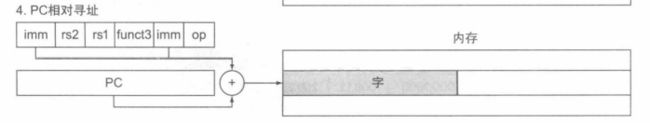

RISC-V指令集结构分析

指令集格式

寄存器-寄存器操作的R类型指令

短立即数和访存load操作的I型指令

用于访存store的S型指令

用于条件跳转操作的B类型指令

用于长立即数的U型指令

用于无条件跳转的J型指令

编程

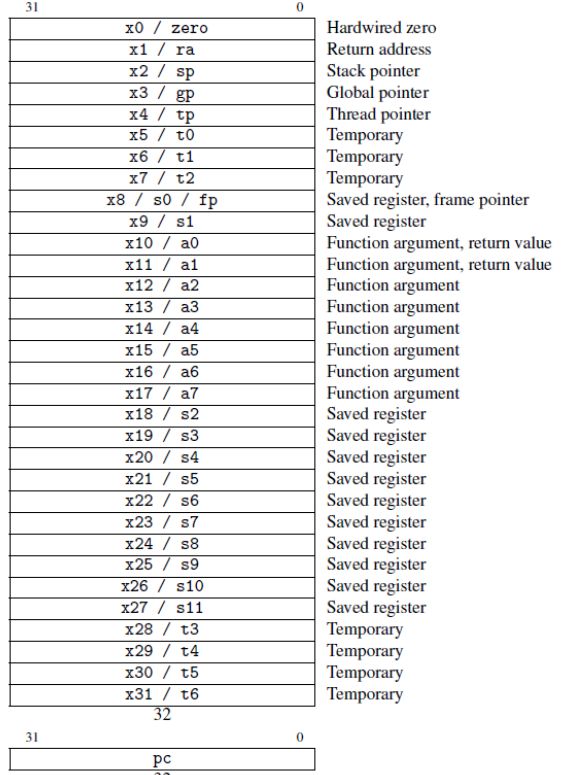

寄存器

RV32I 有 31 寄存器加上一个值恒为 0 的 x0 寄存器。

RISC-V 选择了小尾端字节序

NOTE: RISC-V中没有字节或半字宽度的整数计算操作。操作始终是以完整的寄存器宽度。

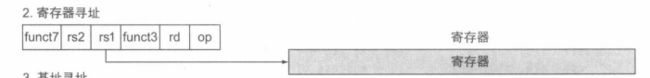

寻址方式

立即数寻址 : 操作数 是 指令本身的常量

寄存器寻址 : 操作数在寄存器中

基地址或偏移寻址: 操作数于内存中,其地址是寄存器和指令中的常量之和。

PC相对寻址:分支地址是PC和指令中常量之和。

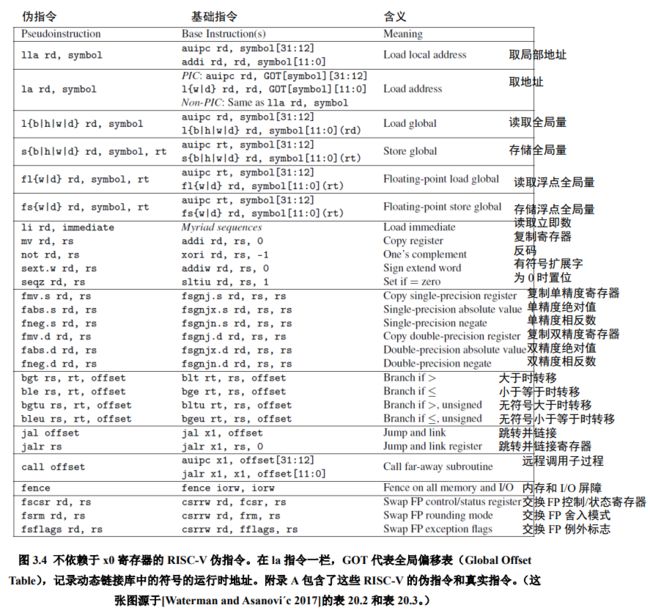

汇编指令格式

其中x0寄存器始终为0.

无对x0的要求。

RISC-V处理器采用5指令周期控制方式方式

(1) 从存储器中取出指令

(2) 读寄存器并译码指令

(3) 执行操作或计算地址

(4) 访问数据存储器中的操作数

(5) 将结果写入寄存器