【PCIE体系结构十二】链路训练的相关基础前菜

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《PCI.EXPRESS系统体系结构标准教材 Mindshare》

目录

物理层控制字符

链路训练中的Ordered Set

物理层控制字符

上篇文章讲进入发送多路复用器的内容时提到过控制字符,这些控制字符是组成数据包或ordered set的重要组成部分,需要再详细介绍一下。Gen 3之后,不叫控制字符了,定义了一些framing token(帧令牌),当传输的不是ordered set时,用token来区分载荷是TLP还是DLLP,大体功能和之前的控制字符类似。这些控制字符在经过物理层是不做加扰的。

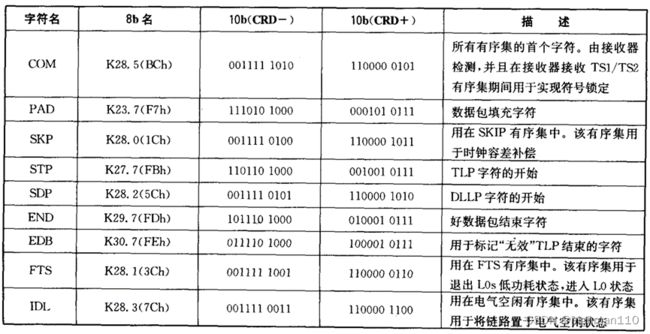

Gen 1和Gen 2的控制字符定义如下:

解释一下几种字符,SDP、STP、End这种就不多说了,意思跟上面图里的一样。

COM,俗称Comma码,001111 1010或110000 0101,其作用是复位LFSR为初始值,这个在链路训练时需要用到,COM作为所有order sets的开始字符,随后跟着三个或者更多的信息字符。接收端确定收到COM的过程叫做symbol lock。有以下三种情况会用COM来实现符号锁定:

1、在首次建立链路时的链路训练期间传输TS1和TS2有序集(每个有序集都以COM符号开始)。

2、在由于链路上有问题而发起的链路重新训练期间传输TS1和TS2有序集(每个有序集都以COM符号开始)。

3、发送器发送FTS有序集,以通知接收器重新获得比特锁定和符号锁定,并将链路状态从L0s(低功耗状态)改变到L0(正常工作状态)。

PAD,主要用于Mult-Lane中,当一个包的长度比较短,有的Lane可能就没有数据可以发了,这时候可以用PAD字符来填充。

SKP,SKP字符用做SKIP有序集的一部分。传输SKIP有序集是为了进行时钟容差偿。

FTS,当链路进入低功耗状态,发送端要唤醒链路时,会首先发送一定数量的FTS Ordered Sets,接收端会重新取得Bit Lock(就是接收端CDR恢复出时钟的过程)和Symbol Lock(就是接收端确定收到COM的过程)。

IDL,该字符用做电气空闲有序集的一部分。传输该有序集是为了通知接收器,该链路将要转换到L0s低功耗状态(也称做链路的电气空闲状态)。

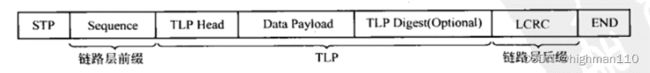

如下图是物理层TLP的报文格式:

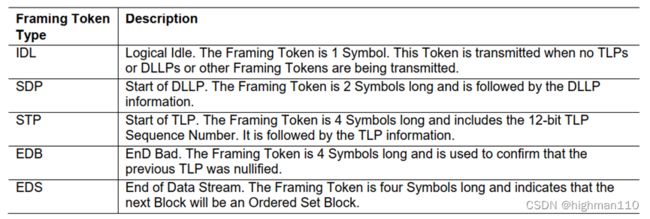

Gen3之后的framing token定义如下,详细内容请查阅PCIE 3.0 spec:

链路训练中的Ordered Set

物理层会发送一些特殊的字符序列来进行链路训练,这些序列也称PLP,物理层报文,PCIE总线规范定义了以下几种order sets:

TS1 and TS2 Ordered Set (TS1OS/TS2OS):即training sequence 1和training sequence 2,这两种PLP在链路训练的多个状态机中使用,其中TS1序列的主要作用是检测PCIe链路的配置信息,TS2序列确认TS1序列的检测结果。

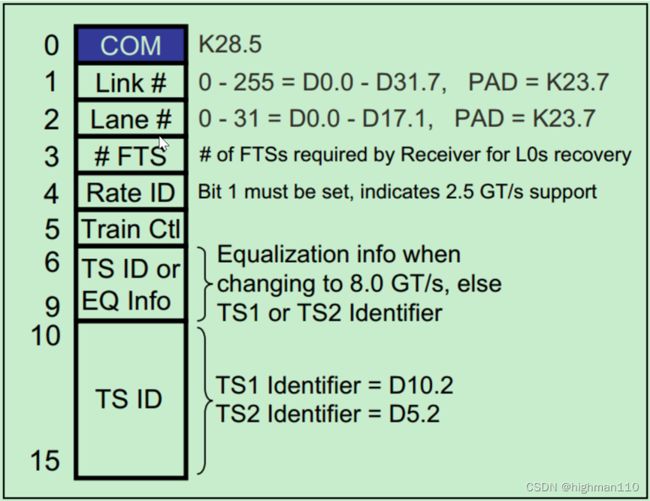

TS1和TS2类似,都是由16个Symbol组成(每个symbol 10bit,8b/10b编码之后的Byte),区别在于symbol 6~9(速率达到8GT/s时的均衡信息或TS1、TS2标识符)和symbol 10~15(TS1、TS2标识符),其结构图如下图所示:

第0字符:在速率为2.5GT/s或者5G/s时,为COM控制字符,表示TS1/TS2序列的开始。COM字符序列将复位LF-SR寄存器。在速率为8GT/s或者以上时,TS1为0x1E,TS2为0x2D。

第1字符:在链路训练的初始阶段,第1字符存放控制字符PAD,即为空,注意空不是全0或者全1,是8B/10B或者128B/130B编码组,这个前面也说到过,且不同的速率情况下PAD的码型和数量也是不同的。而在链路的配置阶段,该字符存放端口使用的Link Number。

第2字符:在链路训练的初始阶段,第2字符为控制字符PAD,即为空。而在链路的配置阶段,该字符存放端口使用的Lane Number。

第3字符:为FTS序列的个数(N_FTS)。不同的PCIe链路需要使用不同数目FTS序

列,才能使接收端的PLL锁定接收时钟。

第4字符:存放当前PCIe设备支持的数据传送率,第1位为1表示支持2.5GT/s传送率;第2位为1表示支持5GT/s及传送率;第3位为1表示支持8GT/s的数据传送率;第4位为1表示支持16GT/s传送率;第5位为1表示支持32GT/s传送率;如果已经发送11111b并通过了训练,会继续发送10111b来表示支持64G GT/s传送率。第6位是一个多功能位,当PCIe链路的没有配置成功时可以作为Notification位,也可以用作发送链路De-emphasis的使能位,它的具体定义在不同的LTSSM状态下有不同的功能;第7位为speed_change位,当该位为1时,通知PCIe链路对端设备需要改变传送速率。

第5字符:存放命令。第0位为“Hot Reset”,第1位为“Disable Link”,第2位为“Loopback”,第3位 “Disable Scrambling”,第4位为“Compliance Receive”。其他bit定义大家自行查阅PCIE规范,这里不多提了。当接收逻辑RX收到TS1或者TS2序列后,将根据该字符的命令进行对应的操作。

Electrical Idle Ordered Set (EIOS):即idle序列,在正常情况下,发送端欲要进入electrical idle状态时,将首先向对端发送idle序列,才能进入。electrical idle是一种PCIE链路的低功耗状态。如果PCIe设备使用2.5GT/s的传送率时,Idle序列由1个COM字符加3个IDL字符组成,即“COM IDL IDL IDL”;如果PCIe设备使用5GT/s的传送率时,Idle序列由两组这样的字符序列组成,即“COM IDL IDL IDL COM IDL IDL IDL”;如果PCIe设备使用8GT/s及以上传送率时,Idle序列由16个66h字符组成。Electrical Idle状态是一种特殊的Idle状态,处于该状态时,PCle链路使用的功耗最低。PCIe设备可以根据链路的使用情况确定当前链路是否处于Electrical Idle状态,而不是必须收到Idle序列后进人该状态。如一个PCIe设备在很长一段时间没有收到流量控制报文或者链路处于Electrical Idle状态时,也可以推断出对端设备处于Idle状态。

Electrical Idle Exit Ordered Set (EIEOS):用来退出低功耗状态。当发送端退出IDLE状态时,必须向对端发送EIEOS序列。EIEOS序列仅在链路传送率大于2.5GT时使用,传送率为5GT/s时,该序列由1个COM(K28.5)字符、14个EIE字符(K28.7)和D10.2(TS1识别符)组成;传送率为8GT/s时,该序列由16个连续交替的00h、11h字符组成;传送率为16GT/s时,该序列由4个连续交替的0000h、1111h字符组成;传送率为32GT/s时,该序列由2个连续交替的00000000h、11111111h字符组成;

FTS Ordered Set (FTSOS):即fast training sequence,该字符序列协助接收逻辑获得bit lock和symbol lock。传送率为5GT/s及以下时,单个FTS序列由1个COM字符加3个FTS字符组成,该序列的主要目的是使接收逻辑RX重新获得Bit/Symbol Lock。发送逻辑需要向对端发送多少个FTS序列由接收到的TS1/2序列决定,TS1/2序列的第3个字符为需要发送FTS序列的个数,最多255个。传送率为8GT/s及以上时,序列有变化,大家自行查阅规范文档。

SKP Ordered Set (SOS):SKIP有序集用在多通道实现中,会在所有通道上定期发送SKIP有序集,以使接收时钟容差补偿逻辑能够补偿两个时钟之间的频率变化,这两个时钟一个是发送设备使用的时钟,用以定时输出串行比特流,另一个是接收器设备的本地时钟。接收器在其弹性缓冲区中向SKIP有序集添加一个SKP符号,从而防止由于发送器的时钟慢于本地接收时钟而可能出现的缓冲区下溢状况。另一方面,接收器检测其弹性缓冲区中SKIP有序集的SKP符号,以便防止由于发送器的时钟快于本地接收时钟而可能出现的缓冲区上溢状况。

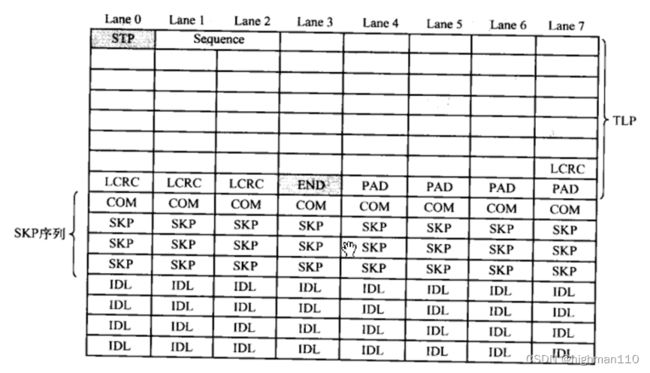

在PCIe总线中,Ordered Set的发送方式与TLP和DLLP有较大不同。假设一条PCIe链路由多个Lane组成,那么TLP和DLLP报文将分散到多个Lane中。而Ordered Set必须同时出现在这些不同的Lane,这几个Lane必须在同一个时间点发送Ordered Set。而不能出现一个Lane正在发送Ordered Set进行与链路训练相关的操作,而其他Lane进行其他数据传递的情况。PCIe链路发送TLP与发送Ordered Set的过程如下图所示。如在一个×4的PCIe链路中发送SKIP序列时,每一个Lane中都要出现“COM、SKP、SKP、SKP”这样的数流。其他Ordered Set的发送方法也与此类似。而TLP或者DLLP的发送分散到各个Lane 上。