各种加法器的比对分析与Verilog实现(5)

上一篇博客介绍了进位旁路加法器和进位选择加法器,本文将用Verilog代码进行实现。原理部分请看:

各种加法器的比对分析与Verilog实现(4)_Albert_yeager的博客-CSDN博客

下面使用Verilog进行实现:

1. 进位旁路加法器的Verilog实现

顶层模块(16比特进位旁路加法器)

module cska_16 (

input [15:0] op1,

input [15:0] op2,

output [15:0] sum,

output cout

);

wire [16>>2:0] c;

assign c[0] = 0;

assign cout = c[16>>2];

genvar i;

generate

for( i=0; i<16>>2; i=i+1) begin

cska_4 cska_4_u (

.op1( op1[i*4+3:i*4] ),

.op2( op2[i*4+3:i*4] ),

.cin( c[i] ),

.sum( sum[i*4+3:i*4] ),

.cout( c[i+1])

);

end

endgenerate

endmodule

中间模块(4比特进位旁路加法器)

module cska_4 (

input [3:0] op1,

input [3:0] op2,

input cin,

output [3:0] sum,

output cout

);

wire [3:0] p;

wire [4:0] c;

wire sel;

assign c[0] = cin;

genvar i;

for( i=0; i<4; i=i+1) begin

full_adder full_adder_u(

.a ( op1[i] ),

.b ( op2[i] ),

.cin ( c[i] ),

.cout( c[i+1] ),

.s ( sum[i] ),

.p ( p[i] )

);

end

assign sel = p[0] & p[1] & p[2] & p[3];

assign cout = sel ? cin : c[4];

endmodule

单元模块(全加器+P信号生成)

module full_adder (

input a,

input b,

input cin,

output cout,

output s,

output p

);

assign s = a ^ b ^ cin;

assign cout = a & b | (cin & (a ^ b));

assign p = a ^ b;

endmodule

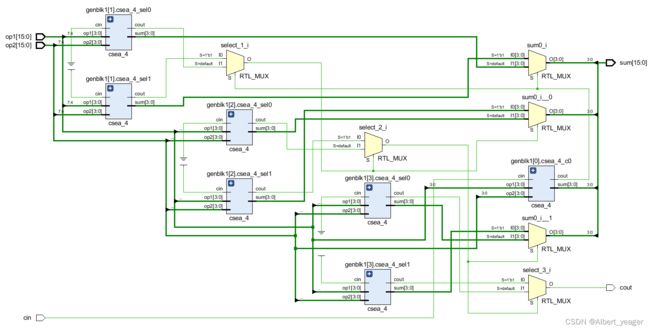

2. 进位选择加法器的Verilog实现

顶层模块

module csea_16 (

input [15:0] op1,

input [15:0] op2,

input cin,

output [15:0] sum,

output cout

);

wire [16>>2:0] c_sel0;

wire [16>>2:0] c_sel1;

wire [16-1:0] sum_sel0;

wire [16-1:0] sum_sel1;

wire [16>>2: 1] select;

assign cout = select[width>>2];

genvar i;

generate

for( i=0; i>2; i=i+1) begin

if(i==0) begin

csea_4 csea_4_c0 (

.op1( op1[3:0] ),

.op2( op2[3:0] ),

.cin( cin ),

.sum( sum_sel0[3:0] ),

.cout( select[1] )

);

assign sum[3:0] = sum_sel0[3:0];

end

else begin

csea_4 csea_4_sel0(

.op1( op1[i*4+3:i*4] ),

.op2( op2[i*4+3:i*4] ),

.cin( 1'b0 ),

.sum( sum_sel0[i*4+3:i*4] ),

.cout( c_sel0[i+1] )

);

csea_4 csea_4_sel1 (

.op1( op1[i*4+3:i*4] ),

.op2( op2[i*4+3:i*4] ),

.cin( 1'b1 ),

.sum( sum_sel1[i*4+3:i*4] ),

.cout( c_sel1[i+1] )

);

assign select[i+1] = select[i] ? c_sel1[i+1] : c_sel0[i+1];

assign sum[i*4+3:i*4] = select[i] ? sum_sel1[i*4+3:i*4] : sum_sel0[i*4+3:i*4];

end

end

endgenerate

endmodule

中间模块

module csea_4 (

input [3:0] op1,

input [3:0] op2,

input cin,

output [3:0] sum,

output cout

);

wire [4:0] temp;

assign temp[0] = cin;

genvar i;

for( i=0; i<4; i=i+1) begin

full_adder full_adder_u(

.a ( op1[i] ),

.b ( op2[i] ),

.cin ( temp[i] ),

.cout ( temp[i+1] ),

.s ( sum[i] )

);

end

assign cout = temp[4];

endmodule

单元模块

module full_adder(

input a,

input b,

input cin,

output cout,

output s

);

assign s = a ^ b ^ cin;

assign cout = a & b | (cin & (a ^ b));

endmodule

参考链接:

进位旁边加法器原理与设计

进位选择加法器原理与设计

求学路上,你我共勉(๑•̀ㅂ•́)و✧