FPGA基础知识-数据流建模

目录

学习目标

学习内容

1.连续赋值语句

2.延迟

3.表达式、操作符合操作数

4.操作符类型

学习时间

学习总结

学习目标:

提示:这里可以添加学习目标

1.讲述连续赋值语句,对于连续赋值语句的限制以及隐式连续赋值语句

2.解释赋值延迟,隐式赋值延迟以及用于连续赋值语句的线网声明延迟

3.定义表达式,操作符,操作数

4.列表解释所有类型的操作符,包括算术操作符、逻辑操作符、关系操作符、等价操作符、按位操作符、缩减操作符、移位操作符、拼接操作符和条件操作符等

5.使用数据流结构对实际的数字电路建模。

学习内容:

1.连续赋值语句

连续赋值语句是Verilog数据流建模的基本语句,用于对线网进行赋值。它等价于门级插述,然而是从更高的抽象角度来对电路进行描述。连续赋值语句必须以关键词assign 开始,

1.连续赋值语句的左值必须是一个标量或向量线网,或者是标量或向量线网的拼接,而不能是向量或向量寄存器。我们将在拼接操作进行讨论;

2.连续赋值语句总是处于激活状态。只要任意一个操作数发生变化,表达式就会被立即重新计算,并且将结果赋给等号左边的线网

3.操作数可以是标量或向量的线网或寄存器,也可以是函数调用

4.赋值延迟用于控制对线网赋予新值的时间,根据仿真时间单位进行说明。赋值延迟类似于门延迟,对于描述实际电路中的时序是非常有用的

例子如下:

assign out=i1&i2;//out是线网,i1和i2也是线网;

2.延迟

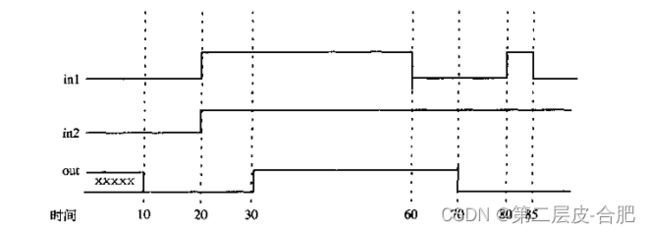

指定延迟的第一种方法是在连续赋值语句中说明延迟值,延迟值位于关键字assign 的后面。在上面的例子中,如果inl和 in2中的任意一个发生变化,那么在计算表达式in1& in2的新值并将新值赋给语句左值之前,会产生10个时间单位的延迟。如果在此10个时间单位期间,即左值获得新值之前,in1或in2的值再次发生变化,那么在计算表达式的新值时会取 in1或in2的当前值。我们称这种性质为惯性延迟。也就是说,脉冲宽度小于赋值延迟的输入变化不会对输出产生影响。

assign #10 out =in1&In2;//连续赋值语句中的延迟

1.当inl和 in2在时间单位20 处变为高电平时,out 在10个时间单位之后(即时间单位为30处〉变为高电平; 当inl和in 2在时间单位20处变为高电平时,out在10个时间单位之后(即时间单位为30处>变为高电平;

2.当in1和 in2在时间单位60处变为低电平时,out在时间单位70处变为低电平;in1在时间单位80处变为高电平,但是在10个时间单位之内重新变为低电平; 当in 1和in 2在时间单位60处变为低电平时,out在时间单位70处变为低电平,

3.in 1在时间单位80处变为高电平,但是在10个时间单位之内重新变为低电平;

4.因此,在时间单位80之后再过10个时间单位,重新计算表达式,此时 in1的值已经为0,因此out的值仍然为0。这说明如果脉冲的宽度小于指定的赋值延迟,就不会影响输出(即不会对赋值语句等号左边的值产生影响) 因此,在时间单位80之后再过10个时间单位,重新计算表达式,此时in 1的值已经为0,因此out的值仍然为0。(这说明如果脉冲的宽度小于指定的赋值延迟,就不会影响输出(即不会对赋值语句等号左边的值产生影响)

3.表达式、操作符合操作数

数据流建模使用表达式而不是门级原语来描述设计。表达式、操作符和操作数构成了数据流建模的基础。

表达式由操作符和操作数构成,其目的是根据操作符的意义计算出一个结果值。

操作数可以中定义的任何数据类型,但是某些语法结构要求使用特定类型的操作数。操作数可以是常数、整数、实数、线网、寄存器、时间、位选(向量线网或向量寄存器的一位)、域选(向量线网或向量寄存器的一组选定的位〉以及存储器和函数调用(将在后续章节中学习)。举例如下: 操作数可以是中定义的任何数据类型,但是某些语法结构要求使用特定类型的操作数.(操作数可以是常数、整数、实数、线网、寄存器、时间、位选(向量线网或向量寄存器的一位)、域选(向量线网或向量寄存器的一组选定的位>以及存储器和函数调用(将在后续章节中学习)。

操作符对操作数进行运算并产生一个结果。 操作符对操作数进行运算并产生一个结果.

4.操作符类型

Verilog 提供了许多种类型的操作符,分别是算术、逻辑、关系、等价、按位、缩减、移位、拼接和条件操作符。这些操作符中的一部分与C语言中的操作符类似。每个操作符都用一个符号来表示。,我们根据类型列出了所有操作符的符号。 Verilog提供了许多种类型的操作符,分别是算术、逻辑、关系、等价、按位、缩减、移位、拼接和条件操作符.这些操作符中的一部分与C语言中的操作符类似.每个操作符都用一个符号来表示。

学习时间:

20230614

学习总结:

1.连续赋值是数据流建模的主要语法结构。连续赋值总是处于有效( active )状态,即任一操作数的变化都会立即导致对表达式的重新计算。连续赋值语句的左侧值(赋值目标)必须是线网类型的变量或其连接。任何逻辑功能都能够使用连续赋值语句来完成。

2.延迟值用于控制右侧变量的改变和语句左侧被赋予新值之间的时间间隔。线网的(赋值)延迟可以通过assign语句、隐式连续赋值和线网声明三种方法来实现。

3.操作符的类型包括算术、逻辑、关系、等价、按位、缩减、移位、拼接、重复和条件.单目、双目和三目操作符分别具有一个、两个和三个操作符,而拼接操作符可以具有任意多个操作符。