北航计算机组成原理课程设计-2020秋 PreProject-Logisim-Logisim组合逻辑电路

北航计算机学院-计算机组成原理课程设计-2020秋

PreProject-Logisim-Logisim组合逻辑电路

本系列所有博客,知识讲解、习题以及答案均由北航计算机学院计算机组成原理课程组创作,解析部分由笔者创作,如有侵权联系删除。

从本节开始,课程组给出的教程中增添了很多视频讲解。为了避免侵权,本系列博客将不会搬运课程组的视频讲解,而对于文字讲解也会相应地加以调整,重点在于根据笔者自己的理解给出习题的解析。因此带来的讲解不到位敬请见谅。

子电路

子电路使用流程:

-

创建子电路——通过Project栏目下Add Circuit;

-

添加子电路内容——子电路布线

-

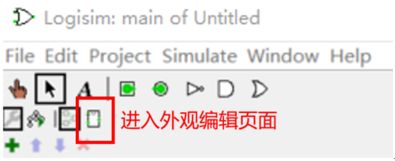

设置子电路外观

注:更改外观时,可对端口增加文字说明,提高可读性

- 引用子电路——使用3中设置的外观进行连接电路,封装子电路,使电路更加模块化,从而提升电路的可读性和可维护性。

Wire Bundles

下图表示不同的接线颜色所表示的含义:

对于一个完整且正确的电路,是以深绿色,浅绿色,黑色接线构成,绿色接线可以通过深浅直接判断出取值,而黑色接线,并不能直接反映出取值,这里建议大家使用Wiring库中的Probe元器件,可以对多位数据实时显示监控。

特别的,在构建大型的电路时,大量接线交叉将直接影响观察,在Wiring库中存在着可简化布线的原件Tunnel,请大家自行查阅Library Reference 参考文档并学习。

组合电路初步练习

Splitter

在使用Logisim的相关接线部件时,Splitter显得尤为重要,观察下图,填上正确的输出

答案:10

本题考查Splitter的使用,重点是观察好Splitter对应的位号即可。首先上面的AND元件左侧连接了Splitter的第0位和第2位,那么输入第0位是1,第2位是0,二者&运算结果是0,这一结果经过右边的Splitter传到输出的第0位,那么输出第0位即为0;同理观察下面的XNOR元件,连接左侧Splitter的第4位0和第6位0,XNOR计算规则为,输入相异则为0,输入相同则为1,因此输出1,而XNOR的右侧连接到右侧Splitter的第1位,那么输出第1位即为1,合在一起输出为10.

多路选择器、译码器和多路分配器

多路选择器

在组合电路中,多路选择器(Multiplexer,简称MUX)是非常重要的一类部件,他们在组合电路中扮演着非常重要的角色。下图是一个典型的Logisim中的多路选择器,左侧是多个输入,右侧是相应的输出,通过底部(黑色)的选择信号,对输入的信号进行选择后输出。另外一个端口是部件的使能端,当其为高电平(为1)时,整个部件使能工作。

MUX最为重要的功能就是从多个输入信号中选择一个作为输出,在我们未来的CPU设计中,我们需要设置很多的MUX来使得CPU中的数据通路能够处理复杂的指令集。

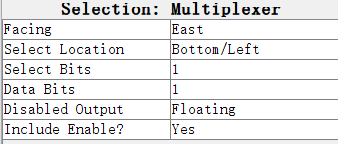

在具体使用中,当选中MUX时,需要关注左下角的Selection:Multiplexer界面,其中可以对数据位宽,选择位宽,是否有使能端等都可以进行相关设置,可以在实际搭建中灵活使用。

多路分配器

多路分配器和多路选择器功能恰好相反,即能够将1个输入数据,根据需要传送到多个输出端的任何一个输出端。

其有与多路选择器十分类似的Selection界面,这些可以在实际使用中进行设置。

译码器

译码器和多路选择器类似,同样是组合电路中非常重要的部件,如下图,右侧是多个输出,底部是黑色的选择信号与使能端。译码器最大的功能在于将二进制编码转换为相应的独热码(one-hot),如101的3位二进制编码作为输入就会被转换成00100000的8位独热码作为输出。因而该元件得名译码器。

同样,在具体使用中选中时,同样有相应的Selection界面,其中对选择位宽,使能相关均可以设置。

我们可以发现,译码器与多路选择器不同之处有两点:

-

除选择信号外,多路选择器是多输入,单输出,输出取决于输入与选择信号,译码器则是无输入,多输出,输出模式仅取决于选择信号。

-

译码器输出位宽每个信号仅一位,多路选择器可以有多位。

因此在之后的组合电路设计中,我们需要仔细思考,在合适的地方使用合适的部件。

相关属性的详细介绍请参考Logisim > 应用与挑战 > logisim 属性栏相关含义介绍

应用中的多路选择器、译码器和多路分配器

答题电路

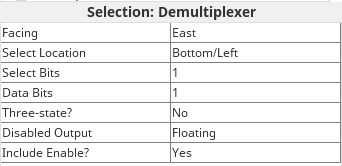

如下图所示,这是一个电视节目中使用的选择题问答电路,主持人出题后,选手通过输入一个2位二进制数来进行答题。选手输入的二进制数与答题选项对应关系见图内"Options"所示。

电路下半部分用来给观众显示选手的选项。上半部分表示选手选择的答案是否正确,LED亮表示正确,灭则错误,图中情况表示正确答案为B。电路中隐去了一些细节,请选择相应类型的部件填至图示空缺位置,使其能够按前文所述工作。

提示:可以打开Logisim查看相关部件功能

1处应该填入的元件为

答案:B. MUX

2处应该填入的元件为

答案:A. Decd

本题要理解这个答题电路的工作逻辑。正如题干描述,上方的电路是为了判定选手答案是否正确,首先要辨别上方电路的右侧是输入,左侧是输出,下方是选择信号;右侧的四个输入是比赛中的出题人提前设置好的,上图显示的是B位置为1,其他位置为0,其含义就是B是正确答案,那么下面的选择信号将会选择这四个位置的一个信号作为输出,如果选择信号选到了B位置,那么输出也为1,表现为LED灯亮,题目答对,如果选择了其他位置的信号,由于其他位置都是0,那么输出也为0,LED灯不亮,回答错误,因此很明显1位置应该填入多路选择器,选择B. MUX。

对于下方的电路,就更容易了,我们发现2位置只有下方的选择信号输入,而输出都是四个1位信号,很明显只能选择译码器。而其中的逻辑如何?题目描述了下方的电路用来显示选手的答案,那么显然将选手的2位选择信号译为独热码输出即可,右侧的四个输出只会有一个信号为1,这就是选手选择的选项,而其他信号均为0,2处填入A. Decd

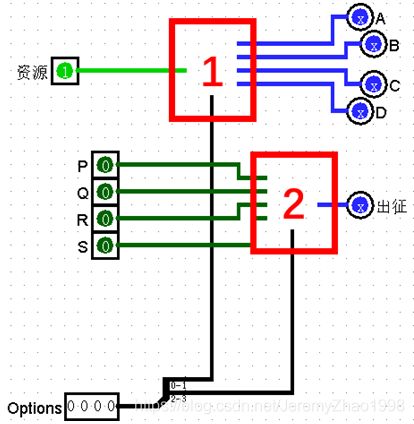

战争游戏

如下图所示,这是一个战争发展类游戏,一个玩家在获得资源后,需要选择升级ABCD四件装备中的一件,而为了获得资源,又需要派出PQRS四名将军中的一名。玩家的选择通过一个四位二进制数表示(如下图),现隐去了一些细节,需要你来补充完整,使得其能攻城掠地。

提示:可以打开Logisim查看相关部件功能

1处应该填入的元件为

答案:C. DMX

2处应该填入的元件为

答案:B. MUX

本题仅从输入输出关系就可以判定得到答案:1位置处有1个输入信号,有2位选择信号和4个输出信号,显然应该是多路分配器DMX;而2位置处有1个输出信号,有2位选择信号和4个输入信号,显然应该是多路选择器MUX。

根据题目给出的逻辑,在1处玩家实现的是用资源选择一个装备来升级,那么选择信号用来选择一路位置让资源信号输出,而资源信号为1时对应位置的装备输出才会为1;在2处实现的是选择一位将军出征,那么2位选择信号所选的是左侧四个将军输入信号,所选位置输出到右侧,当所选的将军信号为1时右侧出征信号才会为1.

牢记这些Plexers的特点:多路选择器的选择信号选左侧多个输入的一个作为输出,多路分配器的选择信号选右侧多个输出路径的其中一路,将左侧唯一的输入信号输出到该路。

逻辑移位器

下图电路是一个16位左移逻辑移位器,左侧输入端口输入被移位的数字,下方输入端口输入要移动的位数,右侧输出端口输出移位后的数字。请选择放入图中方框中的元件,使其能够按前文所述工作

答案:C. DMX

仍旧通过输入输出特点,我们可以发现图中的方框每一个都是1路输入信号,1位选择信号和2路输出信号,因此选择多路分配器DMX。

观察整个左移逻辑移位器,我们可以分析出其逻辑:从最左边开始观察,最左侧的多路分配器,其选择信号是要移位数4位输入的第0位,其含义是“是否要左移1位”,这个多路分配器的两路输出,上面一路原封不动地传出去,下面一路经过了一对耦合的Splitter,而右侧Splitter的最上端是常数0,这对耦合的Splitter作用即为左移1位,移位后最末位应当是0。如果输入的移位数第0位是0,表明不需要移动1位,那么待移位数据从多路分配器上方的路径输出,下方的路径输出全0,两路数据作或运算后最终输出的是不变的待移位数据到下一级;如果输入的移位数第0位是1,表明需要移动1位,那么待移位数据从多路分配器下方的路径输出经过耦合的Splitter完成了移动1位,上方的路径输出全0,两路数据作或运算后最终输出的是待移位数据左移一位,传入下一级。

后面的每一级和第一级逻辑相似,选择信号对应的位数表明“是否需要左移若干位”,然后经过耦合的Splitter进行移位或者直接输出,每一级只负责移动1, 2, 4, 8位,只需要四级就可以完成移动0-15范围内的任意位数。该设计仅用常数时间就可以完成左移若干位,而且使用了最少的元件,设计极为巧妙。

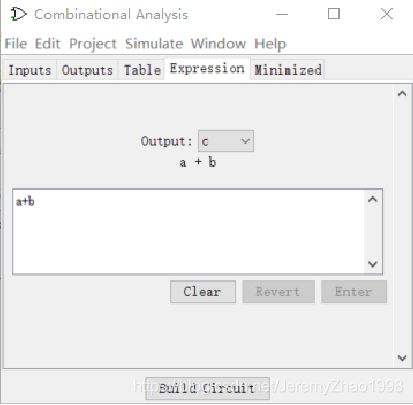

利用Logisim进行组合逻辑分析

Logisim的组合逻辑功能

Logisim中具有逻辑分析的功能,可以实现组合电路,真值表,布尔表达式三者间的两两转换,熟练使用组合逻辑分析功能,能在电路分析,以及根据布尔表达式或真值表迅速生成相应的组合电路,提供巨大的便利。

打开组合逻辑分析模块的方式:

- Window栏目下的Combinational Analysis

- Project栏目下的Analyze Circuit

组合逻辑分析模块,可根据逻辑表达式得到相应的真值表。我们也可以通过输入真值表,再产生相应的表达式,或者产生相应的电路。其中真值表的选值有:0,1,x。

并且在生成电路时,我们也可以勾选下列生成电路的附加约束:

- Use Two-Input Gates Only 只使用二输入门电路

- Use NAND Gates Only 只使用与非门

如上两图,即是要求只使用二输入门电路,只使用与非门所形成的或操作。

可以观察到,两者形成的电路是不一样的,但是在从我们使用逻辑分析模块生成电路的目的来看,我们只使用该电路的输入输出端口,而不需要考虑中间的过程。

思考题:现实生活中的实际电路都是用与非门实现的,为什么这么做?

作者:well xiong

链接:https://www.zhihu.com/question/38788129/answer/78415573

来源:知乎

著作权归作者所有。商业转载请联系作者获得授权,非商业转载请注明出处。谢邀,从理论上来说,这是一个非常合理的做法,并不过时。

理由1:与门的基础性,单纯用与非门可以实现任意逻辑表达式,而用与门就不行,没有取反因子。

理由2:与非门的经济性,在集成电路中,与非门和或非门是仅次于非门的第二简单的门,现在的数字电路基本都是用cmos实现,就是用互补的pmos和nmos实现组合逻辑门。非门(inv)是1个pmos+1个nmos,2输入与非门(nand2)和2输入或非门(nor2)都是2个pmos+2个nmos,而2输入与门(and2)和2输入或门(or2)则是在nand2和nor2后面再接inv得到,需要3个pmos和3个nmos,从资源的角度来说,and和or反而不如nand和nor。

理由3:与非门比或非门性能好,cmos工艺中pmos的导通能力比nmos差,对比nand2和nor2的结构,可以发现nand2中pmos是并联,nmos是串联,所以性能差的单个pmos输出“1”的能力恰好匹敌2个串联nmos输出“0的”能力,而nor2则反过来,pmos串联,nmos并联,对于导通能力差的pmos来说是雪上加霜,通常需要大幅度增加nor2中的pmos的宽度才能和nmos匹敌,但是mos管尺寸的增加会占用更多的面积且造成更大的寄生电容。总之与非门,不管是几输入,都比和其对称的或非门要更优秀。

从以上几点可以看到,nand确实是有资格作为表达式的终极化简因子的,在手工设计电路时,如果可以的话,工程师是倾向于用与非门的,但并不是说对于一个确定的组合逻辑,全部使用与非门来凑就是最优,比如说一个nor2无论如何也比用一个nand2加3个inv要好。

实际工程中,大规模数字逻辑的最佳电路实现是交给软件来做的,这个过程被称为综合(synthesis)。发布于 2015-12-25

数字电路基础课程教学中,为什么总是要把逻辑式化简为与非-与非式,并在实际电路中用与非门实现? - well xiong的回答 - 知乎 https://www.zhihu.com/question/38788129/answer/78415573

分析复杂电路

等价电路

给出逻辑表达式 Y=B C + A ~C,请选出下面与该表达式含义相同的组合电路

| A |  |

|---|---|

| B |  |

| C |  |

| D |  |

答案:A、B、C、D

首先明确待实现表达式:Y = (B & C) | (A & ~C),将各选项的电路书写为表达式,进行化简后与原表达式对比即可知是否等价

A项,电路就是明确的 Y = (B & C) | (A & ~C),是原表达式的直接实现。

B项,Y = (A & ~B & ~C) | (A & B & ~C) | (~A & B & C) | (A & B & C),可以发现将前两个或项合并,后两个或项合并,(A & ~B & ~C) | (A & B & ~C) = (A & ~C);(~A & B & C) | (A & B & C) = (B & C),就有 Y = (A & ~C) | (B & C),与原表达式等价。事实上,B项所绘制的电路是由原表达式真值表直接写出的表达式。

C项,Y = ~(~A | B | C) | ~(~A | ~B | C) | (~A & B & C) | (A & B & C),可以发现C项和B项是非常相似的,整体结构是一样的,只是将B项的前两个或项中,与运算变成了或非运算,并将参与运算的三个信号取反,这一改变是等价的(德摩根律),即~(~A | B | C) = (A & ~B & ~C);~(~A | ~B | C) = (A & B & ~C),因此C项的电路与B项等价,也与原表达式等价。

D项,Y = (A | C) & (B | ~C),由分配律知道 Y = ((A | C) & B) | ((A | C) & ~C) = (A & B | B & C) | (A & ~C | C & ~C) = A & B | B & C | A & ~C = B & C | A & ~C,同样与原表达式等价。

实际上本题的所有电路都是可以由Logisim自动生成的,Logisim内置了自动的逻辑运算,可以实现电路-真值表-逻辑表达式的两两转换,将原表达式输入到Logisim的分析栏中可以找到以上的电路。

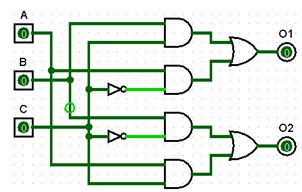

电路功能分析

请分析下图所示电路的逻辑功能

A. SWAP

B. 全加器

C. 全减器

答案:A. SWAP

刚刚完成上一小节的任务我们就可以发现这一电路非常熟悉,就是我们刚刚完成的SWAP交换电路——分析真值表就可以知道,当C为0时,O1输出A,O2输出B,而当C为1时,O1输出B,O2输出A,将AB输入交换。

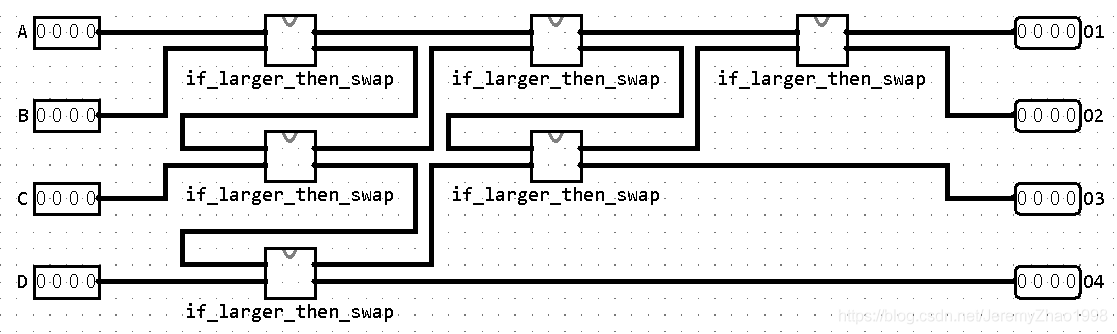

排序电路

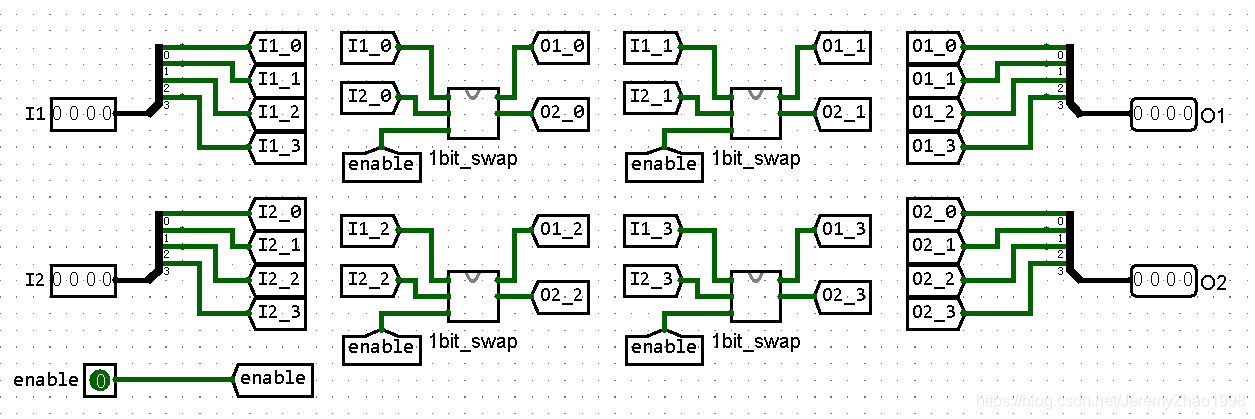

在前面的学习过程中,我们搭建了一个1位的swap电路。现在需要我们使用之前的1位swap电路来搭建一个4位4输入的排序电路。

先使用1位的swap搭建4位的swap,再使用4位的swap模块和Logisim内置的comparator元件搭建排序电路(请不要使用Plexers类元件)

- 功能描述:该电路具有4个4位的二进制数字作为输入和4个4位的二进制数字作为输出。它的功能是,将4个输入的二进制数字进行排序,从上往下数第一个输出端口输出的是4个数字中最小的,第二个输出端口输出的是第二小的,以此类推。

- 输入: A,B,C,D(4bit)

- 输出: #1,#2,#3,#4(4bit)(#1对应第一个输出端口,以此类推)

- 文件内 1 位swap模块名: 1bit_swap

- 文件内 4 位swap模块名: 4bit_swap

- 文件内 排序电路模块名: 4bit_sort

- Hint:所有的二进制数字均看做是无符号的

答案:(不唯一,仅供参考)如下图

工程一共含有四个电路,其中顶层电路为4bit_sort,其余为子电路,如下:

最底层的子电路是1bit_swap,实现两个一位信号的交换,有使能端口(上一节的swap电路),如下:

向上一层,按照题目所述要求,利用1bit_swap构建了4bit_swap,实现带有使能端的4位输入数据交换。在下面的设计中,使用了Tunnel来简化连线,其中的逻辑很简单,利用四个1bit_swap分别交换输入的四位即可:

再向上一层,原本要进入排序的逻辑,但我们发现再排序中,我们会频繁使用到的操作是“比较两个数,如果前者大于后者则将两者交换”,这会用到计算逻辑Comparator和我们刚刚设计的4bit_swap,他们的组合频繁出现的话,考虑讲二者封装称为新的一层子电路,命名为if_larger_then_swap,两个输入如果前者大于后者,则换位输出,否则原位输出,如下:

最后的顶层就是我们需要的排序电路了。由于只有四个输入,各种排序算法所需的元件数量相差不大,这里就采用了最简单的逻辑冒泡排序(bubble-sort),每一轮将前一元素与后一元素对比,前者大则交换,这样会使最大元素沉到底部,如此往复进行三轮即可排好顺序,而每一轮都可以不用判定最底部的元素,因此一共只需要6个if_larger_than_swap逻辑,如下图:

(请注意:由于笔者没有权限,上面的电路结构并未经过课程组给出的官方测试,其正确性无法保证,仅供参考。)