AMBA 系列之 APB 协议

目录

1、简介

2、端口说明(Ports)

3、状态机(FSM)

4、传输时序(Timing)

4.1、Write

4.1.1、Write transfer with no wait states

4.1.2、Write transfer with wait states

4.2、Read

4.2.1、Read transfer with no wait states

4.2.2、Read transfer with wait states

4.3、Error Respond

4.3.1、Error response Write transfer

4.3.2、Error response Read transfer

4.3.4、Mapping of PSLVERR

1、简介

APB(Advance Peripheral Bus)是AMBA总线的一部分,从1998年第一版至今共有3个版本。

AMBA 2 APB:定义最基本的信号 interface, 读写 transfer, APB bridge, APB slave.

AMBA 3 APB:增加定义信号 PREADY, PSLVERR 来完成对 wait state 和 Error reporting 的功能。

AMBA 4 APB:增加定义信号 PPROT, PSTRB 来支持 secure, supervisor 和 sparse data transfer 的功能。

APB接口用在低带宽和不需要高性能总线的外围设备上。 APB是非流水线结构,所有的信号仅与时钟上升沿相关,这样就可以简化APB外围设备的设计流程,每个传输至少耗用两个周期。APB可以与AMBA高级高性能总线(AHB-Lite) 和AMBA 高级可扩展接口 (AXI)连接;

APB主要用于低带宽的周边外设之间的连接,例如UART、1284等,它的总线架构不像AHB支持多个主模块,在APB里面唯一的主模块就是APB 桥。其特性包括:两个时钟周期传输;无需等待周期和回应信号;控制逻辑简单,只有四个控制信号。APB上的传输可以用状态图来说明;

2、端口说明(Ports)

| 信号名 | 来源 | 说明 |

|---|---|---|

| PCLK | 时钟源 | 系统时钟,传输发生在上升沿 |

| PRESETn | 复位源 | 复位信号,低使能 |

| PADDR | APB桥 | 地址信号,最高可达32位 |

| PSELx | APB桥 | 由APB bridge产生的信号,针对每一个Peripheral Bus Slave片选信号,表示x从机是否被选中 |

| PENABLE | APB桥 | 使能信号,标记传输使能 |

| PWRITE | APB桥 | 读/写控制信号,高位写,低为读 |

| PWDATA | APB桥 | 写数据 |

| PREADY | 从机 | 标记从机是否已将数据发送到总线,高为ready |

| PRDATA | 从机 | 读数据 |

| PSLVERR | 从机 | 故障信号,高为发生故障 |

在APB总线中分别有PWDATA和PRDATA,但这并不表示它支持同时读写,

3、状态机(FSM)

APB 的状态机定义如下:

IDLE:这个是 APB 的默认状态,也就是没有传输时候的状态;

SETUP:当需要进行一个传输的时候,APB 首先进入这个状态;PSELx 信号首先拉高;总线仅仅在 SETUP 状态停留一个时钟周期,然后接着在下一个时钟的上升沿进入 ACCESS 状态;

ACESS:在 SETUP 状态转换到 ACCESS,PENABLE 信号被拉高;在 SETUP 状态转换到 ACCESS 状态这段时间里,address,write,select 和 write data 信号必须保持稳定;

处于 ACESS 状态下,如果 PREADY 为 0,会让其继续处于 ACCESS 状态;否则,PREADY 为 1,如果还有传输则再次进入 SETUP -> ACCESS ,如果没有传输,直接回到 IDLE;

4、传输时序(Timing)

4.1、Write

写传输分为不带等待信号的写,和带等待信号的写:

4.1.1、Write transfer with no wait states

这种是不带等待信号的写传输,如下所示:

T1 时刻 APB 将地址信息 PADDR 和写的数据 PWDATA 准备好,拉高 PWRITE 表示进入写,同时拉高 PSEL,从 IDLE 进入 SETUP

T2 时刻也就是下一个时钟周期拉高 PENABLE,使得状态进入 ACCESS

T3 时刻检测到 PREADY 被拉高,也就是说 Slave 已经正确接收到数据,传输完成;PENABLE 拉低,PSEL 拉低

4.1.2、Write transfer with wait states

这种是带等待信号的写传输,如下所示:

T1 时刻 APB 将地址信息 PADDR 和写的数据 PWDATA 准备好,同时拉高 PSEL,从 IDLE 进入 SETUP

T2 时刻也就是下一个时钟周期拉高 PENABLE,使得状态进入 ACCESS

T3 时刻检测到 PREADY 为 0,也就是说 Slave 还没有接收完数据,所以在此刻,下面信号必须保持,以便 Slave 能够继续采样:

- PADDR 地址信号

- PWRITE 数据方向信号

- PSEL 片选信号

- PENABLE 使能信号

- PWDATA 数据

T4 时刻 PREADY 依然 为 0,所以还是保持不变

T5 时刻,PREADY 为 1,说明 Slave 已经正确接收到数据,传输完成;PENABLE 拉低,PSEL 拉低

注意:即便是传输结束了,Address 和 data 信号也不会立即改变,直到下一次传输才会刷新新的地址和数据信号,这样做的原因是减少功耗;

4.2、Read

读数据和写的流程几乎差不多,也分为了等待和非等待

4.2.1、Read transfer with no wait states

同非等待写一样,图示如下:

T1 时刻 APB 将地址信息 PADDR 准备好,拉低 PWRITE 表示进入读,同时拉高 PSEL,从 IDLE 进入 SETUP

T2 时刻也就是下一个时钟周期拉高 PENABLE,使得状态进入 ACCESS

T3 时刻检测到 PREADY 被拉高,也就是说 Slave 已经完成收据发送,PRDATA 上就是来自 Slave 的数据,传输完成;PENABLE 拉低,PSEL 拉低

4.2.2、Read transfer with wait states

加等待的读时序如下:

时序过程和上述一样,只不过 PREADY 被拉低了两个周期,真正从 Slave 读的数据到 T5 时刻才真正有效;这里不在多说;

4.3、Error Respond

在读和写的过程,可能出现错误,错误通过 PSLVERR 信号来指明;

APB外围设备不要求必须支持PSLVERR引脚,当不使用该引脚时,应被置低

4.3.1、Error response Write transfer

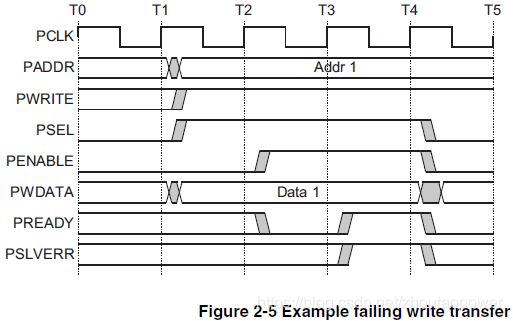

下面这个是写失败后的时序:

可以看到,在写失败后,PSLERR 信号被拉高了

4.3.2、Error response Read transfer

下面这个是读失败后的时序:

读失败后,PRDATA 上的数据不再有效

4.3.4、Mapping of PSLVERR

如果发生了失败的情况 PSLVERR 信号会反馈到桥接的 AHB/AXI 总线上的回复信号上

参考文献:

http://blog.sina.com.cn/s/blog_13f7886010102x4t3.html

https://blog.csdn.net/cy413026/article/details/90751756