HDL抽象等级 仿真模型 网表 delay speicfy与sdf

1.HDL 硬件描述语言 抽象分级

HDL这里主要说verilog 在描述硬件电路时分为三个抽象级别

行为级模型:主要用于test bench,着重系统行为和算法,不在于电路实现,不可综合(常用描述有initial,fork/join,task,function,repeat,wait,event,while等)。

•RTL级模型:主要用于集成电路的设计(ASIC,SOC或FPGA等),重点在于电路实现,在于如何在timing,area和power中做出平衡。可综合出门级电路。(常用描述有module,always,case,assign等)。

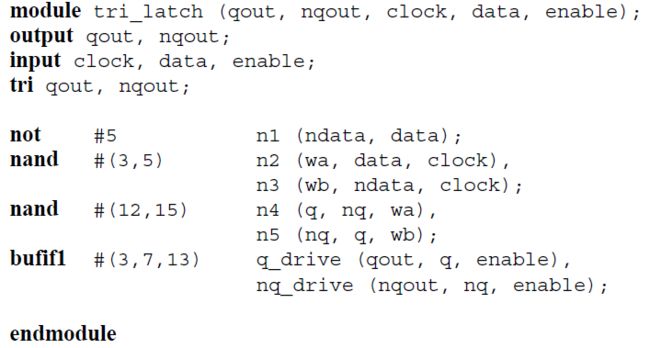

•门级模型:主要用于后端的物理实现,它是实际电路的逻辑实现,通常由RTL级模型综合出来的,(常用描述有逻辑门,UDP,线网等),门级模型还用于开发小规模的元件。

我们常见的门级模型的verilog有 stdcell的仿真模型(即 .v文件), mem的仿真模型,第三方IP的gate_level级仿真模型【因为第三方IP常常会提供rtl级和gate-level级两种仿真模型。RTL级仿真模型用来功能仿真,gate-level用来前防(zero-delay)和后防(带延时仿真)】。

门级模型 的verilog module都是用 和工艺无关的最小单元来描述电路。比如常用的

not

and

or

xor

buff

bufif1

bufif0

notif0

notif0是看不到寄存器的,因为寄存器也是由这些基本单元构成的。下面两张图就是简单的门级module的例子。其实翻开stdcell的verilog模型,代码也是和下面一样的。

module and4(

output out,

input a, b, c, d);

specify

(a,b *> out) = 2.5 ;

(c,d *> out) = 3.5 ;

endspecify

wire an1, an2 ;

and (an1, a, b);

and (an2, c, d);

and (out, an1, an2);

endmodule2.仿真中怎么带延时信息

仿真带延时信息就需要 verilog的module中有specify--end specify,有了specify sdf才能正确反标。sdf只是后端收完timing之后 更准确的延迟信息。反标就是反标在有specify的地方。sdf与specify的延迟不一致时以sdf为准,没有sdf的地方使用specify的延迟信息。

3.为什么我们常写的RTL代码没有specify

这是因为RTL都是寄存器级的描述,而寄存器并不是最小的电路单元,很难将延时下到pin上,而且也不统一,比如说一个逻辑与“&&”,只能看到信号而看不到pin,相当于每一个“&&” 都要写一遍specify。寄存器也是一样的 都是同样的DFF,rtl写起来千差万别,不好加specify。 当我们先把RTL级代码翻译成gate_level的verilog,然后再map到标准单元库,最终输出map到标准单元库的netlist。然后netlist调用stdcell的gate-level级仿真模型,就可以带上所有的延迟信息。

所以我们看到的netlist是需要调用stdcell的仿真模型。而所有的非net延迟信息都包含在了stdcell的module中。

综合netlist可以说并不是一个gate-level的代码,它只是包含了stdcell的例化和连线关系的一个描述文件,stdcell的仿真模型才认为是gate-level的代码。

第三方提供的gate-level代码 同时包含了netlist(常常是不可综合的)和调用的gate-level级cell module,这些cell不是工艺相关的stdcell,而是通用的cell描述。

可参考另一篇文章:

sdf与timingCheck和后仿真_cy413026的博客-CSDN博客