DC LAB8 & SDC约束 & 四种时序路径分析

DC LAB

- 1.启动DC

- 2.读入设计

- 3. 查看所有违例的约束报告

-

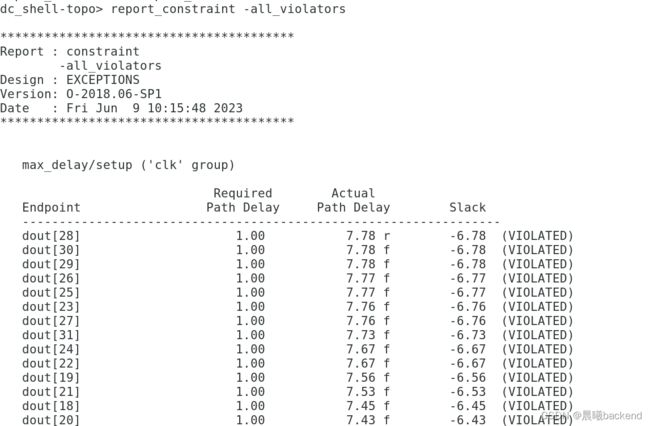

- 3.1 report_constraint -all_violators (alias rc)

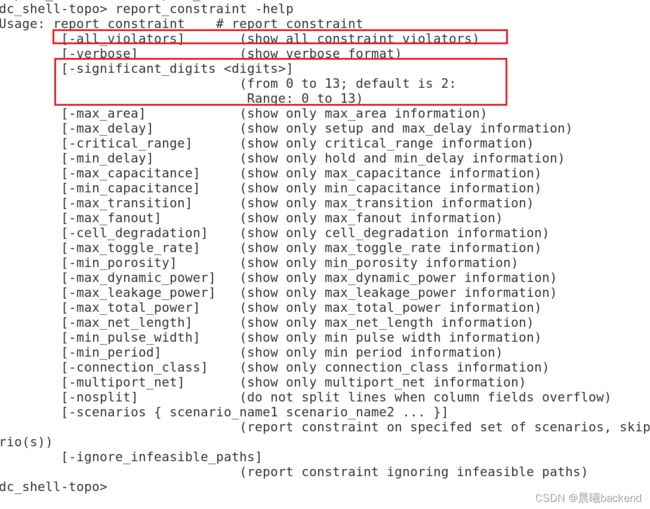

- 3.2 view report_constraint -all_violators -verbose -significant_digits 4 (打印详细报告)

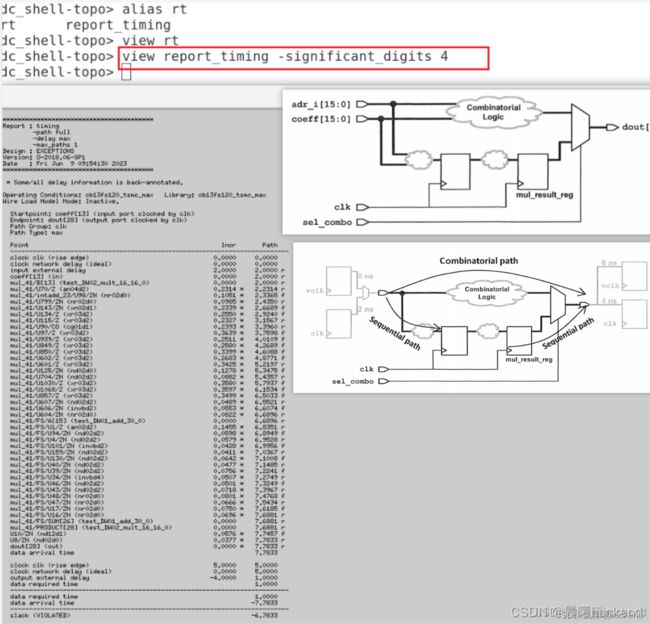

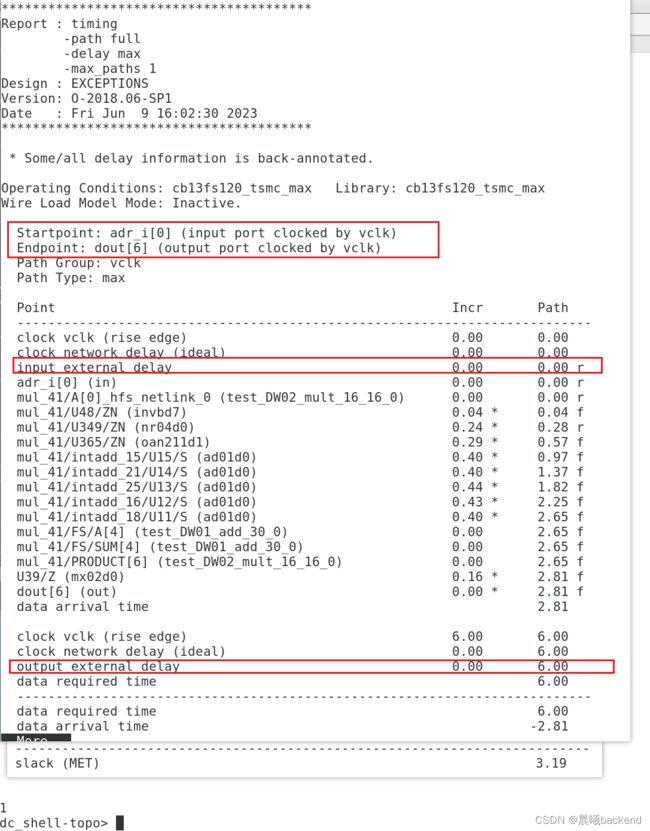

- 4.查看时序报告 report_timing -significant_digits 4

- 5. 约束组合逻辑(adr_i/coff到comb logic到dout)

-

- 5.1 创建虚拟时钟

-

- 5.1.1 set_input_delay 用法

- 5.2 创建虚拟时钟vclk后再report_timing

-

- 5.2.1 组合逻辑约束,clk与vclk logically_exclusive(设置`clk-->comb-->vclk`, `vclk-->comb-->clk`为false)

- 5.2.2 设置`clk与vclk llogically_exclusive`后再去report_timing -group vclk -significant_digits 4

- 5.3 查看clk的timing, report_timing -group clk -significant_digits 4

-

- 5.3.1 组合逻辑约束,`设置clk--->comb-->clk为false path`

- 5.3.2 设置`clk--->comb-->clk为false path` 后再report_timing -from $in_ports -to [all_outputs]

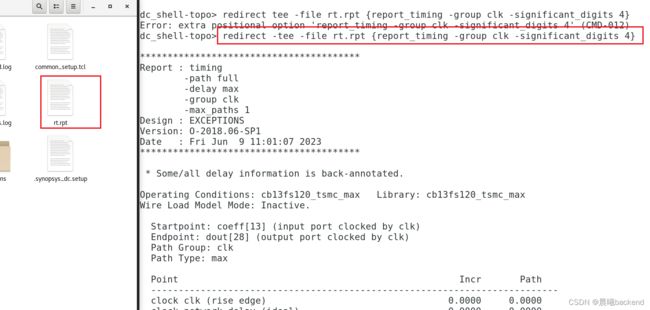

- 6. 查看clk group timing ,report_timing -group clk

-

- 6.1 设置`mul_result_reg*/D `(reg2reg)多周期检查setup `set_multicycle_path `

-

- 6.1.1 设置完setup,多周期再检查reg2reg(`coeff_q_reg_14_ ` to `mul_result_reg_31_`)的setup

- 6.2 检查hold(肯定violation,多周期设置没设置hold,只设置了setup,hold现在在5ns检查太严格了)

-

- 6.2.1 设置 `mul_result_reg*/D ` (reg2reg)多周期检查hold

- 6.2.2 设置hold多周期后再检查

- 7.report_constraint -all_violators

- 8.四种时序路径总结

-

- 8.1 in2reg

- 8.2 reg2reg

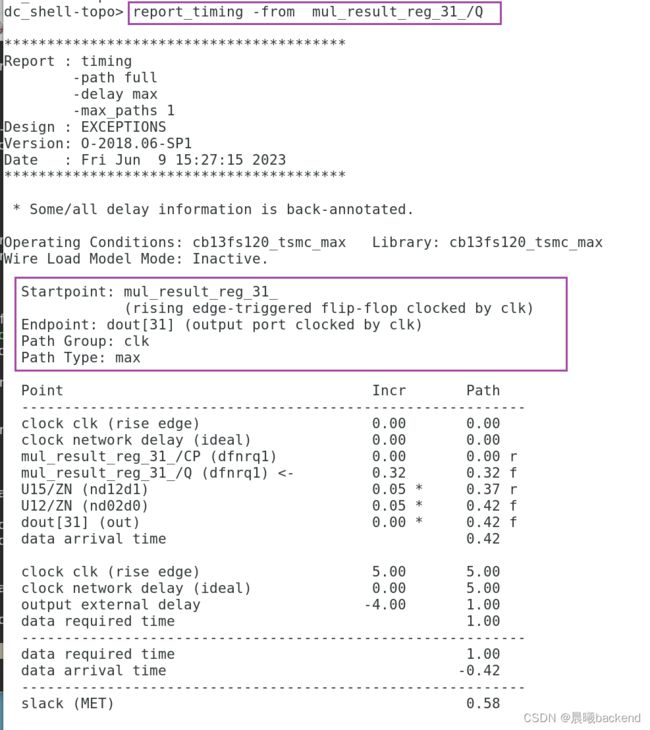

- 8.3 reg2out

- 8.4 in2out

-

- 8.4.1 in2out`(adr_i[0]-->dout[6]) `demo

- 8.4.2 in2out`(coeff[5]-->dout[6]) `demo

- 9.打印所有port、cells、pins

-

- get_ports

- get_cells

- get_pins

1.启动DC

dc_shell-t -64bit -topo

2.读入设计

read_ddc EXCEPTIONS.ddc

current_design EXCEPTIONS

link

3. 查看所有违例的约束报告

3.1 report_constraint -all_violators (alias rc)

3.2 view report_constraint -all_violators -verbose -significant_digits 4 (打印详细报告)

4.查看时序报告 report_timing -significant_digits 4

- 组合逻辑延时是7.7833-2=5.7833

- 对于adr_i/coff到comb logic到dout,

(in2out,应该定义虚拟时钟vclk),将clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk,这三条设置false - 上图是adr_i/coff到comb logic到dout时序路径,有vio(clk–>input delay 2ns -->coff --> comb logic 5.7833ns --> dout) 这条路径应设置false path

5. 约束组合逻辑(adr_i/coff到comb logic到dout)

- To accomplish this,the combinatorial paths will be constrained using a new virtual clock which you will call vclk.

- The sequential paths are already constrained using the 5ns design clock clk,and input and output delays of 2ns and 4ns,respectively.

- The following schematic illustrates this concept (note that the two input ports, adr_ i and coeff,are collapsed into one port here to simplify the schematic):

5.1 创建虚拟时钟

create_clock -name vclk -period 6

set in_ports [get_ports "coeff* adr_i*"]

set_input_delay 0 -clock vclk -add_delay $in_ports

set_output_delay 0 -clock vclk -add_delay [all_outputs]

5.1.1 set_input_delay 用法

dc_shell-topo> set_input_delay -help

Usage: set_input_delay # set input_delay

[-clock clock_name] (relative clock)

[-clock_fall] (delay is relative to falling edge of clock)

[-level_sensitive] (delay is from level-sensitive latch)

[-rise] (specifies rising delay)

[-fall] (specifies falling delay)

[-max] (specifies maximum delay)

[-min] (specifies minimum delay)

[-add_delay] (don't remove existing input delay)

[-network_latency_included]

(specifies that clock_network_latency is included)

[-source_latency_included]

(specifies that clock_source_latency is included)

[-reference_pin pin_list]

(list of pins)

delay_value (path delay)

port_pin_list (list of ports and/or pins)

5.2 创建虚拟时钟vclk后再report_timing

view report_timing -group vclk -significant_digits 4

- 组合逻辑的路径应该只有vclk约束,设置

clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk为false - The launch clock is vclk and the capture clock is vclk . This is not correct!

- The combinatorial paths should be constrained only by vclk . The two clocks should not interact.

5.2.1 组合逻辑约束,clk与vclk logically_exclusive(设置clk-->comb-->vclk, vclk-->comb-->clk为false)

- 对于

clk-->comb-->clk只有手动设置false了 (5.3.1)

#两种时钟,四种组合,约束后只能从clk到clk或者vclk到vclk

#

set_clock_group -name false_grp1 -logically_exclusive -group clk -group vclk

# Altenatively:

#

# set_false_path -from [get_clocks clk] -to [get_clocks vclk]

# set_false_path -from [get_clocks vclk] -to [get_clocks clk]

5.2.2 设置clk与vclk llogically_exclusive后再去report_timing -group vclk -significant_digits 4

- 组合逻辑延时 5.7833ns

5.3 查看clk的timing, report_timing -group clk -significant_digits 4

- 这里不会显示

vclk-->clk,因为前面(5.2.1)设置了logically exclusive - 只会显示

clk-->clk

- 上图是addi/coff到comb到dout的时序路径,有vio(clk–>input delay 2ns -->coff --> comb logic 5.7833ns --> dout) 这条路径设置false path ,

- 这条路径用虚拟时钟vclk检查

- 前面5.2.1虽然设置了logic exclusive(

clk-->comb-->vclk,vclk-->comb-->clk为false),但是clk—>comb–>clk还是得手动去 false

5.3.1 组合逻辑约束,设置clk--->comb-->clk为false path

set_false_path -from [get_clocks clk] \

-through $in_ports \

-through [all_outputs] -to [get_clocks clk]

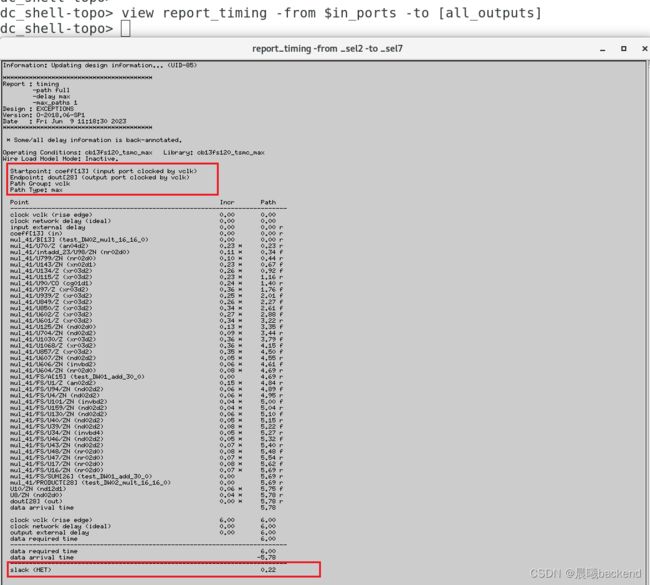

5.3.2 设置clk--->comb-->clk为false path 后再report_timing -from $in_ports -to [all_outputs]

- 由于设置

clk-->comb-->clk,clk-->comb-->vclk,vclk-->comb-->clk为false,故只会显示vclk–>vcomb–>clk这条时序路径

6. 查看clk group timing ,report_timing -group clk

- 从下图可以看出reg2reg 中间组合逻辑延时为9.1589ns,Tcq=0.4383

- 组合逻辑介于一个周期和两个周期之间,所以设置multicycle path(setup设置N,hold则对应N-1)

两个寄存器间的Tcq+Tcomb = 9.5943,单周期检查太严格,故设置多周期检查,setup在第二个周期在检查

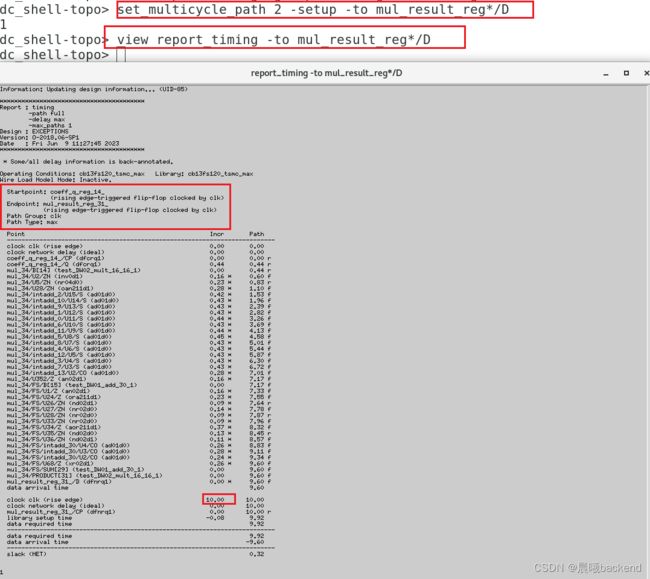

6.1 设置mul_result_reg*/D (reg2reg)多周期检查setup set_multicycle_path

##若setup设置N,hold 对应设置为N-1

set_multicycle_path 2 -setup -to mul_result_reg*/D

6.1.1 设置完setup,多周期再检查reg2reg(coeff_q_reg_14_ to mul_result_reg_31_)的setup

- 由于只设置了setup,所以这里检查setup的 comb max delay是没有问题的

- 但是检查hold,就过于严苛了

6.2 检查hold(肯定violation,多周期设置没设置hold,只设置了setup,hold现在在5ns检查太严格了)

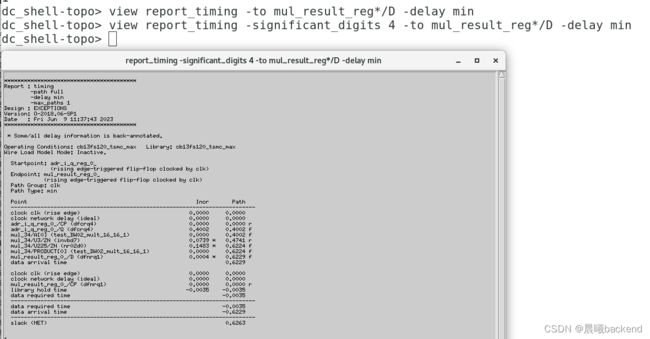

6.2.1 设置 mul_result_reg*/D (reg2reg)多周期检查hold

set_multicycle_path 1 -hold -t o mul_result_reg*/D

6.2.2 设置hold多周期后再检查

report_timing -significant_digits 4 -to mul_result_reg*/D -delay min

7.report_constraint -all_violators

- 所有timing vio都已经清除完毕了

8.四种时序路径总结

8.1 in2reg

report_timing -group clk

[-add_delay] (don't remove existing input delay)

8.2 reg2reg

- 这里设置了

set_multicycle_path 2 -setup -to mul_result_reg*/D

8.3 reg2out

8.4 in2out

8.4.1 in2out(adr_i[0]-->dout[6]) demo

report_timing -from adr_* -to dout[6]

report_timing -from adr_* -to dout*

8.4.2 in2out(coeff[5]-->dout[6]) demo

report_timing -from coeff* -to dout[6]

report_timing -from coeff[0] -to dout[6]