ICC 图文学习——LAB4:CTS 时钟树综合

时钟树综合的定义:时钟网络从根节点逐渐插入驱动器(buffer、inverter)从而达到其叶节点,按照芯片时钟网络的约束要求产生时钟树的过程。

主要内容:

·完成时钟树的综合CTS(负载平衡,解决DRC问题)和时钟树的平衡优化CTO(减少skewlatency)

·完成non_colck path的时序优化等

·完成时钟树的routing。

LAB4:CTS 时钟树综合

- 1. 打开设计,并检查时钟树

- 2. CTS前的设置和检查

- 3. 时钟树综合

- 4. Post-CTS

- 5. 时钟布线

相关文件的准备:

orca_lib.mw/CEL:

place_opt 放置和扫描插入的设计以Milkway格式保存

scripts/:

cts_setup.tcl 设置CTS选项的脚本

ndr.tcl 指定非默认时钟布线规则命令的脚本

opt_ctrl.tcl 时序和优化控制

1. 打开设计,并检查时钟树

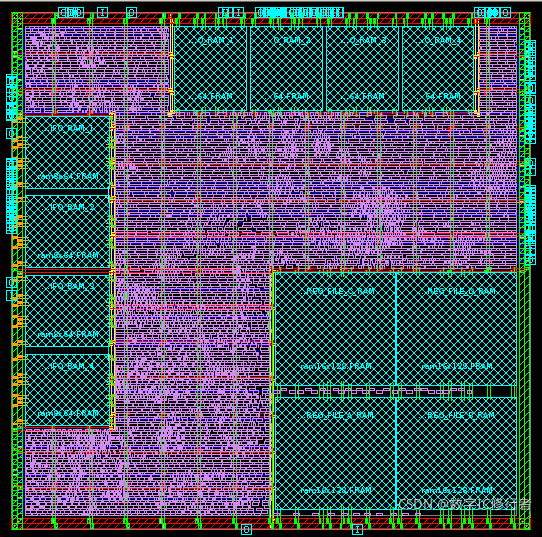

- 在lab4_cts目录下启动ICC GUI,并打开设计库,如下:

open_mw_lib orca_lib.mw

- 复制CEL place_opt,并将其命名为clock_opt,命令如下:

copy_mw_cel -from place_opt -to clock_opt

- 打开 clock_opt 设计

open_mw_cel clock_opt

- 检查时钟树的skew、总体情况和timing 违反

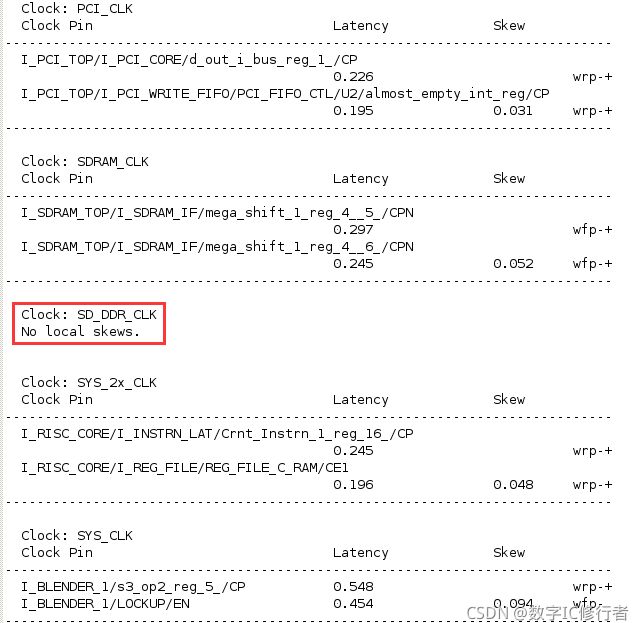

a. 检查时钟树的skew属性:

report_clock -skew -attributes

report_clock_tree -summary

该命令可以查看时钟树所驱动的sinks,不同时钟的skew、时钟树的最长路径(最大延迟)。

该命令可以查看时钟树所驱动的sinks,不同时钟的skew、时钟树的最长路径(最大延迟)。

c. 检查是否存在setup 违反

view report_constraint -all

从图中可以看出,该设计存在hold违反,因为hold违反在CTS后才进行修复。

- 通过GUI查看是否有时序例外的端口

exception pin知识补充:

默认情况下,CTS只会平衡时钟树延迟(最小skew)到 " 停止引脚 " ,停止引脚是顺序单元的时钟引脚。如果有例外的引脚需要平衡,那就需要在CTS前指定好这些例外的引脚,主要讲解如下:

若同一个引脚多次发出set_clock_tree_exception命令,引脚会保持最高优先级的异常,引脚优先顺序如下:

不间断引脚 > 排除引脚 > 浮动引脚 > 停止引脚。现在对它们进行详细介绍,如下:

a. Non_stop pins(不间断引脚)

不间断引脚通常被认为是时钟树端点的引脚,但ICC会穿过它们跟踪寻找真正的端点。驱动生成时钟的时序单元的时钟引脚是隐式不间断引脚。下面关于隐式不间断引脚的介绍:

若时序单元的扇出驱动的是生成时钟(即该时序单元用于分频之用,产生生成时钟),则ICC会将该时序单元的时钟引脚视为隐式不间断引脚,并穿过该时序单元以追踪到真正的时钟树端点,如下图①所示。此外,ICC认为集成门控(ICG)单元的时钟输入引脚是隐式不间断引脚,不用手动对其进行重复设置,如图②。

指定不间断引脚的命令如下:

set_clock_tree_exception -non_stop_pins

b. exclude pins(排除引脚)

排除引脚是从时钟树时序计算和优化中排除的时钟树端点。ICC仅在计算和优化设计规则约束时(DRC)使用排除引脚。

在CTS期间,ICC通过在排除引脚(隐式和显示排除引脚)之前插入 guide buffer 来从时钟树中隔离这些引脚。对于这些引脚,ICC只会执行设计规则(DRC)修复,不会执行skew和latency优化。

指定排除引脚的命令如下:

set_clock_tree_exception -exclude_pins

c. float pins(浮动引脚)

具有特殊插入延迟要求的时钟引脚。于停止引脚类似,但在构建时钟树时会考虑该引脚的内部时钟延迟。工具在计算到该float pins的插入延时时,将把float pin延迟(正或负)添加到计算插入延迟中去。

指定浮动引脚的命令如下:

set_clock_tree_exceptions #有下面不同选项

-float_pins [get_pins pin_list]

-float_pin_max_delay_fall max_delay_fall_value

-float_pin_max_delay_rise max_delay_rise_value

-float_pin_min_delay_fall min_delay_fall_value

-float_pin_min_delay_rise min_delay_rise_value

-float_pin_logic_level logic_level_value

注:如果使用 -float_pins 选项,则必须至少指定一个浮动引脚延迟选项,否则将发生错误。

d. stopt pins(停止引脚)

用于平衡时钟树延迟的时钟端点。在时钟树综合期间,ICC在计算和优化设计规则约束(逻辑DRC)和时钟树时序(skew和latency)时使用stop pins。stop pins也称为sink pins。

指定停止引脚的命令如下:

set_clock_tree_exception-stop_pins

d. dont_touch_subtrees(勿触碰子树)

在某些情况下,希望保留现有时钟树的一部分,需要这样设置。如当两个时钟网络共享多路选择器后面的某些时钟逻辑的一部分时,保留的时钟树的部分称为勿触碰子树。

指定勿触碰子树的命令如下:

set_clock_tree_exception -dont_touch_subtrees

若要删除某个引脚上的dont_touch_subtrees属性,命令如下:

remove_clock_tree_exception -dont_touch_subtrees

以上是关于exception pin知识的介绍,接下来我们将进行lab,实际运用

a. 依次选择 " Layout Window "— "Clock "— " New Interactive CTS Window "。

由上图可以看出,SD_DDR_CLK是一个generated clock,DRAM_CLK是其Master clock,sd_ck作为其source。

b. 按照下图步骤,对SDRAM_CLK进行详细分析。

c. 最大化新打开的窗口,并打开左侧SDRAM_CLK前的 " + " ,选择sdram_clk,可以看到右侧面板出现这个时钟的所有sinks,exception pin都是implicit_exclude_pin。

2. CTS前的设置和检查

- 将所有的引脚例外设置为stop pins,如下:

set_clock_tree_exceptions -stop_pins {I_SDRAM_TOP/I_SDRAM_IF/sd_mux_*/S}

- 设置 target skew

依次选择 " GUI " — "Clock " — "Set Clock Option " ,将target skew设为 0.1 。将target放宽可以提高速度,加快时钟树的合成,默认值是0。

对应的命令如下:

set_clock_tree_options -target_skew 0.1

- 调整post-CTS时序分析和优化的时钟不确定度,本设计将其设置为0.1,如下。

set_clock_uncertainty 0.1 [all_clock]

- 设置时钟树的reference

指定创建CTS的缓冲单元,以提高结果的质量。一般buffer或inverter,它们各有优缺点,一般库里的buffer或inverter都是以CLK或CK开头的,可用通配符查找。本lab缓冲单元的选择如下:

set_clock_tree_references -references {bufbd1 bufbd2 bufbd4 bufbd7 bufbdf}

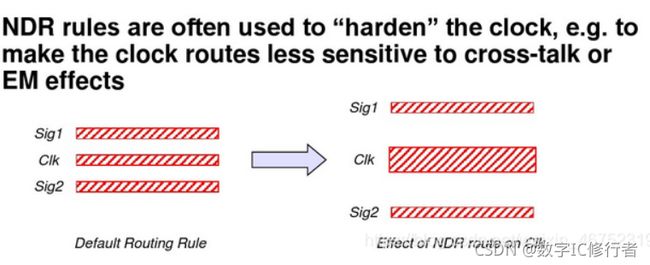

- 设置时钟树的NDR rule。

可以按照下面步骤实现,也可以source脚本

a. 删除之前定义过的NDR(本lab没有该步骤)

remove_routing_rules -all

b. 为时钟线定义双倍线宽、双倍线间距,本lab只定义了双倍线间距

NDR一般指双倍线宽和双倍间距。通常会采用双倍间距加强clock net,避免受到串扰的影响;双倍线宽可以缓解EM问题,如下图:

依次选择 "Layout Window " — " Route "— " Routing Setup " — "Define Routing Rule " — " New ",新建一个NDR。在Rule name中填入名字,Width multiplier 和Spacing multiplier 中均填入2,点击Apply即可创建NDR,如下图:

上面操作相应命令如下:

define_routing_rule clk_rule(your rule name) -default_reference_rule -multiplier_spacing 2 -multiplier_width 2

本lab对双倍间距的定义相关命令如下:

define_routing_rule CLOCK_DOUBLE_SPACING -spacings {METAL3 0.42 METAL4 0.63 METAL5 0.82}

c. 报告定义的NDR规则,验证间距值是否正确指定,如下:

report_routing_rule CLOCK_DOUBLE_SPACING

d.为时钟树布线选择自己定义的NDR和金属层

由于标准单元出pin大部分是M1/M2,如果设置NDR rule ,会导致很多DRC问题,因此,在第一级sinks端使用默认绕线规则进行布线,而采用高层进行时钟信号布线,如下图:

依次选择 "Layout Window " — " Clock "— " Set Clock Tree Options " — "Routing ",如下图:

上面操作对应命令如下:

set_clock_tree_options -routing_rule CLOCK_DOUBLE_SPACING -layer_list {METAL3 METAL5} -use_default_routing_for_sinks 1

- 检查时钟绕线层和用于创建CTS的缓冲单元是否正确定义,如下:

v report_clock_tree -settings

- 进行物理检查,如下:

check_physical_design -stage pre_clock_opt -display

- 设置时钟树延迟计算模式,如下(新版本将不再适用):

set_delay_calculation -clock_arnoldi

- 最后检查时钟树问题,如下:

check_clock_tree

3. 时钟树综合

skew知识补充:

我们把时钟信号到达不同寄存器的时间偏差称为skew。skew是衡量时钟树性能的重要参数,传统CTS的目的就是为了减小skew。

1. 通常根据时钟域以及路径关系,skew可以分为global skew、local skew和 interclock skew,下面将详细介绍它们:

a. global skew:泛指 同一时钟域中任意两个路径的最大skew。如下图所示,注意是任意两条路径,不管是不是timing path,都会算做global skew计算的对象。CTS阶段关注的是global skew,会尽可能的将global skew做小。

b. local skew:指 同一时钟域中任意两个有逻辑关联关系的路径最大skew。如下图所示,必须是存在逻辑关系的path 才会计算local skew,我们在分析timing的时候,更多关注的是local skew。

c. interClock skew:指不同时钟域之间路径的最大skew,如下图所示,

2. 根据clock和data path 的方向,skew又可以分为 positive skew 和 negative skew,如下图所示:

a. 对于positive skew,clock和data path在相同方向上。反之对negative skew来说,clock 和data path在相反方向上。由setup和hold的计算公式可知:

b. 对于positive skew来说,它可以减小T的大小,进而提高了芯片的性能,但使hold更难满足。

c. 对于negative skew来说,它会使hold更容易满足,但却降低芯片的性能。

以上是关于exception pin知识的介绍,接下来我们将进行lab,实际运用

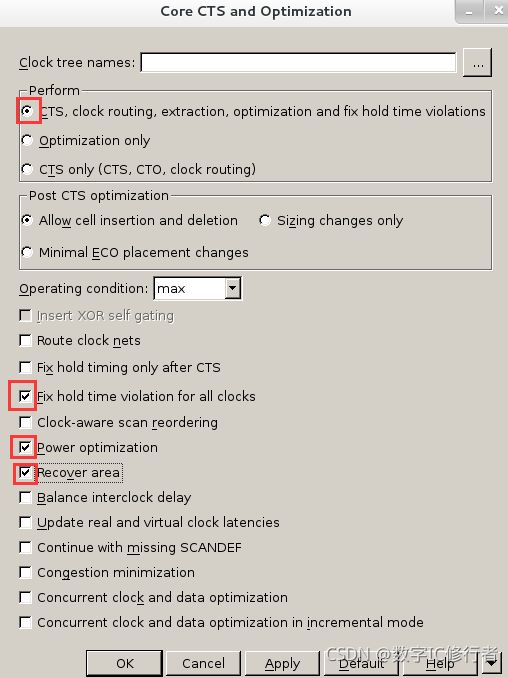

- 时钟树综合,不做任何时序优化或布线

依次选择 "Layout Window " — " Clock "— " Core CTS and Optimization " ,在弹出对话框中。勾选下图两处,只建立时钟树,不进行时钟线布线。

上面操作对应命令如下:

clock_opt -only_cts -no_clock_route

- 查看CTS的 global skew报告,如下:

report_clock_tree -summary

该命令可以查看不同时钟树的名字、时钟树sinks pin的数目、CTS阶段插入的buffer数量和面积、时钟树中所有单元的总数、skew的大小(global skew)、时钟树的最长时钟路径、时钟树所有DRC违反数目等。

- 生成不同的skew报告(local skew),命令如下:

report_clock_timing -type skew -significant_digits 3

- 生成时序报告,主要检查slack是否为正值,如下:

v report_timing

由上图可以发现,从clock network delay(propagated)可知所有时钟网络已设置为传播属性,移除了理想属性,且slack值为正数。

- 查看所有违规报告,如下:

v report_constraint -all

- 保存设计,命令如下:

save_mw_cel -as clock_opt_cts

4. Post-CTS

做完CTS后,由于时钟树已建立,所以需要将时钟网络以及高扇出网络的理想属性移除,设置为传播属性;并开始修复hold违反,下面将进一步进行讲解。

- CTS后,ICC工具会自动移除所有时钟网络的理想属性,设置为传播属性;最好手工设置一下,将它的理想属性移除并去掉其中估计的clock skew部分,如下:

remove_ideal_network [all_fanout -flat -clock_tree]

remove_clock_latency $clk

set_propagated_clock [get_attr $clk sources]

- 重新定义关于clock uncertainty 的定义。如下:

set_clock_uncertainty -setup 1 $clk

set_clock_uncertainty -hold 0.a $clk

- 移除时钟网络的理想属性和sdc中定义的latency后,对时钟树延迟信息进行更新,如下:

update_clock_latency

- 启动hold time 修复:

set_fix_hold [all_clocks]

- 查看质量(QoR)报告

report_qor

- 进行面积范围设置,通过缩小规模,使用正的slack来减缓路径。

set_max_area 0

set physopt_area_critical_range 0.2 #set area critical range

- 提取RC参数,此时互联线延时准确,如下:

extract_rc

注:上一个任务report_timing中,已经隐式的执行了这个RC的提取。

clock_opt -only_psyn -area_recovery -optimize_dft -no_clock_route

注:在timing优化阶段,可以看到MIN DELAY COST 附加列,表示此时也在执行hold time优化。

- 查看报告和所有违规(setup、hold、design rule)

report_qor

report_constraint -all

- 保持设计

save_mw_cel -as clock_opt_psyn

5. 时钟布线

- 进行时钟绕线,如下:

route_zrt_group -all_clock_nets -reuse_existing_global_route true

注:在View Setting 面板中,关闭 Cell 和 Route 目录的子目录N et Type 下的 Power 和Ground 的可见性,可以直观的看到大多数时钟网都打在Metal 3 - Metal 5 上。

- 检查所有约束,确认没有 timing 和 DRC 违反

report_constraint -all

- 保存设计

save_mw_cel -as clock_opt_route

- 报告物理布线信息

report_design -physical

- 查看时钟树的拓扑结构,

可以选择下图序号 1 中的Clock tree ,然后在弹出的窗口中,点击 Reload,最后可以通过点击序号2中对应的level 和勾选序号 3 中的方框,来查看时钟树的拓扑结构。

- 时钟树综合完成,退出ICC

exit