电子综合设计——电子钟

一、设计基本要求:

1、进行24小时制的时、分、秒计时

2、具有手动输入的时间功能调整

3、具有闹钟设置功能,能发出相应的闹钟提示

4、实现12/24计时方式转换

5、实现星期显示

二、总体框架设计(附上总体设计框架)

整个设计的流程和思路如图1所示

(图1)

三、设计步骤(分模块叙述,并附上各模块与总体电路图)

本次实验设计思路和顺序与图1框架一致,一共分为7步,下面是每一步的详细说明:

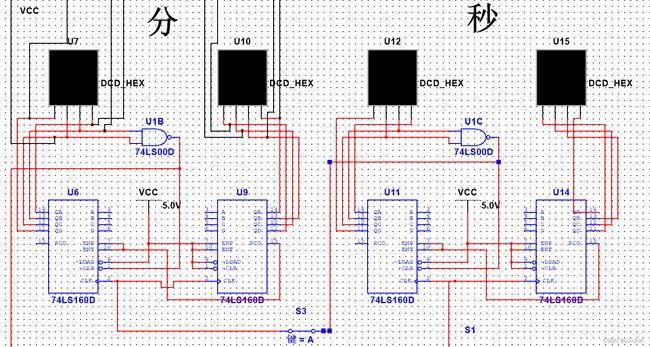

(1)设计60进制

60进制是采用两片74ls160芯片和与非门实现的,分、秒计数器的十位都是6进制(0-5),个位都是10进制(0-9),共同构成60进制。60进制采用74ls160的清零法来实现10进制功能和6进制功能,根据芯片74ls160的结构把输出端的0110用一个与非门(74ls00)引到清零端(CLR)端,即当个位计数到10的瞬间,向本位发送一个清零信号,并同时向其十位发送一个进位脉冲。十位加法计数器在计数到6的瞬间,向本位发送一个清零信号,并同时向分(秒)位的个位发送一个进位脉冲。

分、秒的设计都为60进制,用导线将秒位的与非门输出端和分位的脉冲端相连即可设置好分秒进位。

60进制具体电路如图2所示,分秒相连具体电路如图3所示。

(图2)

(图3)

(2)设计24进制

24进制(00-23)的实现同样是由2片74ls160芯片和与非门构成,方法为清零法,时计时器的十位是二进制,个位是十进制,同时和与非门相连,实现满24清零,和分、秒不同,它有两个清零信号,一是在小时的个位计数到10的瞬间,向本位发送一个清零信号,并同时向十位数发送一个进位脉冲。二是在小时的十位计数到2并且个数计数到4的瞬间,向个位和十位同时发送一个清零信号。所以与非门输入端连接为:十位的QB,个位的QC,脉冲输入为分位的与非门输出端。

24进制具体电路如图4所示,将24进制连接在总电路如图5所示。

(图4)

(图5)

(3)时、分、秒相连

该流程比较简单,只需要将上面两个设计好的模块用导线将本模块的脉冲与上一模块的与非门输出连接即可。

具体电路如图6。

(图6)

(4)设置手动调时功能

该模块通过在脉冲端和与非门输出端添加一个开关,开关闭合一次即输入一次脉冲,可使计数加一,如此可实现调时功能。

具体电路如图7。

(图7)

(5)设置闹钟

闹钟模块是由数值比较器74ls85和拨码开关构成,74ls85通过比较拨码开关设定的数值和数码管显示的时、分数值是否一致,当一致时就会使灯泡亮灯一分钟,从而达到闹钟目的。

具体电路如图8。

(图8)

(6)设置星期

该模块通过一片74ls160芯片和三输入与非门(74ls10)实现,让该模块达到七进制(0-6),三输入与非门输出端与清零端(CLR)结合,当数码管达到6的瞬间,向清零端发出清零信号。

具体电路图如图9所示。

(图9)

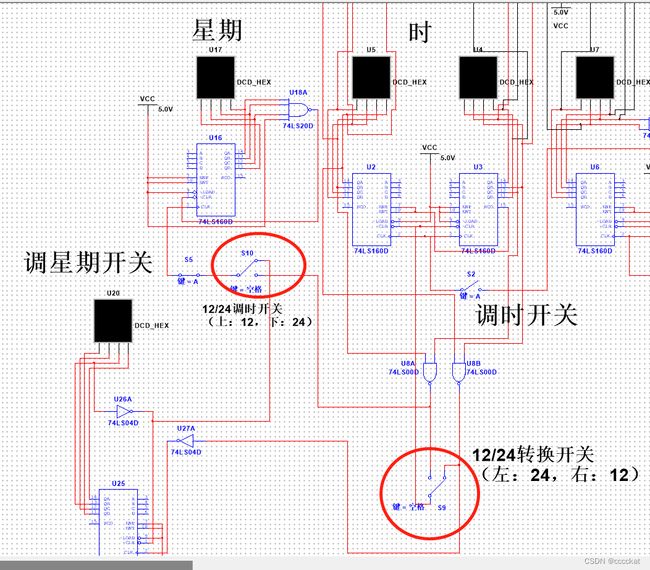

(7)实现12/24小时制转换

该模块在时模块连接清零端增加一个单刀双掷开关,开关一端连接12小时进制的与非门输出,另一端连接24小时进制的与非门输出,通过拨动开关实现时模块的12和24小时进制的转换,具体连接如图10。

为了解决在12小时制需要2个12小时轮转过后星期才会增加1的问题,在12小时的与非门输出端增加了一个满2进1模块,该模块由74ls160和非门构成,脉冲由时模块的12小时进制与非门输出端连接,从而达到在12小时制时,会经过2次12小时后,星期才会进1。在满2进1模块端和12小时制的与非门输出端导线之间加一个非门是为了让满2进1模块的初始值为0。

具体电路如图10所示。

(图10)

在时模块连接星期模块时,需要在星期模块的输入脉冲端接一个单刀双掷开关,当使用24小时进制时,就将星期模块直接连接时模块24小时进制的与非门输出端,当使用12小时进制时就将星期模块连接满2进1模块的非门输出端,从而实现12/24小时转换。具体如图11所示,通过图中2个圈的拨动即可实现转换。

(图11)

四、运行结果

五、心得体会

首先非常感谢在设计过程中提出问题时,各位老师和身边同学的耐心解答。

本次课程设计使我对数字电路这门课的理解更加深刻。专业课的知识综合运用实践训练,是对整体专业知识的总结与考察。在学完数字电路这门课课本上的知识后,其实是会觉得有些枯燥的,并且也不了解这个它的具体用途。但在这周的课程设计中,不论是中间的过程还是最终的成品,都让我印象深刻,这种将所学的知识运用到实际生活中经常用的物件中的实验,让我了解到了大学所学知识的用途,这将更加鼓舞我在往后的学习中投入更多的精力,争取成为一名合格的大学生。

我的主要收获有以下几点:

一、学会了使用Multisim的基本功能。对本学期数字电路课程中学到的元器件的功能有了直观的认识。

二、学会了查找资料。在设计之前,对于各类元器件、软件、电路都只是停留在了解阶段,之前也一直处于比较依赖老师和同学的阶段,有任何问题第一时间选择选择问她们,但在这次设计中,就需要自己去查找资料来辅助解决这次设计。

三、专业知识的进一步提升。本次课程设计需要综合运用整学期学到的知识,将理论与实际结合起来,这对我们是一个大的考验,在完成后,也能明显感觉到自己的专业知识有了进一步的提升。

通过这次课程设计不仅仅有收获,而且还有一些对以后这类课程设计的反思:

一、设计的过程中要预先给自己留够的空间。否则临时在中间添加元器件时,会显得拥挤且混乱。

二、在一开始设计时一个个模块单独设计并验证,最后再将各模块连接。

三、在连接总电路之前,可以想想各模块有没有更加简洁的线路,将各模块电路的线尽量排列整齐。

刚开始拿到这个课程设计还是比较迷茫的,一开始我甚至连Multisim这个软件都没有下载,感觉无从下手。所以我花了些时间去研究软件、分析题目、整理设计框架,了解基本运行原理来论证和改进。

基本框架确定后,再去查资料,通过Multisim仿真、请教老师来重新改进。虽然实际运行中出现了很多问题,换了不少设计,有时无法找出错误就换元器件重新接线。

有些在理论上可行的电路在调试中未必正确,例如在设计手动调时功能时,初步想法是在CLK端和与非门输出端之间的导线增加一个脉冲,但在仿真实验中发现,这是不可行的。这就需要耐心、仔细分析和解决问题,不断尝试才能得出正确的答案。

在完成了设计并验证后,我发现有些事情,一开始面对宏大的问题看着是很难的,将大问题拆解成小问题,一步步认真的做,才能完成它、理解它。

以上,就是我对本次设计的看法,通过此次课程设计,虽然最终我的设计并不是完美的(例如在增加手动调时功能后,整个电路的初始值会是1),但我学会了许多知识,最终结果也到达了本次课程设计的基本要求,特别是对Multisim该软件的认识以及运用和设计中所用到的数字电子技术的知识的运用。

总的来说,本次课程设计极大的增加了我对专业知识的理解和兴趣。