一文看懂GPIO口的八种工作原理

GPIO是通用输入/输出端口的简称,是STM32可控制的引脚。GPIO的引脚与外部硬件设备连接,可实现与外部通讯、控制外部硬件或者采集外部硬件数据的功能。

STM32F103ZET6芯片为144脚芯片,包括7个通用目的的输入/输出口(GPIO)组,分别为GPIOA、GPIOB、GPIOC、GPIOD、GPIOE、GPIOF、GPIOG,同时每组GPIO口组有16个GPIO口。通常简略称为PAx、PBx、PCx、PDx、PEx、PFx、PGx,其中x为0-15。

**

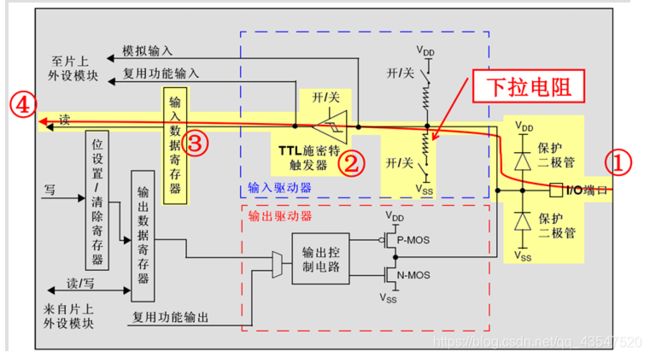

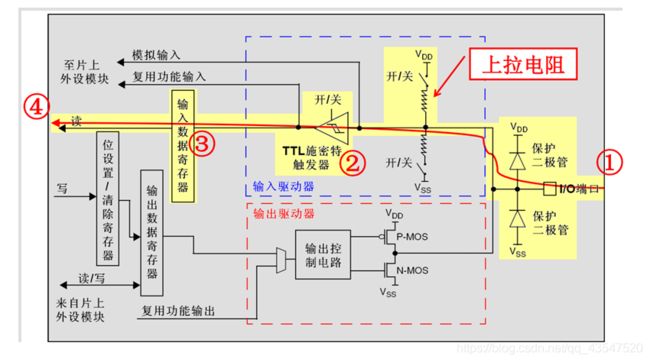

GPIO基本结构

**

每个GPIO内部都有这样的一个电路结构,这个结构在本文下面会具体介绍。

保护二极管:IO引脚上下两边两个二极管用于防止引脚外部过高、过低的电压输入。当引脚电压高于VDD时,上方的二极管导通;当引脚电压低于VSS时,下方的二极管导通,防止不正常电压引入芯片导致芯片烧毁。但是尽管如此,还是不能直接外接大功率器件,须加大功率及隔离电路驱动,防止烧坏芯片或者外接器件无法正常工作。

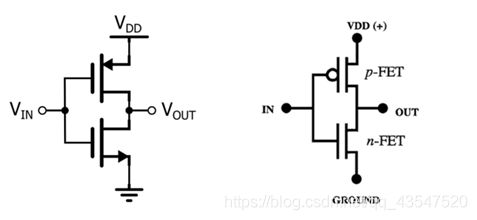

P-MOS管和N-MOS管:由P-MOS管和N-MOS管组成的单元电路使得GPIO具有“推挽输出”和“开漏输出”的模式。

TTL肖特基触发器:信号经过触发器后,模拟信号转化为0和1的数字信号。但是,当GPIO引脚作为ADC采集电压的输入通道时,用其“模拟输入”功能,此时信号不再经过触发器进行TTL电平转换。ADC外设要采集到的原始的模拟信号。

GPIO的工作方式有8种,分别是

浮空输入_IN_FLOATING

带上拉输入_IPU

带下拉输入_IPD

模拟输入_AIN

开漏输出_OUT_OD

推挽输出_OUT_PP

开漏复用输出_AF_OD

推挽复用输出_AF_PP

4输入 + 2 输出 + 2 复用输出,一共是8种模式,

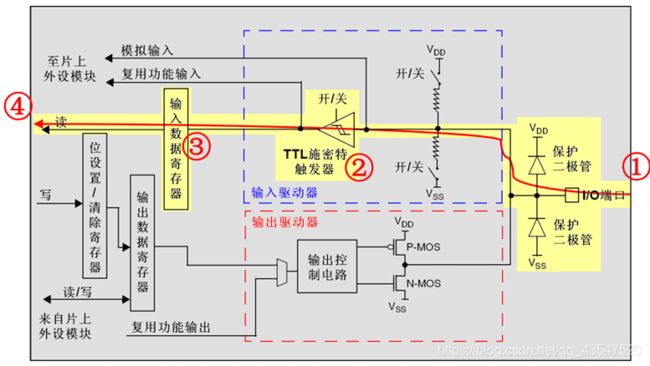

浮空输入模式

黄色的高亮部分显示了数据传输通道,外部的电平信号通过左边编号1的I/O 端口进入STM32内部经过编号2的施密特触发器整形以后送入编号为3的“输入数据寄存器”在“输入数据寄存器”的另一端(编号4) ,CPU通过内部的数据总线可以随时读出I/O 端口的电平变化的状态。这个时候的I/O的电平状态是不确定的,完全由外部输入决定;如果在该引脚悬空(外围电路没有连接)的情况下,读取该端口的电平是不确定的。

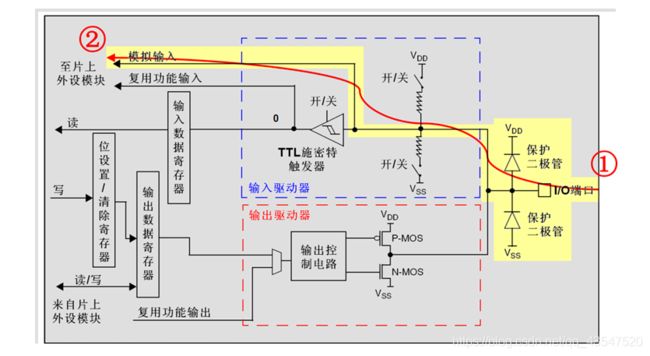

上拉输入模式

与前面介绍的浮空输入模式相比,仅仅是在数据通道上面,接入了一个上拉电阻,根据STM32的数据手册,这个上拉电阻阻值介于30K~50K 欧姆。在I/O口无信号输入的情况下,输入端的电平可以保持在高电平(VDD经过上拉电阻);并且在I/O端口输入为低电平的时候,输入端的电平就是低电平(可以理解为电阻分压)。

下拉输入模式

对于输入下拉模式的输入,是在数据通道的下部,接入了一个下拉电阻。

根据STM32的数据手册,这个下拉电阻阻值也是介于30K~50K 欧姆。

怎么选择上拉电阻或者下拉电阻

1.当作单片机作为输入时,假设我们直接在IO端口接一个按键到地(或电源)。因为按键按不按管脚都是悬空的。单片机就很难检测按键是否按下。所以人为的接一个上拉(或下拉)。以确定未按下的时候IO输入电平的状态。

2.可以提高芯片的抗干扰能力。

3.当单片机的IO口作输出时,如果不接上拉电阻只能提供灌电流。无法输出电流驱动外接设备。这时也需要考虑上拉电阻。这样才可以使IO输出高电平

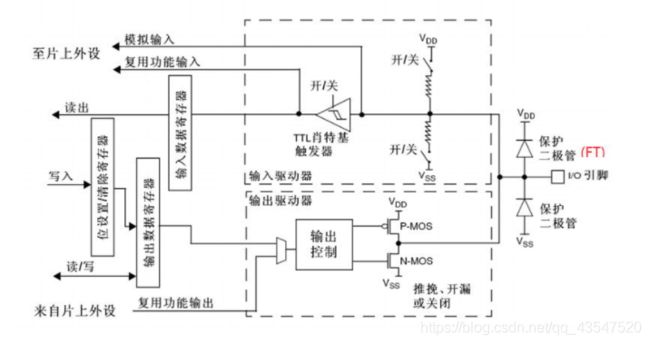

模拟输入模式

如果把STM32配置为模拟输入模式时,工作原理就比较简单了,信号从左边编号为1 的端口进从右边编号为2的一端直接进入STM32单片机的AD模块。

细心的朋友可以看到数据通道中上拉、下拉电阻和施密特触发器,这时均处于关断的状态,“输入数据寄存器”就不能反映IO端口上的电平变化的状态了,换句话说,也就是在模拟输入状态下,CPU不能通过“输入数据寄存器”读到IO端口变化的数据了。

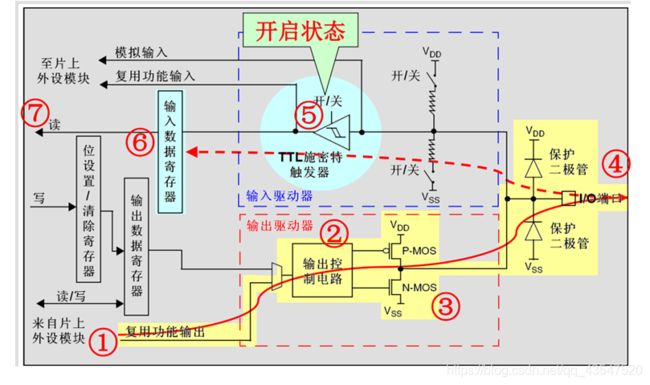

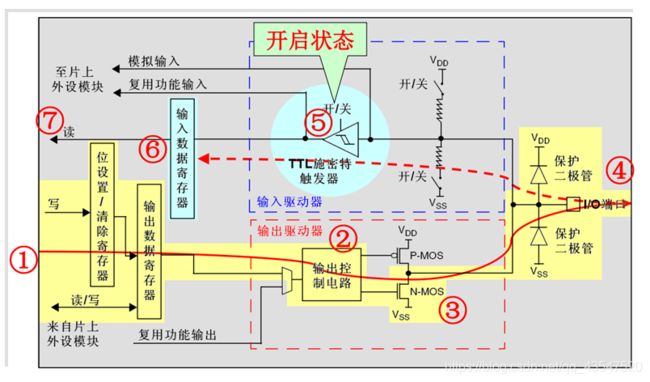

开漏输出模式

当CPU 在编号1 端通过“位设置/ 清除寄存器”或“输出数据寄存器”写入数据后,该数据位将通过编号2的输出控制电路传送到编号4 的I/O端口。如果CPU 写入的是逻辑“1 ”,则编号3 的N-MOS管将处于关闭状态,此时I/O 端口的电平将由外部的上拉电阻决定。如果CPU 写入的是逻辑“0 ”,则编号3的N-MOS管将处于开启状态,此时I/O端口的电平被编号3 的N-MOS管拉到了“地”的零电位。

在图中的上半部,施密特触发器处于开启状态,这意味着CPU 可以在“输入数据寄存器”的另一端,随时可以监控I/O端口的状态,通过这个特性,还可以实现了虚拟的I/O端口双向通信:假如CPU 输出逻辑“1 ”,由于编号3 的N-MOS管处于关闭状态,I/O 端口的电平将完全由外部电路决定。因此,CPU 可以在“输入数据寄存器”读到外部电路的信号,而不是它自己输出的逻辑“1 。

开漏复用输出模式

GPIO的开漏复用输出模式与开漏输出模式的工作原理基本相同。不同的是编号为2 的输入的源不同,它是和复用功能的输出端相连。此时的“输出数据寄存器”被输出通道给断开了。从上面的这个图,我们还可以看到CPU同样可以从“输入数据寄存器”读取到外部IO端口变化的电平信号。

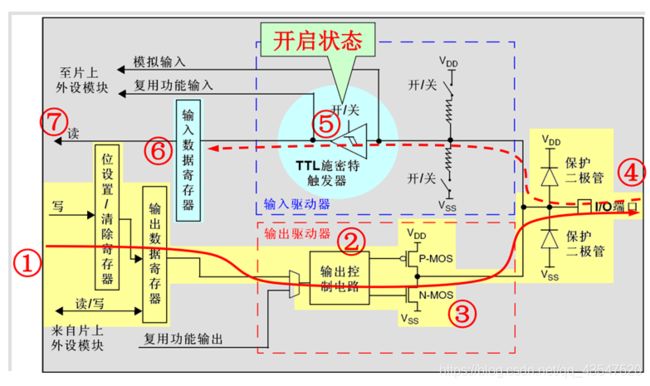

推挽输出

GPIO的推挽输出模式是在开漏输出模式的基础上,在“输出控制电路”之后,增加了一个P-MOS管。当CPU输出逻辑“1 ”时,编号3 处的P-MOS管导通,而下方的N-MOS管截止,达到输出高电平的目的。当CPU输出逻辑“0 ”时,编号3 处的P-MOS管截止,而下方的N-MOS管导通,达到输出低电平的目的,在这个模式下,CPU 仍然可以从“输入数据寄存器”读到该IO端口电压变化的信号。

推挽复用输出模式

编号2“输出控制电路” 输入是与复用功能的输出端相连。此时“输出数据寄存器”被从输出通道断开了,片上外设的输出信号直接与“输出控制电路”的输入端想连接。我们将GPIO配置成复用输出功能后,假如相应的外设模块没有被激活,那么此时IO端口的输出将不确定。其它部分原理与前面叙述的模式一样,包括对“输入数据寄存器”的读取方式也是一样的。

总结与分析

1、什么是推挽结构和推挽电路?

推挽输出的结构是由两个三极管或者MOS管受到互补信号的控制,两个管子始终保持一个处于截止,另一个处于导通的状态。

推挽电路是两个参数相同的三极管或MOSFET,以推挽方式存在于电路中,各负责正负半周的波形放大任务。电路工作时,两只对称的功率开关管每次只有一个导通,所以导通损耗小、效率高。输出既可以向负载灌电流,也可以从负载抽取电流。推拉式输出级既提高电路的负载能力,又提高开关速度。

推挽输出的一个缺点是,如果当两个推挽输出结构相连在一起,一个输出高电平,即上面的MOS导通,下面的MOS闭合时;同时另一个输出低电平,即上面的MOS闭合,下面的MOS导通时。电流会从第一个引脚的VCC通过上端MOS再经过第二个引脚的下端MOS直接流向GND。整个通路上电阻很小,会发生短路,进而可能造成端口的损害。这也是为什么推挽输出不能实现" 线与"的原因。

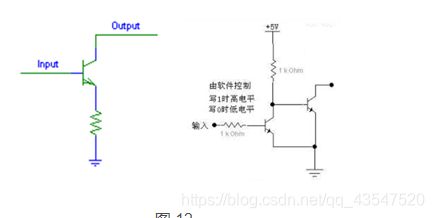

2、什么是开漏输出电路?*

常说的与推挽输出相对的就是开漏输出,对于开漏输出和推挽输出的区别最普遍的说法就是开漏输出无法真正输出高电平,即高电平时没有驱动能力,需要借助外部上拉电阻完成对外驱动。下面就从内部结构和原理上说明为什么开漏输出输出高电平时没有驱动能力,以及进一步比较与推挽输出的区别。

首先需要介绍一些开漏输出和开集输出。这两种输出的原理和特性基本是类似的,区别在于一个是使用MOS管,其中的"漏"指的就是MOS管的漏极;另一个使用三极管,其中的"集"指的就是三极管的集电极。这两者其实都是和推挽输出相对应的输出模式,由于使用MOS管的情况较多,很多时候就用"开漏输出"这个词代替了开漏输出和开集输出。

开漏输出的这一特性一个明显的优势就是可以很方便的调节输出的电平,因为输出电平完全由上拉电阻连接的电源电平决定。所以在需要进行电平转换的地方,非常适合使用开漏输出。

**开漏输出的这一特性另一个好处在于可以实现"线与"功能,所谓的"线与"指的是多个信号线直接连接在一起,**只有当所有信号全部为高电平时,合在一起的总线为高电平;只要有任意一个或者多个信号为低电平,则总线为低电平。而推挽输出就不行,如果高电平和低电平连在一起,会出现电流倒灌,损坏器件。