基于异步FIFO的串口回环测试

文章目录

- 前言

- 一、异步FIFO简介

- 二、串口简介

-

- 2.1 数据接收模块(RX)

- 2.1 数据发送模块(TX)

- 三、IP核说明与配置

-

- 2.1 PLL IP核

- 2.2 FIFO IP核

- 四、数据关联

前言

当涉及到串口通信的硬件设计和软件开发时,进行有效的测试是至关重要的。串口回环测试是一种常见的测试方法,用于验证串口通信的功能和稳定性。在许多应用中,为了确保串口通信的正常运行,往往需要使用缓冲区或FIFO来管理数据的传输和接收。

基于异步FIFO的串口回环测试是一种测试方法,其中FIFO被用于连接串口的发送和接收端口。这种测试方法可以帮助验证FIFO和串口逻辑的正确性,并确保数据在往返传输过程中保持精确和稳定。

在本文中,我们将探讨如何使用异步FIFO来实现串口回环测试。我们将介绍如何设计和构建包含异步FIFO的串口回环测试电路,并提供相关的软件代码示例。我们还将讨论这种测试方法的重要性,以及它在确保串口通信质量和可靠性方面的作用。

本文旨在为工程师、硬件设计人员和软件开发者提供有关基于异步FIFO的串口回环测试的详细介绍和指导。无论您是初学者还是有经验的专业人士,本文都将为您提供基本的理论知识、实施步骤和建议,以帮助您成功完成串口回环测试。

一、异步FIFO简介

FIFO(First-In-First-Out)是一种常用的数据缓冲区,用于在数据的生产者和消费者之间进行数据传输。它按照先进先出的原则,确保数据以先进入缓冲区的顺序被读取和处理。

例如,将0、1、2、3、4、5…依次不断写入到FIFO里面,然后传输到其它模块处理,那么,最开始被处理的数据就是最先进入到FIFO里面的数据,即为0,下一个处理的数据是第二个进入到FIFO里面的数据,即为1。工作流程图如下:

FIFO有多种应用,尤其在数据传输和存储方面。它可以用于解决通信设备之间传输速度不匹配的问题。当数据发送端以较快的速度产生数据而数据处理端以更慢的速度处理时,FIFO可以临时存储数据,以平衡两者之间的速度差异,从而保证数据的连续性和完整性。

异步FIFO是一种特殊类型的FIFO,它在处理输入数据和输出数据之间没有时钟同步。与同步FIFO不同,异步FIFO不依赖于共享时钟信号来实现数据的读写操作。这使得异步FIFO在异构系统中更具灵活性,能够连接具有独立时钟域的模块。

异步FIFO通常由两个主要组件组成:读取(读取数据的操作)和写入(写入数据的操作)。读写操作涉及到数据的存储和移位,以及对读写指针的更新。为了确保数据的正确性和稳定性,在设计异步FIFO时需要考虑数据的同步和脉冲的处理。异步FIFO主要信号包含写FIFO时钟,写请求信号,写入的数据,写入的数据个数;读FIFO时钟,读请求信号,读出的数据,读出的数据个数。异步FIFO信号框图如下:

与同步FIFO相比,异步FIFO可能更复杂一些,因为需要处理异步数据传输时的时序问题。然而,使用适当的设计和时序技术,可以实现可靠的异步FIFO,用于数据传输和处理的各种应用中。

在串口通信中,异步FIFO经常被用于解决串口发送和接收之间的速度不匹配问题。通过使用异步FIFO来缓冲和管理发送和接收的数据,可以提高串口通信的效率和稳定性。

二、串口简介

2.1 数据接收模块(RX)

RX(接收)模块是串口回环中的一个重要组成部分,它负责接收PC机发送的数据,并将其传递给数据回环的发送模块。本次串口回环采用的是RS232通信协议,数据位可以设置为5位、6位、7位或8位。这些数据位指定了每个字节中用于传输数据的位数。一般情况下,常用的设置是8位数据位,因为它提供了更大的数据范围和更高的精确度。本次回环测试也是采用8位数据位来进行测试。

设置串口接收模块工作时钟为100MHZ,波特率(1s内传输的比特数)为115200,假设传输的数据为8’b0000_1000,绘制的信号波形图如下:

2.1 数据发送模块(TX)

TX(发送)模块是串口回环另一个重要的组成部分。TX模块负责将数据发送到PC机,以实现数据的往返传输。TX模块作用是将RX模块编码产生的8bit数据,解码后重新得到单比特的信号。设置串口发送模块工作时钟为50MHZ,波特率也是为115200,假设需要解码的数据为8’b0100_1100,将数据解码的信号波形图如下所示:

三、IP核说明与配置

2.1 PLL IP核

PLL IP 核通过将输入时钟信号与内部振荡器进行频率和相位锁定,以生成稳定的、高质量的输出时钟信号。它通常用于对时钟信号进行频率分频、倍频以及时钟相位调整等操作。

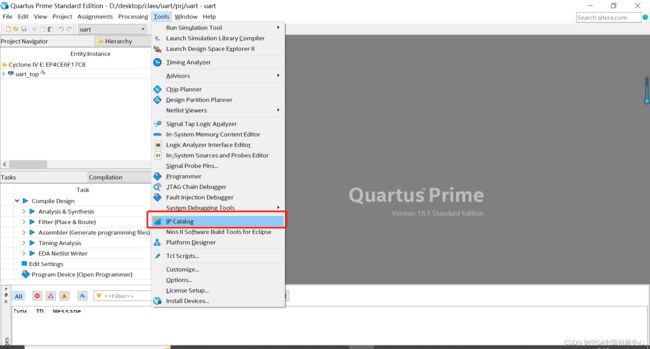

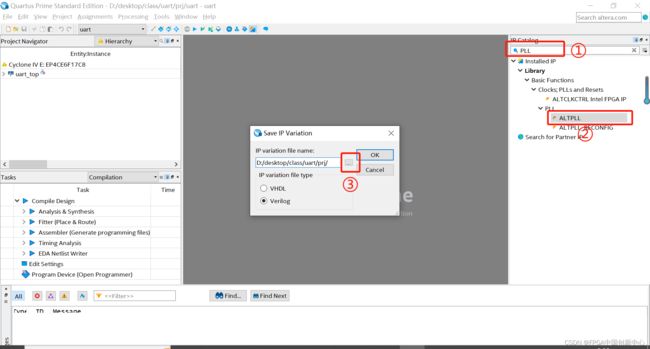

在Quartus主界面,Tools里面选择IP Catalog,如下图所示:

①在弹出的界面里面输入PLL,②然后点击ALTPLL,③为PLL IP核指定一个存放路径并命名,本工程给PLL IP核命名为clk_gen。操作步骤如下图所示:

针对弹出的界面:

①是关于PLL IP核的相关文件和说明文档。这些文档旨在提供有关PLL IP核的详细信息,包括核的功能、使用方法、接口规范、时钟设置和调整方法等。

②是使用PLL IP核需要配置的信息,在后续使用到再挨个说明。

③是PLL IP核配置好以后的大致模型,这里因为我们之前已经配置好了,输入的时钟是inclk0,输出的时钟是c0和c1,还有一个锁存信号。

④是芯片家族型号,在最开始新建工程时已经选中,默认不可更改。

⑤是需要选择设备的速度等级,将这里默认设置为any,Quartus将根据设计的需求、资源利用率、时钟频率等因素综合考虑,自动选择一个合适的且满足设计要求的设备速度等级。

⑥是设置输入时钟的频率,这里默认传入的是系统时钟,频率设置为50MHZ。

⑦是设置PLL类型,这里因为器件原因,使用默认即可。

⑧是在PLL里面默认生成返回路径,有如下几种工作模式可以选择:

一、正常模式(Normal Mode):这是最常见的PLL工作模式。在正常模式下,PLL将输入时钟信号通过锁相环来生成稳定的输出时钟信号。它可以根据反馈路径和设计参数来控制输出时钟频率和相位。

二、源同步补偿模式(Source-Synchronous Compensation Mode):此模式通常用于源同步接口的应用。源同步补偿模式允许PLL根据输入数据的时钟信号进行更精确的时钟生成,并通过提供相应的延迟补偿来确保数据的正确采样。这在高速数据传输中非常有用,可以提高系统的可靠性和抗噪声能力。

三、零延迟缓冲模式(Zero Delay Buffer Mode):这种模式通过使用零延迟缓冲器来消除时钟信号的延迟。零延迟缓冲模式通常在需要最小化时钟延迟的应用中使用,例如时序严格的系统,如DDR接口控制器等。它可以提供高精度的时钟分配和延迟控制,以确保系统的时序要求得到满足。

四、无补偿模式(No Compensation):这种模式下,PLL不进行任何补偿操作。它适用于某些特殊应用,如需要定制化的时钟生成或需要手动控制PLL的补偿设置的场景。在这种模式下,需要手动配置PLL的控制参数来满足特定的设计要求。

因为设计没有特殊的需求且工程较小,因此采用默认的普通模式即可。

⑨是指在配置PLL IP核时,可以选择对哪个输出时钟频率进行补偿操作。补偿是指对时钟信号进行精确调整,以使其频率和相位与参考时钟或期望的时钟关系保持一致。这里默认选择即可。配置完成后如下图所示,点击Next进行下一步:

设置输入信号选项栏,可以设置创建一个复位信号对PLL进行异步复位,用于将PLL重置为初始状态,以便在系统启动、初始化或特定条件下重新同步时钟。或者是创建一个控制相位频率检测器的启用或禁用,用于比较参考信号和反馈信号之间的相位和频率差异,以控制PLL的运行。这两个选项都可以不勾选。

设置输入信号选项栏,需要创建一个锁存信号“locked”,用于指示锁相环是否已经锁定到稳定状态。“enable self-reset on loss lock”选项是用于控制PLL在失去锁定时,锁相环是否自动执行复位操作,以重新建立锁定。本设计的全局复位是需要关锁存信号和系统复位,不需要自动执行复位操作,配置图如下图所示,配置完成后点击Next:

如下是频谱扩展 功能,在时钟信号中引入微小的频率变化,以减少电磁干扰 (EMI) 和射频干扰 (RFI)。保持默认设置点击Next即可:

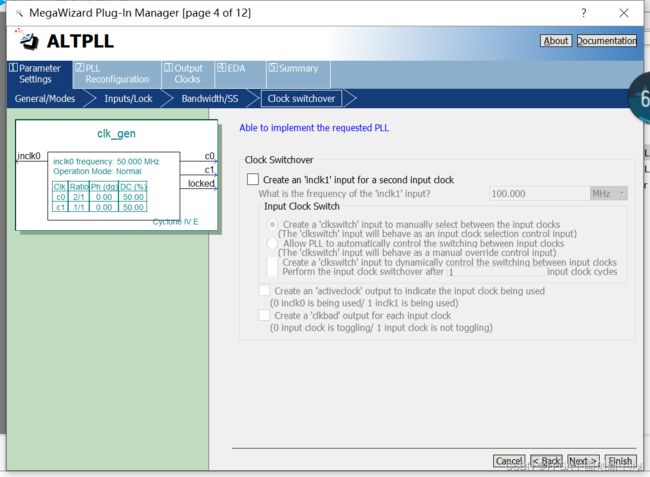

如下是时钟切换功能,允许在不中断系统运行的情况下,动态切换PLL的时钟源。这里不使用保持默认设置点击Next即可:

如下是动态重配置功能,允许在系统运行时修改PLL的配置参数,而无需重新编程FPGA或重新启动系统。这里不使用保持默认点击Next即可:

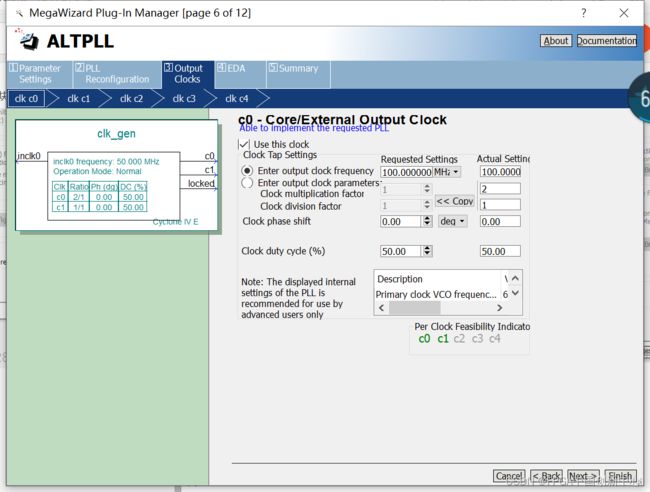

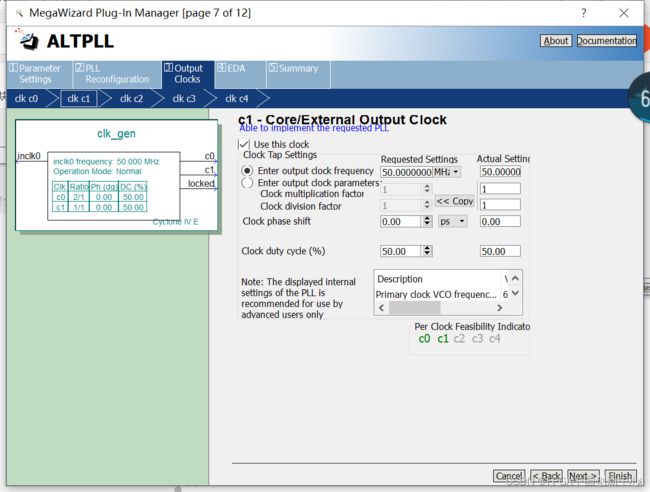

接下来配置输出的时钟,设置c0时钟频率为100MHZ,无相位偏移,占空比为50%;设置c1时钟频率为50MHZ,无相位偏移,占空比也为50%。在这里,系统时钟频率是50MHZ,输出的c1时钟频率也为50MHZ,那么可不可以不分频直接拿系统时钟代替分频后的c1时钟呢?这是可以的,引入50MHZ的输出时钟,是为了与100MHZ的输出时钟保持使能同步,如果锁存信号为低电平,那么输出的两个时钟都会失能,如果为高电平那么两个时钟都会开始工作。配置如下:

设置好输出时钟后,一直点击Next,到如下界面后勾选生成例化模板,点击finish完成PLL IP核的配置:

2.2 FIFO IP核

在如下页面,在搜索框内输入FIFO,选择FIFO后为文件新建一个存放路径,本工程给FIFO IP核文件命名为fifo_gen。操作步骤如下图所示:

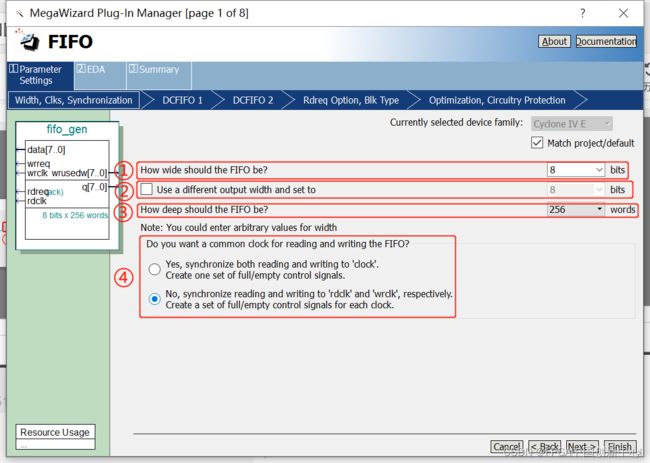

进入如下界面后:

①是设置FIFO写数据的位宽,因为这里是需要和数据位宽为8的串口相关联,所以这里需要设置大于等于8位宽。

②是配置读数据位宽,如果读写数据位宽相同,则此处就不勾选。因为串口通信接收模块接收的是8位宽数据,发送给发送模块的也是8位宽数据,所以这里就不勾选。

③是设置FIFO的数据个数,即深度,本次设计深度为256,即FIFO最多存储256个8位宽的数据。

④是设置读写时钟是否相同,如果相同则为同步FIFO,否则为异步FIFO,因为本次接收数据模块时钟为100MHZ,发送数据模块时钟为50MHZ,所以需要选择第二个选项,使用异步FIFO。

配置好以后,点击Next:

如下是在配置此IP核时,有三种优化方式,询问你选择哪一种:

Lowest latency but requires synchronized clocks(最低延迟,但需要同步时钟):这种优化类型旨在实现最低的延迟,适用于需要快速数据传输并使用具有相同时钟源的同步时钟系统。该优化类型将重点放在降低延迟上,以实现更快的数据处理速度。这意味着该设计对时钟同步性要求较高,要求时钟信号在系统中保持同步。

Minimal setting for unsynchronized clocks(非同步时钟的最小设置):这种优化类型适用于使用非同步时钟的系统,优化目标是使用尽可能少的设置来实现PLL功能。这种优化类型主要关注简化设计和减少设置的复杂性,以便在非同步时钟环境中实现所需的PLL功能。

Best metastability protection, best fmax and unsynchronized clocks(最佳亚稳态保护、最佳fmax和非同步时钟):这种优化类型集中于提供最佳的亚稳态(metastability)保护、最高的工作频率(fmax)并适用于非同步时钟的系统。在这种设计中,关注点是保护系统免受亚稳态问题的影响,同时提供尽可能高的工作频率。这对于使用非同步时钟的系统尤其重要,因为非同步时钟可能会导致数据不稳定性和时序问题。

在设计中,如果对时序要求较高且工程比较复杂,芯片资源也丰富的情况下,可以选择第三个选项;如果芯片资源不够且工程较小时,可以选择第一个选项。在本设计中是折中选择第二个选项。

如下图配置好以后点击Next:

对于本工程而言,因为FIFO写入端写入数据的速度要大于FIFO读出端读出数据的速度,FIFO读出端要结合FIFO内的数据个数,将数据依次传输给数据发送模块处理。配置写入端写入数据的个数信号,图形如下:

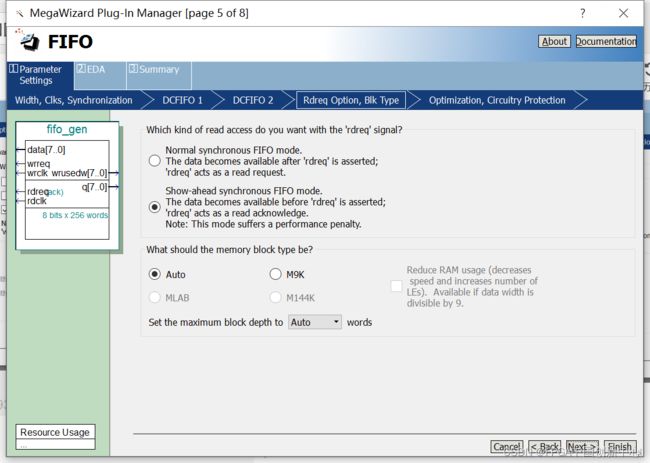

对于读请求信号,读过程有两种模式,第一种模式是在读请求信号有效的情况下,读出的数据会延迟读请求信号一个时钟周期;第二种模式是读出的数据与读请求信号保持同步,在读请求信号有效时就马上读出数据。本工程选择读请求信号与读出的数据保持同步这一模式。

在选择存储块和存储块最多存储的深度时,设置为自动即可。配置如下图所示,配置完成后点击Next:

如图为询问是否希望禁用某些电路保护功能,以确保电路的安全性和可靠性。这些保护功能可用于防止电路因过压、过流、过热等问题而损坏,当FIFO内写满数据时,可通过电路保护功能禁止数据的写入;当FIFO内读空数据时,也可通过电路保护功能防止继续读出数据。

“ implement FIFO storage with logic cells only, even if the device contains memory blocks”的意思是在使用FIFO IP核时,即使FPGA器件包含内存块,也要使用逻辑单元来实现FIFO存储。需要注意的是,使用逻辑单元来实现FIFO存储可能会导致占用更多的逻辑资源,并且可能对性能产生一定的影响。因此在这里是不选择此选项的。

配置完成后点击Next:

四、数据关联

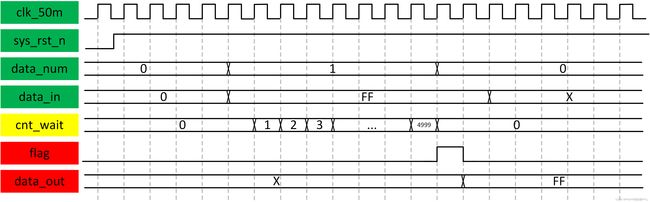

以向FIFO内写入一个数据为例,需要将此数据和数据个数作为数据发送模块开始工作信号产生的标志,绘制的信号波形图如下所示:

其中,data_num是数据个数,data_in是FIFO里面与数据个数对应的数据,因为串口波特率是115200,每次传输8bit数据需要发送10bit(包含起始位和停止位)数据,总共需要4400个时钟周期左右。设置等待5000个时钟周期,然后产生一个flag标志信号,和输出数据data_out,将这两个信号传输给数据发送模块,即可实现异步FIFO的串口回环测试。