pinctrl 配置信息详解

pinctrl 配置信息详解

文章目录

- pinctrl 配置信息详解

- iomuxc

- pinctrl配置详解

iomuxc

pinctrl(pin controller)可以管理系统中所有的pin,也可以设置管教的复用关系,电器属性等,所以pinctrl在内核钟使用的频率非常高。

IMX6ULL设备树中中节点以及使用:

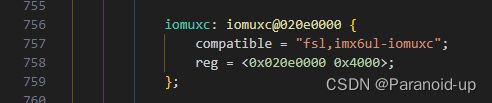

iomuxc 节点就是 I.MX6ULL 的 IOMUXC 外设对应的节点

iomuxc: iomuxc@020e0000 {

compatible = "fsl,imx6ul-iomuxc";

reg = <0x020e0000 0x4000>;

};

打开 imx6ull-alientek-emmc.dts,找到如下所示内容:

&iomuxc {

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059 /* SD1 VSELECT */

MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x13058 /* USB_OTG1_ID */

>;

};

pinctrl_csi1: csi1grp {

fsl,pins = <

MX6UL_PAD_CSI_MCLK__CSI_MCLK 0x1b088

MX6UL_PAD_CSI_PIXCLK__CSI_PIXCLK 0x1b088

MX6UL_PAD_CSI_VSYNC__CSI_VSYNC 0x1b088

MX6UL_PAD_CSI_HSYNC__CSI_HSYNC 0x1b088

MX6UL_PAD_CSI_DATA00__CSI_DATA02 0x1b088

MX6UL_PAD_CSI_DATA01__CSI_DATA03 0x1b088

MX6UL_PAD_CSI_DATA02__CSI_DATA04 0x1b088

MX6UL_PAD_CSI_DATA03__CSI_DATA05 0x1b088

MX6UL_PAD_CSI_DATA04__CSI_DATA06 0x1b088

MX6UL_PAD_CSI_DATA05__CSI_DATA07 0x1b088

MX6UL_PAD_CSI_DATA06__CSI_DATA08 0x1b088

MX6UL_PAD_CSI_DATA07__CSI_DATA09 0x1b088

>;

};

pinctrl_ds18b20: 18b20 {

fsl,pins = <

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0x17059

>;

};

pinctrl_dht11: dht11 {

fsl,pins = <

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0x17059

>;

};

pinctrl_enet1: enet1grp {

fsl,pins = <

MX6UL_PAD_ENET1_RX_EN__ENET1_RX_EN 0x1b0b0

MX6UL_PAD_ENET1_RX_ER__ENET1_RX_ER 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA0__ENET1_RDATA00 0x1b0b0

MX6UL_PAD_ENET1_RX_DATA1__ENET1_RDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_EN__ENET1_TX_EN 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA0__ENET1_TDATA00 0x1b0b0

MX6UL_PAD_ENET1_TX_DATA1__ENET1_TDATA01 0x1b0b0

MX6UL_PAD_ENET1_TX_CLK__ENET1_REF_CLK1 0x4001B009

>;

};

pinctrl_enet2: enet2grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO07__ENET2_MDC 0x1b0b0

MX6UL_PAD_GPIO1_IO06__ENET2_MDIO 0x1b0b0

MX6UL_PAD_ENET2_RX_EN__ENET2_RX_EN 0x1b0b0

MX6UL_PAD_ENET2_RX_ER__ENET2_RX_ER 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA0__ENET2_RDATA00 0x1b0b0

MX6UL_PAD_ENET2_RX_DATA1__ENET2_RDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_EN__ENET2_TX_EN 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA0__ENET2_TDATA00 0x1b0b0

MX6UL_PAD_ENET2_TX_DATA1__ENET2_TDATA01 0x1b0b0

MX6UL_PAD_ENET2_TX_CLK__ENET2_REF_CLK2 0x4001B009

>;

};

pinctrl_ecspi3: ecspi3grp {

fsl,pins = <

MX6UL_PAD_UART2_RTS_B__ECSPI3_MISO 0x100b1 /* MISO*/

MX6UL_PAD_UART2_CTS_B__ECSPI3_MOSI 0x100b1 /* MOSI*/

MX6UL_PAD_UART2_RX_DATA__ECSPI3_SCLK 0x100b1 /* CLK*/

MX6UL_PAD_UART2_TX_DATA__GPIO1_IO20 0x100b0 /* CS*/

>;

};

pinctrl_gpio_leds: gpio-leds {

fsl,pins = <

MX6UL_PAD_GPIO1_IO03__GPIO1_IO03 0x17059

>;

};

pinctrl_gpio_keys: gpio-keys {

fsl,pins = <

MX6UL_PAD_UART1_CTS_B__GPIO1_IO18 0x80000000

>;

};

pinctrl_flexcan1: flexcan1grp{

fsl,pins = <

MX6UL_PAD_UART3_RTS_B__FLEXCAN1_RX 0x1b020

MX6UL_PAD_UART3_CTS_B__FLEXCAN1_TX 0x1b020

>;

};

pinctrl_flexcan2: flexcan2grp{

fsl,pins = <

MX6UL_PAD_UART2_RTS_B__FLEXCAN2_RX 0x1b020

MX6UL_PAD_UART2_CTS_B__FLEXCAN2_TX 0x1b020

>;

};

pinctrl_i2c1: i2c1grp {

fsl,pins = <

MX6UL_PAD_UART4_TX_DATA__I2C1_SCL 0x4001b8b0

MX6UL_PAD_UART4_RX_DATA__I2C1_SDA 0x4001b8b0

>;

};

pinctrl_i2c2: i2c2grp {

fsl,pins = <

MX6UL_PAD_UART5_TX_DATA__I2C2_SCL 0x4001b8b0

MX6UL_PAD_UART5_RX_DATA__I2C2_SDA 0x4001b8b0

>;

};

pinctrl_lcdif_dat: lcdifdatgrp {

fsl,pins = <

MX6UL_PAD_LCD_DATA00__LCDIF_DATA00 0x79

MX6UL_PAD_LCD_DATA01__LCDIF_DATA01 0x79

MX6UL_PAD_LCD_DATA02__LCDIF_DATA02 0x79

MX6UL_PAD_LCD_DATA03__LCDIF_DATA03 0x79

MX6UL_PAD_LCD_DATA04__LCDIF_DATA04 0x79

MX6UL_PAD_LCD_DATA05__LCDIF_DATA05 0x79

MX6UL_PAD_LCD_DATA06__LCDIF_DATA06 0x79

MX6UL_PAD_LCD_DATA07__LCDIF_DATA07 0x79

MX6UL_PAD_LCD_DATA08__LCDIF_DATA08 0x79

MX6UL_PAD_LCD_DATA09__LCDIF_DATA09 0x79

MX6UL_PAD_LCD_DATA10__LCDIF_DATA10 0x79

MX6UL_PAD_LCD_DATA11__LCDIF_DATA11 0x79

MX6UL_PAD_LCD_DATA12__LCDIF_DATA12 0x79

MX6UL_PAD_LCD_DATA13__LCDIF_DATA13 0x79

MX6UL_PAD_LCD_DATA14__LCDIF_DATA14 0x79

MX6UL_PAD_LCD_DATA15__LCDIF_DATA15 0x79

MX6UL_PAD_LCD_DATA16__LCDIF_DATA16 0x79

MX6UL_PAD_LCD_DATA17__LCDIF_DATA17 0x79

MX6UL_PAD_LCD_DATA18__LCDIF_DATA18 0x79

MX6UL_PAD_LCD_DATA19__LCDIF_DATA19 0x79

MX6UL_PAD_LCD_DATA20__LCDIF_DATA20 0x79

MX6UL_PAD_LCD_DATA21__LCDIF_DATA21 0x79

MX6UL_PAD_LCD_DATA22__LCDIF_DATA22 0x79

MX6UL_PAD_LCD_DATA23__LCDIF_DATA23 0x79

>;

};

pinctrl_lcdif_ctrl: lcdifctrlgrp {

fsl,pins = <

MX6UL_PAD_LCD_CLK__LCDIF_CLK 0x79

MX6UL_PAD_LCD_ENABLE__LCDIF_ENABLE 0x79

MX6UL_PAD_LCD_HSYNC__LCDIF_HSYNC 0x79

MX6UL_PAD_LCD_VSYNC__LCDIF_VSYNC 0x79

>;

};

pinctrl_pwm1: pwm1grp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO08__PWM1_OUT 0x110b0

>;

};

pinctrl_qspi: qspigrp {

fsl,pins = <

MX6UL_PAD_NAND_WP_B__QSPI_A_SCLK 0x70a1

MX6UL_PAD_NAND_READY_B__QSPI_A_DATA00 0x70a1

MX6UL_PAD_NAND_CE0_B__QSPI_A_DATA01 0x70a1

MX6UL_PAD_NAND_CE1_B__QSPI_A_DATA02 0x70a1

MX6UL_PAD_NAND_CLE__QSPI_A_DATA03 0x70a1

MX6UL_PAD_NAND_DQS__QSPI_A_SS0_B 0x70a1

>;

};

pinctrl_sai2: sai2grp {

fsl,pins = <

MX6UL_PAD_JTAG_TDI__SAI2_TX_BCLK 0x17088

MX6UL_PAD_JTAG_TDO__SAI2_TX_SYNC 0x17088

MX6UL_PAD_JTAG_TRST_B__SAI2_TX_DATA 0x11088

MX6UL_PAD_JTAG_TCK__SAI2_RX_DATA 0x11088

MX6UL_PAD_JTAG_TMS__SAI2_MCLK 0x17088

>;

};

pinctrl_sii902x: hdmigrp-1 {

fsl,pins = <

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x11

>;

};

pinctrl_tsc: tscgrp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO01__GPIO1_IO01 0xb0

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0xb0

MX6UL_PAD_GPIO1_IO03__GPIO1_IO03 0xb0

MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0xb0

>;

};

pinctrl_uart1: uart1grp {

fsl,pins = <

MX6UL_PAD_UART1_TX_DATA__UART1_DCE_TX 0x1b0b1

MX6UL_PAD_UART1_RX_DATA__UART1_DCE_RX 0x1b0b1

>;

};

pinctrl_uart2: uart2grp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DCE_TX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DCE_RX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART2_DCE_RTS 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART2_DCE_CTS 0x1b0b1

>;

};

pinctrl_uart2dte: uart2dtegrp {

fsl,pins = <

MX6UL_PAD_UART2_TX_DATA__UART2_DTE_RX 0x1b0b1

MX6UL_PAD_UART2_RX_DATA__UART2_DTE_TX 0x1b0b1

MX6UL_PAD_UART3_RX_DATA__UART2_DTE_CTS 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART2_DTE_RTS 0x1b0b1

>;

};

pinctrl_uart3: uart3grp {

fsl,pins = <

MX6UL_PAD_UART3_RX_DATA__UART3_DCE_RX 0x1b0b1

MX6UL_PAD_UART3_TX_DATA__UART3_DCE_TX 0x1b0b1

>;

};

pinctrl_usdhc1: usdhc1grp {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x17059

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x10071

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x17059

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x17059

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x17059

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x17059

>;

};

pinctrl_usdhc1_100mhz: usdhc1grp100mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170b9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100b9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170b9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170b9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170b9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170b9

>;

};

pinctrl_usdhc1_200mhz: usdhc1grp200mhz {

fsl,pins = <

MX6UL_PAD_SD1_CMD__USDHC1_CMD 0x170f9

MX6UL_PAD_SD1_CLK__USDHC1_CLK 0x100f9

MX6UL_PAD_SD1_DATA0__USDHC1_DATA0 0x170f9

MX6UL_PAD_SD1_DATA1__USDHC1_DATA1 0x170f9

MX6UL_PAD_SD1_DATA2__USDHC1_DATA2 0x170f9

MX6UL_PAD_SD1_DATA3__USDHC1_DATA3 0x170f9

>;

};

pinctrl_usdhc2: usdhc2grp {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

>;

};

pinctrl_usdhc2_8bit: usdhc2grp_8bit {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x10069

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x17059

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x17059

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x17059

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x17059

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x17059

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x17059

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x17059

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x17059

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x17059

>;

};

pinctrl_usdhc2_8bit_100mhz: usdhc2grp_8bit_100mhz {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100b9

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170b9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170b9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170b9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170b9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170b9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170b9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170b9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170b9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170b9

>;

};

pinctrl_usdhc2_8bit_200mhz: usdhc2grp_8bit_200mhz {

fsl,pins = <

MX6UL_PAD_NAND_RE_B__USDHC2_CLK 0x100f9

MX6UL_PAD_NAND_WE_B__USDHC2_CMD 0x170f9

MX6UL_PAD_NAND_DATA00__USDHC2_DATA0 0x170f9

MX6UL_PAD_NAND_DATA01__USDHC2_DATA1 0x170f9

MX6UL_PAD_NAND_DATA02__USDHC2_DATA2 0x170f9

MX6UL_PAD_NAND_DATA03__USDHC2_DATA3 0x170f9

MX6UL_PAD_NAND_DATA04__USDHC2_DATA4 0x170f9

MX6UL_PAD_NAND_DATA05__USDHC2_DATA5 0x170f9

MX6UL_PAD_NAND_DATA06__USDHC2_DATA6 0x170f9

MX6UL_PAD_NAND_DATA07__USDHC2_DATA7 0x170f9

>;

};

pinctrl_wdog: wdoggrp {

fsl,pins = <

MX6UL_PAD_LCD_RESET__WDOG1_WDOG_ANY 0x30b0

>;

};

ts_int_pin: ts_int_pin_mux {

fsl,pins = <

MX6UL_PAD_GPIO1_IO09__GPIO1_IO09 0x79

>;

};

csi_pwn_rst: csi_pwn_rstgrp {

fsl,pins = <

MX6UL_PAD_GPIO1_IO02__GPIO1_IO02 0x10b0

MX6UL_PAD_GPIO1_IO04__GPIO1_IO04 0x10b0

>;

};

};

};

示例代码就是向 iomuxc 节点追加数据,不同的外设使用的 PIN 不同、其配置也不同,因此一个萝卜一个坑,将某个外设所使用的所有 PIN 都组织在一个子节点里面。示例代码45.1.2.2 中 pinctrl_hog_1 子节点就是和热插拔有关的 PIN 集合,比如 USB OTG 的 ID 引脚。pinctrl_flexcan1 子节点是 flexcan1 这个外设所使用的 PIN, pinctrl_wdog 子节点是 wdog 外设所使用的 PIN。如果需要在 iomuxc 中添加我们自定义外设的 PIN,那么需要新建一个子节点,然后将这个自定义外设的所有 PIN 配置信息都放到这个子节点中。

iomuxc: iomuxc@020e0000 {

compatible = "fsl,imx6ul-iomuxc";

reg = <0x020e0000 0x4000>;

pinctrl-names = "default";

pinctrl-0 = <&pinctrl_hog_1>;

imx6ul-evk {

pinctrl_hog_1: hoggrp-1 {

fsl,pins = <

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

MX6UL_PAD_GPIO1_IO05__USDHC1_VSELECT 0x17059 /* SD1 VSELECT */

MX6UL_PAD_GPIO1_IO00__ANATOP_OTG1_ID 0x13058 /* USB_OTG1_ID */

>;

};

pinctrl_csi1: csi1grp {

fsl,pins = <

MX6UL_PAD_CSI_MCLK__CSI_MCLK 0x1b088

MX6UL_PAD_CSI_PIXCLK__CSI_PIXCLK 0x1b088

MX6UL_PAD_CSI_VSYNC__CSI_VSYNC 0x1b088

MX6UL_PAD_CSI_HSYNC__CSI_HSYNC 0x1b088

MX6UL_PAD_CSI_DATA00__CSI_DATA02 0x1b088

MX6UL_PAD_CSI_DATA01__CSI_DATA03 0x1b088

MX6UL_PAD_CSI_DATA02__CSI_DATA04 0x1b088

MX6UL_PAD_CSI_DATA03__CSI_DATA05 0x1b088

MX6UL_PAD_CSI_DATA04__CSI_DATA06 0x1b088

MX6UL_PAD_CSI_DATA05__CSI_DATA07 0x1b088

MX6UL_PAD_CSI_DATA06__CSI_DATA08 0x1b088

MX6UL_PAD_CSI_DATA07__CSI_DATA09 0x1b088

>;

};

};

pinctrl配置详解

compatible 属性值为“fsl,imx6ul-iomuxc”,前面讲解设备树的时候说过, Linux 内核会根据 compatbile 属性值来查找对应的驱动文件,所以我们在 Linux 内核源码中全局搜索字符串“fsl,imx6ul-iomuxc”就会找到 I.MX6ULL 这颗 SOC 的 pinctrl 驱动文件。

pinctrl_hog_1 子节点所使用的 PIN 配置信息,我们就以第 9 行的 UART1_RTS_B这个 PIN 为例,讲解一下如何添加 PIN 的配置信息, UART1_RTS_B 的配置信息如下:

MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x17059 /* SD1 CD */

我们重点来看一下这两部分是什么含义,前面说了,对于一个 PIN 的配置主要包括两方面,一个是设置这个 PIN 的复用功能,另一个就是设置这个 PIN 的电气特性。所以我们可以大胆的猜测 UART1_RTS_B 的这两部分配置信息一个是设置 UART1_RTS_B 的复用功能,一个是用来设置 UART1_RTS_B 的电气特性。

首先来看一下 MX6UL_PAD_UART1_RTS_B__GPIO1_IO19,这是一个宏定义,定义在文件arch/arm/boot/dts/imx6ul-pinfunc.h 中, imx6ull.dtsi 会引用 imx6ull-pinfunc.h 这个头文件,而imx6ull-pinfunc.h 又会引用 imx6ul-pinfunc.h 这个头文件(绕啊绕!)。从这里可以看出,可以在设备树中引用 C 语言中.h 文件中的内容。 MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 的宏定义内容如下:

#define MX6UL_PAD_UART1_RTS_B__UART1_DCE_RTS 0x0090 0x031C 0x0620 0x0 0x3

#define MX6UL_PAD_UART1_RTS_B__UART1_DTE_CTS 0x0090 0x031C 0x0000 0x0 0x0

#define MX6UL_PAD_UART1_RTS_B__ENET1_TX_ER 0x0090 0x031C 0x0000 0x1 0x0

#define MX6UL_PAD_UART1_RTS_B__USDHC1_CD_B 0x0090 0x031C 0x0668 0x2 0x1

#define MX6UL_PAD_UART1_RTS_B__CSI_DATA05 0x0090 0x031C 0x04CC 0x3 0x1

#define MX6UL_PAD_UART1_RTS_B__ENET2_1588_EVENT1_OUT 0x0090 0x031C 0x0000 0x4 0x0

#define MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 0x0090 0x031C 0x0000 0x5 0x0

#define MX6UL_PAD_UART1_RTS_B__USDHC2_CD_B 0x0090 0x031C 0x0674 0x8 0x2

代码 中一共有 8 个以“MX6UL_PAD_UART1_RTS_B”开头的宏定义,大家仔细观察应该就能发现,这 8 个宏定义分别对应 UART1_RTS_B 这个 PIN 的 8 个复用 IO。查阅《I.MX6ULL 参考手册》可以知 UART1_RTS_B 的可选复用 IO 如图 45.1.2.1 所示:

代 码 196 行 的 宏 定 义MX6UL_PAD_UART1_RTS_B__GPIO1_IO19 表 示 将UART1_RTS_B 这个 IO 复用为 GPIO1_IO19。此宏定义后面跟着 5 个数字,也就是这个宏定义的具体值,如下所示:

0x0090 0x031C 0x0000 0x5 0x0

这 5 个值的含义如下所示:

综上所述可知:

0x0090:mux_reg 寄存器偏移地址,设备树中的 iomuxc 节点就是 IOMUXC 外设对应的节点 , 根 据 其 reg 属 性 可 知 IOMUXC 外 设 寄 存 器 起 始 地 址 为 0x020e0000 。 因 此0x020e0000+0x0090=0x020e0090IOMUXC_SW_MUX_CTL_PAD_UART1_RTS_B 寄存器地址正 好 是 0x020e0090 , 大 家 可 以 在 《 IMX6ULL 参 考 手 册 》 中 找 到IOMUXC_SW_MUX_CTL_PAD_UART1_RTS_B 这个寄存器的位域图,如图 所示:

因此可知,0x020e0000+mux_reg 就是PIN 的复用寄存器地址。

0x031C:conf_reg 寄存器偏移地址,和 mux_reg 一样,0x020e0000+0x031c=0x020e031c,这个就是寄存器 IOMUXC_SW_PAD_CTL_PAD_UART1_RTS_B 的地址。

0x0000:input_reg 寄存器偏移地址,有些外设有 input_reg 寄存器,有 input_reg 寄存器的外设需要配置 input_reg 寄存器。没有的话就不需要设置,UART1_RTS_B 这个 PIN 在做GPIO1_IO19 的时候是没有 input_reg 寄存器,因此这里 intput_reg 是无效的。

0x5 : mux_reg 寄 存 器 值 , 在 这 里 就 相 当 于 设 置IOMUXC_SW_MUX_CTL_PAD_UART1_RTS_B 寄存器为 0x5,也即是设置 UART1_RTS_B 这个 PIN 复用为GPIO1_IO19。

0x0:input_reg 寄存器值,在这里无效。

这就是宏 MX6UL_PAD_UART1_RTS_B GPIO1_IO19 的含义,看的比较仔细的同学应该会发现并没有 conf_reg 寄存器的值,config_reg 寄存器是设置一个 PIN 的电气特性的,这么重要的寄存器怎么没有值呢?回到示例代码 中,第 9 行的内容如下所示:

MX6UL_PAD_UART1_RTS_B GPIO1_IO19 0x17059

MX6UL_PAD_UART1_RTS_B GPIO1_IO19 我们上面已经分析了,就剩下了一个 0x17059,反应快的应该已经猜出来了,0x17059 就是 conf_reg 寄存器值!此值由用户自行设置,通过此值来设置一个 IO 的上/ 下拉、驱动能力和速度等。在这里就相当于设置寄存器IOMUXC_SW_PAD_CTL_PAD_UART1_RTS_B 的值为 0x17059。