紫光FPGA试用--软件篇

目录

一 软件安装启动

二 如何打开IP核?查看/修改现有IP核参数?

三 如何定义引脚?

四 如何下载code进入FPGA?

1. 下载到FPGA芯片内:

2.下载到外部FLASH中

五 如何进入在线调试模式,调试步骤

操作步骤:

错误汇总:

六 Global include 设置

七 相关约束文件格式及使用范围

一 软件安装启动

license需要FAE提供,同时需要下载虚拟网卡。可以参考提供的文件操作。

若安装完成后显示错误:无MSVCP140_1.dll文件,无法打开软件。。这时只能重新安装,哪怕查看实际的安装目录下有次文件。

二 如何打开IP核?查看/修改现有IP核参数?

Toolà ip compile 。如下,左边catalog是软件所有的IP核,右边project是本工程下使用的IP核,双击可打开具体查看和修改配置。下图右侧是IP核的基本信息。

三 如何定义引脚?

Tool à physical constraint edit post-map ,里面有IC的I/O分布及其相关物理属性等视图及配置界面。点开工具后,左端是操作栏。

(注意:如果有添加.fdc调试配置文件在工程中,可能会报错,打不开这个工具)

四 如何下载code进入FPGA?

Toolàconfiguration,如下图。

有boundary scan 和 spi flash configuration,boundary scan下识别sbit文件,通过JTAG将其下载到FPGA 芯片内部。而spi flash configuration下,右击界面可以识别FLASH芯片,将code烧录到flash中。

1. 下载到FPGA芯片内:

1)先点击电脑的标识,connect to server,进行配置和连接USB BALSTER,需要输入电脑的IP地址,然后点击connect会出现扫描到的USB blaster,选择速率后点击next,显示出配置信息后finish。这里需要注意,如果能识别USB blaster,但是没办法识别到FPGA IC,可能是这里选择的速率过高,降低后在尝试识别IC。

2)add pango device ,添加sbit文件

3) program & verify

2.下载到外部FLASH中

1)首先需要将sbit文件转换成sfc文件。在Operations菜单中点击“Convert File”选项,选择FLASH芯片,以及添加sbit文件。

2)scan device 添加不成功??????

需要选中上图的器件后,在器件上面右击然后出现add flash device。

五 如何进入在线调试模式,调试步骤

涉及到两个工具,inserter & debugger

1. Fabric inserter 在线调试工具的参数设置文件,需要在compile 和 synthesize 成功后才能打开使用。其对应生成的文件为.fic(相当于带检测信息编译后的文件,通过debugger下载到板上调试)。打开 Inserter 主界面后,Inserter 会自动加载并解析用户添加至 PDS中的设计文件,并自动生成输出文件路径。。

当 Inserter 检测到作为其输入网表的 ADF 文件被修改时,会弹出窗口询问用户是否重新载入文件,如果选择重新载入,则当前设置的 net 连接信息将被清空,其他核信息将被保留。

JtagHub 配置:右下角 New DebugCoreUnit 按钮添加 DebugCore,最多可添加 15 个。如不添加 DebugCore,再点击 Next 软件会默认添加一个 DebugCore。同时,用户可在该界面中指定要使用的边界扫描链,也可以指定要使用的 JTAG。

DebugCore 配置:Trigger Parameters、Net Connections 和 PowerOn Init Parameters 为标题的标签页面,分别对应 DebugCore 不同参数的配置

Net Connections:将 DebugCore 的输入信号和用户 design 中的网线连接起来,尚未连

接时,Net Connections 中的所有信号都为红色显示。

PowerOn Init Parameters 选项卡用于设置在上电初始化瞬间信号的捕获条件,了解上电初始化瞬间信号的形态和稳定性。

如下图所示

注意:

在添加观测信号时,有很多信号并不会出现在上图的NET VIEW框内。这是因为这些信号名被优化了,需要在信号定义或者接口的地方加入防优化注释/* synthesis syn_keep=1 */。

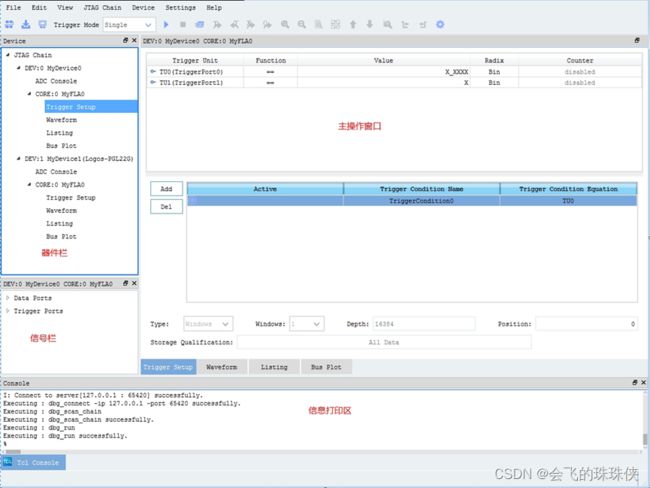

2. Fabric Debugger 是一款界面化的 FPGA 芯片调试工具。直接与 JtagHub、DebugCore 交互,能够实时的配置目标 FPGA、设置触发条件并且观测结果。

操作步骤:

1. 在PDS软件中运行编译综合。

2. 打开inserter软件,配置完inserter参数后,保存并退出。生了.fic文件。

3. 返回PDS软件运行 Flow 中的 Map,PDS 将自动调用插核流程。

4. 打开debugger软件,连接JTAG。扫描设备。打开位流配置界面,选择.sbit文件。同时会自动导入位流文件对应的 .fic 文件。

错误汇总:

1. 如下图错误。显示添加fic文件错误。

添加文件时,.sbit和.fic文件需要是一同编译后产生的两个文件

六 Global include 设置

在PDS软件中,调用全局变量不需在文件中引用,可以直接在左边栏中的全局文件中添加相对应得文件即可。

七 相关约束文件格式及使用范围

1. Sdc 格式文件:该格式是时序约束文件格式,此格式文件只能在没有使用综合工具的情

况下才可加载,里面记录的是 timing 相关的约束信息。

2. Lcf 格式文件:该格式是逻辑约束文件格式,此格式文件只能在没有使用综合工具的情况下才可加载,里面记录的是与逻辑约束相关的信息,如设置属性。Map 过后部分逻辑约束信息会转化为物理约束。

3. Scf 格式文件:该格式文件里面记录的是 timing 相关的约束信息,有无综合工具均可添加,作用于 dev_map 阶段。

4. Fdc 格式文件:该格式文件中包含时序和逻辑约束,是只有在使用了综合工具的情况下

才可以使用。

5. pcf文件,是物理约束文件,可以修改I/O PIN脚。

6. adf格式文件,完成Place & Route后生成的文件。

7. fic格式文件,inserter参数设置后生存的文件,用于在线调试使用

8. sfc格式文件,