Cache Maintenance-通过VA对cache进行clean和invalidate操作-汇编程序详解

目录

cache操作相关寄存器:CTR

程序1:清除指定的一段地址空间的缓存

读取CTR获取cache line 的大小

使用cache line的size作为虚拟地址的步进值,循环清理缓存

程序2:清理某个指定地址的cache line

cache操作相关寄存器:CTR

CTR寄存器负责提供寄存器的基础结构:

其中用于获取数据缓存和指令缓存的cache line 的大小的字段分别为:

- DminLine, bits [19:16] ,为log2(the number of words),单位为word。

- IminLine, bits [3:0],同上。

CTR示例:

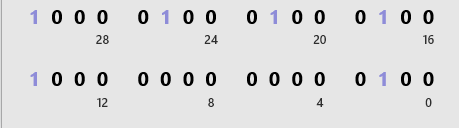

![]() 在这个例子中,CTR的值为0x8444804,二进制编码为:

在这个例子中,CTR的值为0x8444804,二进制编码为:

由此可得:

[19:16]字段的值为0b100,十进制为4,所以一个cache line 的大小为 2^4 = 16 words,为16个字,换成字节为:64字节(1 word = 4 bytes)。

详细解析可参考博文:关于cache maintenance 操作的四个寄存器(CTR,CLIDR,CSSELR,CCSIDR)解析

程序1:清除指定的一段地址空间的缓存

地址空间的基址保存在:寄存器X0

需要清理的地址空间长度保存在:寄存器X1

该代码通过虚拟地址VA,清理清除数据和指令缓存,该虚拟地址用于从寄存器x0中给定的基址和寄存器x1中给定的长度开始的区域。

//

// X0 = base address

// X1 = length (we assume the length is not 0)

// Calculate end of the region

ADD x1, x1, x0 // Base Address + Length

//

// Clean the data cache by MVA

MRS X2, CTR_EL0 // Read Cache Type Register

// Get the minimun data cache line

UBFX X4, X2, #16, #4 // Extract DminLine (log2 of the cache line)

MOV X3, #4 // Dminline iss the number of words (4 bytes)

LSL X3, X3, X4 // X3 should contain the cache line

SUB X4, X3, #1 // get the mask for the cache line

BIC X4, X0, X4 // Aligned the base address of the region

clean data cache:

DC CVAU, X4 // Clean data cache line by VA to PoU

ADD X4, X4, X3 // Next cache line

CMP X4, X1 // Is X4 (current cache line) smaller than the end // of the region

B.LT clean_data_cache // while (address < end_address)

DSB ISH // Ensure visibility of the data cleaned from cache读取CTR获取cache line 的大小

MRS X2, CTR_EL0 // 读取Cache Type Register

UBFX X4, X2, #16, #4 // 抽取DminLine 字段(log2 of the cache line)

MOV X3, #4 // Dminline is the number of words (4 bytes)

LSL X3, X3, X4 // X3=4 * 2^(X4)

寄存器X3中保存的即是数据缓存的cache line的大小,以换算成字节(bytes)为单位。

使用cache line的size作为虚拟地址的步进值,循环清理缓存

SUB X4, X3, #1 // 获取cache line的掩码,假设line size为64(0b1000000)字节,减1操作后,X4的值为0b111111

BIC X4, X0, X4 // 清除基址X0的前6位,相当于对其取整,使得基址能够整除cache line大小的字节数(64),

使用虚拟地址VA作为操作对象清理缓存,一次只能清理一个与该地址对应的cache line。

所以被操作的地址需要能够被cache line 的size整除。

clean data cache:

DC CVAU, X4 // Clean data cache line by VA to PoU

ADD X4, X4, X3 // 由于一个字节对应一个地址,地址加上一个cache line的字节数,相当于指向下一个 cache line的地址

CMP X4, X1 // 地址空间为[X4:X0],判断当前地址是否还在区间内,如果还在,则继续清理操作

B.LT clean_data_cache // while (address < end_address)

DSB ISH // 内存屏障,同步上下文

只需更改DC CVAU, X4 这条指令,就可以对不同的cache进行清理清除操作。

程序2:清理某个指定地址的cache line

X0:保存需要清理的虚拟地址

假设此时cache line 的大小为64(0b100 0000 = 0x40)字节

与程序1同理,清理地址前先判断该地址是否能被cache line的大小整除。

假设X0中保存的地址为0x4400 0010,cache line的大小为0x40字节,不能被其整除。

以该地址为起始地址,需要被清理的一个cache line大小的地址空间范围为:0x4400 0010 ~ 0x4400 0050,该地址空间占了两个cache line:

- 0x4400 0000 ~ 0x4400 0040

- 0x4400 0040 ~ 0x4400 0080

所以清理该地址0x4400 0010开始的一个cache line大小的缓存,需要清理两个cache line。

以下是具体程序:

AND X2, X0, #0x3F //0x3F = 0b0011 1111,将X0的低6位保存在X2中,相当于整除cache line 大小后的余数

ADD W1, W2, #64 //

BFI X0, XZR, #0, #6 //比特插入,将X0的低6位置零DCLC_LOOP

DC CIVAC, X0 // 对数据缓存执行清理清除命令

ADD X0, X0, #64 // 指向下一个cache line的首地址

SUBS W1, W1, #64 //检查余数是否为零

B.GT DCLC_LOOP // 如果不为0,则开始下一个cache line 的清除

ARMv7中关于Cache Maintenance操作的CP15指令:

ARM Architecture Reference Manual ARMv7-A and ARMv7-R edition

![]()

![]() ARMv8中对应的指令ARM Cortex-A Series Programmer's Guide for ARMv8-A

ARMv8中对应的指令ARM Cortex-A Series Programmer's Guide for ARMv8-A

![]()

![]()