Icarus Verilog

Icarus Verilog 是一个Verilog仿真工具,以编译器的形式工作,将以verilog编写的源代码编译为某种目标格式。如果要进行仿真的话,可以生成一个vvp的中间格式,由其所附带的vvp命令执行。

https://github.com/steveicarus/iverilog

Icarus Verilog编译器主要包含三个工具:

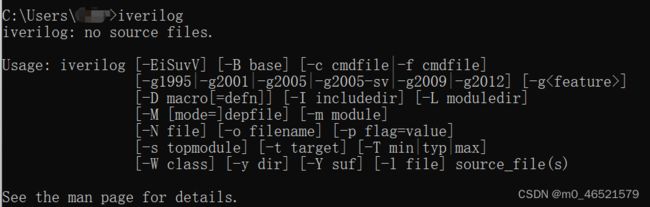

iverilog:用于编译verilog和vhdl文件,进行语法检查,生成可执行文件。

vvp:根据可执行文件,生成仿真波形文件。

gtkwave:用于打开仿真波形文件,图形化显示波形。

参数-o:[-o filename] 用于指定生成文件的名称。如果不指定,默认生成文件名为a.out

iverilog -o test test.v参数-y:[-y dir] 用于指定包含文件夹,如果top.v中调用了其他的.v模块,top.v会编译提示。找不到调用的模块,需要指定调用模块所在文件夹的路径,支持相对路径和绝对路径。

iverilog -y D:/test/demo led_demo_tb.v参数-I:[-I includedir]如果程序使用`include语句包含了头文件路径,可以通过-i参数指定文件路径,使用方法和-y参数一致。

参数-tvhdl:把verilog文件转换为VHDL文件

testbench文件中有几行iverilog编译器专用的语句,如果不加的话无法生成vcd文件

initial

begin

$dumpfile("wave.vcd"); //生成的vcd文件名称

$dumpvars(0, led_demo_tb); //tb模块名称

endprbs4.v

module prbs4(clk, rst_n, out, out_invalid_n);

input clk;

input rst_n;

output reg out;

output reg out_invalid_n;

reg [3:0] a;

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

a <= 4'b1000;

end

else begin

a[3] <= a[3]^a[0];

a[2] <= a[3];

a[1] <= a[2];

a[0] <= a[1];

end

end

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

out <= 1'b0;

out_invalid_n <= 1'b0;

end

else begin

out <= a[0];

out_invalid_n <= 1'b1;

end

end

endmoduleprbs4_tb.v

`timescale 1ns / 1ps

module prbs4_tb();

reg clk;

reg rst_n;

wire out;

wire out_valid_n;

integer i;

prbs4 uut(clk, rst_n, out, out_valid_n);

initial begin

$dumpfile("prbs4.vcd");

$dumpvars(0, prbs4_tb);

end

initial begin

rst_n = 1'b0;

#20 rst_n = 1'b1;

end

initial begin

clk = 0;

for(i=0; i<45; i=i+1) begin

#1 clk = 1;

#1 clk = 0;

end

$display("test complete");

end

endmodule(1)编译

cmd输入:

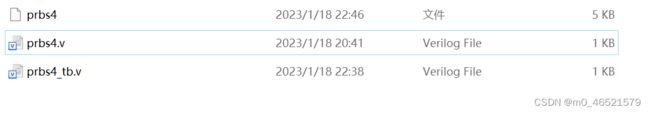

iverilog -o prbs4 prbs4.v prbs4_tb.v得到

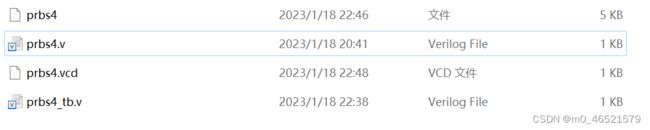

(2)生成波形文件

cmd输入:

vvp -n prbs4 -lxt2得到

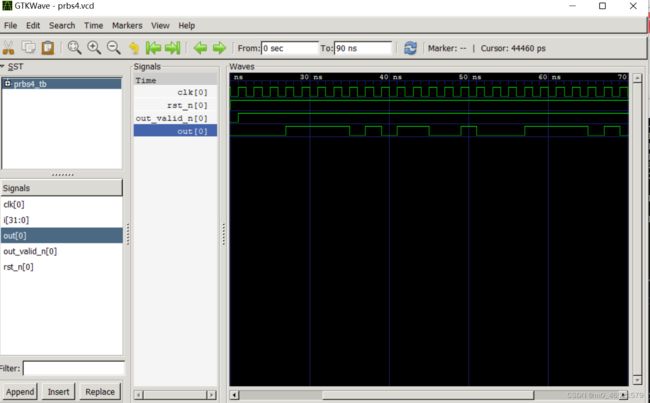

(3)打开波形文件

cmd输入:

gtkwave prbs4.vcd得到

参考

https://blog.csdn.net/zkwlyz163988/article/details/123437329

https://blog.csdn.net/u013353078/article/details/122720947

https://blog.csdn.net/whik1194/article/details/114703141