FPGA技术面试题

一、串行接口

1、 串行接口与并行接口区别

串行接口是数据线一根线,通过串行协议传输数据,比如uart

并行接口是一个数据在多根数据线并行传输,比如rgb888、rgb565等等

2、 什么是总线,有什么特点

核心:多个设备共用数据线

3、 Spi有几种模式,分别是什么

4种,CPHA CPOL

分别是 scl默认电平低电平、高电平两种

sda在时钟的第一个时钟沿、第二个时钟沿数据生效两种

4、i2c和spi总线如何实现多机通信的,简述

I2c通过呼叫应答方式,i2c每帧数据都会先发设备地址指明数据发给谁的,读谁的;

Spi通过片选信号,spi通信前先拉低对应从机的片选,然后和收发数据

5、什么是同步时钟和异步时钟

同步就是有时钟信号,实现每位数据的有效位置如spi异步,没有时钟信号标定数据的位置

6、简述一下什么是单工、半双工、全双工通信,举个例

单工,只能发或者收数据

半双工,可以发也可以收,但是收发不能同时进行

全双工,可以发也可以收,收发可以同时进行

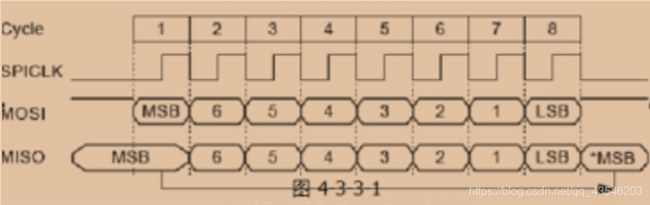

7、画出spi主机四种模式波形图

8、画出i2c读、写模式完整波形图

Start addr ack data ack data nack stop

Start addr ack data ack data nack stop

9、画出异步串口发送一个字节完整波形图

10、串行接口发送接收是按多少有效数据位的格式

按字节,8bit

11、收发数据的时候,LSB是什么意思

低位先发

12、简述异步串口uart发送电路设计思路

一个计数器产生波特率时间,一个计数器产生发送第几bit,使用移位或者case发送对应位

13、为什么异步串口发送协议起始位是低电平,停止位用高电平,能不能用高电平,为什么?

高电平可以被低电平拉低,发送的时候拉低对方设备能检测的到低电平,不能用高电平起始,高电平不能拉高低电平

14、i2c总线上为什么要用上拉电阻

总线默认一般是开漏,需要上拉电阻设置默认高电平

15、异步串口如果txd和rxd短路会怎样,如何避免和排查

发送接收是同一数据,应用层协议做好收发应答

16、异步串口txd对gnd短路会怎样

发送数据发不出去,接收方一个字节为0x00

17、异步串口rxd对gnd短路会怎样?

会接收到一个字节0x00,收不到对方发送数据

18、异步串口txd和rxd分别与通信设备断开会出现什么现象?

Txd断开,发送数据对方不能收到,对方发数据可以收到

Rxd断开,发送数据,对方能收到,对方发数据不能收到

19、异步串口通信中,gnd需要接到一起吗,为什么?

需要,电气上的电平是对gnd做参考0电压

20、异步串口校验位的奇、偶校验的原理

奇校验:让所有这个字节的数据中出现奇数个1,比如,1000110(0)则必须添0,

这样原来有3个1已经是奇数了,所以添上0之后1的个数保持为奇数

偶校验:让所有这个字节的数据中出现奇数个1,比如,1000110(1)则必须添1,

这样原来有3个1已经是奇数了。所以添上1之后1的个数保持为偶数。

21、spi通信中,两个设备都是主机模式,会出现什么情况

两个设备只有一个启动的话,读写数据都是错误没有用的,

两个设备都启动的话,无法建立通信

22、spi通信中,如果clk与gnd短路或者断开会怎样,如何排查

从机无法收到数据,主机无法读出数据

排查:示波器、逻辑分析仪、quartus自带的signaltap任意一种都行

23、spi通信中,如果cs断开会怎样,如何排查

从机无法收到数据,主机无法读出数据

排查:万用表、示波器、逻辑分析仪、quartus自带的signaltap任意一种都行

24、spi通信中,如果mosi和miso短路会怎样,如何排查

收发数据相同

排查:万用表打短路

25、i2c通信中,是如何确定设备存在正常通信

主机发送设备地址的情况下,看设备是否应答,无应答说明设备不存在或者通信线路异常或者器件损坏

26、i2c通信中,主机发送数据从机没有应答该如何处理

设置超时时间,在时间内没有应答通信失败

27、i2c通信中,7位地址,一个总线理论上可以和多少个从机通信

128

28、i2c总线,sda和gnd短路会怎么样,如何排查

Read到数据都是0x00

排查:万用表打短路

29、i2c总线的时钟频率最大多少,通信时可以都用最大吗,为什么

高速模式3.4M,不能都用,i2c通信时钟频率是从机决定的,如果一个总线上有不同时钟频率的从设备,需要切换时钟频率通信

二、sdram

1、sdram的作用是什么?

暂存数据

2、举个例fpga上用sdram的地方,为什么要用?

摄像头采集图像的时候,缓存用sdram

因为fpga内部的ram区域不足以存储图片的大小,所以需要一个存储区域作为缓存

三、soc

1、 什么是soc黄金参考工程

黄金参考工程是厂商出厂自己做的一个参考工程

2、 简述verilog HDL pwm代码在quartuII封装成ip,主要是哪几步操作

1).根据avalon总线时许,编写avalon接口读写pwm寄存器

2).添加到quartus在quartus II platform designer上面添加新的compnement修改输出接口

3、 简述hls如何封装成ip并在soc上使用

通过c语言编写逻辑模块和测试模块,验证功能,观察波形图,查看html报告,通过hls编译器编译生成ip,添加到quartus上面,

4、 avalon总线有哪些类型的接口

mm slave、 mm master、 流接口

5、 soc应用程序访问ip流程是什么

1. 映射avalon总线的地址

2. 计算ip的地址

3. 映射接口地址

4. 操作

6、 soc自定义常用外设ip使用的是avalon那种接口

Avalon mm slave接口

7、hps自己的外设和avalon的外设区别

Hps自己的外设是固核,不用也不可以拿来做其他的逻辑

Avalon外设是软核,不用的话逻辑资源可以拿来做其他的

8、软核、硬核、固核是什么,各有什么特点

软核:综合之前的寄存器传输级(RTL) 模型,灵活性高、可移植性强,但预测性低有不确定风险

硬核:经过验证的设计版图,设计人员不能对其修改与软核实现方式相比,硬核可以把功耗降低5~10 倍, 节约将近90% 的逻辑资源

固核:带有平面规划信息的网表,通常以RTL 代码和对应具体工艺网表的混合形式提供。

固核的设计灵活性稍差,但在可靠性上有较大提高

9、soc上面,linux下是如何访问接口的

使用虚拟内存映射,主要是mmap函数将总线地址拿到,通过avalon桥偏移地址找到avalon桥地址,通过hps0.h文件里面的外设偏移地址计算外设地址,通过接口定义的顺序和接口类型直接把接口地址计算出来,通过指针直接访问接口

10、platform designer上面一定要添加cpu吗

可以不用

四、hls

1、hls可以对算法做那些方面的优化

优化面积、优化执行时间

2、流接口读写操作有那些操作函数,区别是什么

read、write、try_read、try_write

3、hls生成ip默认会有哪些信号

start、done、busy、stall

4、数据类型可以怎么优化

使用ac数据类型减小位宽,从而优化面积,减小位宽相应做计算也会增快

5、简述一种面积换时间和时间换面积的方法

面积换时间:使用hls循环展开,复制循环内部的电路

时间换面积:将大部分相同电路的做成一个,使用循环,然后每次传入不同的参数

6、 简述hls图像灰度化和二值化原理

灰度化:将图片像素点提前出来,拆分成红绿蓝三个分量,用Gray = R*0.299 + G*0.587 + B*0.114公式分别代入,R红色分量G绿色分量B蓝色分量,Gray对应输出灰度值,然后将Gray分别填充三个分量合成像素点,合成图片;

二值化:将图片像素点提前出来,拆分成红绿蓝三个分量,用y= gray > b? 255:0公式分别代入,b设定阈值,gray灰度值,y是输出,然后将y分别填充三个分量合成像素点,合成图片

7、简述hls图像增亮原理

将图片像素点提前出来,拆分成红绿蓝三个分量,用y=ax+b公式分别代入,a对应对比度,b对应亮度,x对应分量,y对应输出,然后合成像素点,合成图片

8、简单说一下封装全连接神经网络手写体成ip流程

1. 通过python神经网络工程提取权重和偏置,修改为h文件

2. 用python工程里的读取图片程序,将图片转换成h文件,数组形式

3. 通过全连接神经网络算法编写c程序,封装成mm slave接口

4. 添加权重、偏置、图片的h文件编写mian测试

5. HLS编译器编译windows平台运行程序验证结果

6. HLS编译器编译生成quartus可识别的ip

9、给一段c语言程序代码,在fpga上面做加速,能从那些方面做提升,简述过程

1. 时间上的优化加速

2. C语言里面存在循环可以展开减少执行时间

3. 里面的变量使用ac数据类型,减少数据位宽优化面积和执行时间

4. 复杂的计算换成简单的计算,比如除以2换成右移1位

5. 函数参数接口使用avalon接口减少位宽,优化面积

6. 接口使用稳定参数优化寄存器级数减少时间

10、hls循环优化情况在哪里可以查看

html报告里面的循环报告

11、hls展开系数代表什么意思

复制电路的个数

12、hls稳定参数优化的是什么

简单来讲就是将接口优化成wire线型变量,减少寄存器传入级数,从而优化时间

五、存储

1、如果一个flash一个扇区写次数寿命是1万次,现在有一个数据需要写100万次,请问如何解决,简述思路

存储的时候记录存储写操作次数,每5000次写之后,将存储位置切换到另一个位置

2、 flash和e2prom存储的有什么差异

flash是按扇区读写,一次必须读写一个扇区,速度较快,一般用于大数据量存储;

e2prom是按字节读取,一次可以只读一个字节,速度较慢,一般用于小数据量存储

3、ram、sram、dram、sdram、ssram、ddr的特点和差异

Ram是随机存储器,是一个通称,掉电数据丢失

Sram静态随机存储器,加电情况下数据不丢失,掉电数据丢失,不需要刷新

Dram动态随机存储器,需要不停的刷新数据,因为是电容存储要不停的充电,掉电数据丢失

Sdram同步的dram,需要不停的刷新数据,掉电数据丢失,需要同步的时钟读写,读写速度较快

Ssram,同步的sram,不需要刷新,掉电数据丢失,需要同步时钟,速度较sdram快

Ddr ddr sdram,双倍速度sdram,就是sdram的升级版,在时钟的上升沿和下降沿都读取数据

4、FIFO存储有什么特点

先进先出,队列的形式

5、 ram和rom有什么差异

ram读写速度快,rom读写速度慢,

ram掉电数据丢失,rom掉电数据不丢失

六、开发流程

1、 在开发阶段如果仿真异常如何排查问题

先排查模块,再排查模块内部寄存器,逐级排查

2、 在开发阶段如果仿真正常,烧写到硬件异常如何处理

逻辑分析仪测量硬件波形,对应返回排查是哪个模块,再排查模块内部寄存器,如果程序比较混乱直接重写

3、 状态机有几种,分别是什么,有什么区别

时序逻辑电路按照输入输出关系有两种状态机,摩尔状态机、米莉状态机;

摩尔状态机就是输出与输入无直接联系,米利状态机是输出与输入有直接联系

4、 按键为什么要消抖,机械按键本身会有弹性,不消抖会怎么样?

机械按键在按键按下和弹起的瞬间,本身因为弹性作用会产生机械抖动,机械抖动会造成电路上通断不稳定出现多次通断,进而导致输入电平变成带毛刺的信号

如果不消抖,会因按键异常而产生多次按键按下的结果

5、 什么情况下可以不消抖,消抖方法有哪些?

当按键功能只有一个单一功能的时候,比如一个按键就是开,输入几次都是开,那就可以不需要消抖

消抖方法可以分为状态机、延迟计数法、

6、FPGA设计流程

功能定义-->设计输入-->功能仿真-->综合优化-->综合后仿真-->布局布线-时序仿真-->板级仿真与验证-->调试

7、仿真的作用是什么,为什么要仿真?

仿真模块的逻辑在设定输入下输出是否正确

仿真模块的时序在设定输入下输出是否正确

仿真模块的逻辑在非设定输入下输出是否异常

七、Verilog HDL

1、一个 reg 变量可以在多个 always 块里写值吗,为什么?

不可以,hdl 语言最后会生成电路,多个 always 同时赋值会造成硬件冲突,甚至编译器会报错

2、仿真的时候如何设置基准时间和精度?

1.仿真工具上面可以设置

2.testbench 里面可以直接写 `timescale 1ns/1ps 基准时间 1ns,精度 1ps

3、Verilog HDL 仿真中产生随机数和显示结果的方法

Num = $random;

$display("at time %d duty is %d\n",$time,duty);

4、Verilog HDL 的循环实际和 C 语言的区别

Verilog 是复制电路,循环是并行执行

C 语言是重复执行一段代码,循环是串行执行

八、硬件工具使用

1、万用表、示波器、逻辑分析仪可以测量那些东西,用来测些什么?

万用表主要用来测试电压、电流、通断、电阻、电容等,缺点只能看有效值,不能看实时值示波器主要测量模拟信号实时值,如频率、周期、幅值等,缺点是通道较少没有协议解析

逻辑分析仪主要抓取多路通道的波形,解析编码协议,缺点是只能看数字信号,不能看模拟信号

2、万用表测量电压是什么电压,fpga 输出 50%的占空比的 pwm 波测出来是多少?

有效值,1.65v

3、示波器测量的电压是什么电压,fpga 通过 dac 输出正弦,测量出来是什么?

实时值,测量出来是一个幅值为 dac 基准电压的正弦信号

4、逻辑分析仪是以什么电压区分电平的,输入幅值 3v 的一个正弦信号,逻辑分析仪读取什么?

低端逻辑分析仪是以 ttl 电平,默认 0.7v 以下低电平,1.5v 以上高电平,中间保持

高端的逻辑分析仪有电平设置功能,自己设置高低电平的电压阈值

输入正弦信号软件中为方波

5、现有一个产品出现故障,没有任何输出现象,我们应该先测什么,用什么测

答:输入电源电压,所有芯片电压电压,

万用表或者示波器

九、开发工具

1、quartus 里面编译成功之后生成什么文件

Sof

2、fpga 可以从那几个地方配置硬件

Fpga 内部 ram,外部 epcs,还有 soc 的话可以从 sd 卡配置

3、管脚约束的方法有那些

1.管脚较少的情况下可以使用 Quartus 上面的 pin planner 手动修改

2.管脚较多的情况下可以编写 tcl 脚本,使用 tcl scripts 运行脚本

十、通信

1、曼彻斯特编码

1 用低电平加高电平上升沿表示 ;0 用高电平加低电平下降沿表示

双方约定好波特率异步收发

2、Nrz 非归零编码

1 用电平跳变表示 0 用电平保存表示

双方约定号波特率异步收发或者同步时钟收发

3、编码的作用是什么,为什么要编码

通信上面,大部分都是串行,编码的目的是实现一个字节在串行上面的数据传输,不同的编码

有不同的侧重点,比如无线编码的一般都侧重考虑干扰的情况,普通的有线串口只考虑收发速度