vivado中ila的使用方法记录

ILA工具生成方法

一、 ILA工具介绍

在FPGA的开发中,当完成代码设计后,为了验证代码的准确性和各种不同条件下的可靠性,往往需要优先想到通过逻辑仿真进行相关验证。使用逻辑仿真进行验证虽然可以周密的考虑给出不同输入条件下的输出结果或交互结果,但是也其相对局限性:使用仿真需要设计人员写testbench代码,从而增加代码的书写量,随之而产生提高验证工作的门槛和排除错误的工作量等一些列问题。特别是对纲入门的人,有时候难对testbench的设计方法优准确的把握,甚至testbench的书写规则和设计源码的规则混淆了,从而对学习源码设计参数适得其反的效果

使用仿真进行逻辑验证还有另一个局限性,其体现在:有些驱动模块的模型无法获取的情况下,仿真几乎是一项不可能完成的任务。比如,在没有ddr2、ddr3、摄像头模组等代码模型的条件下,设计的驱动模块缺乏能够模拟真实外部期间的数据交互环境,从而很难实现仿真的验证过程。

最后,仿真大多适合以时间为标尺,对条件变化有清晰的时间节点预设的验证需求。这就导致对工程的验真很难形成FPGA芯片、计算机和人的三者互动,也很难通捕捉随机触发条件而进行验证,从而使得触发条件的选择,受较大的局限性。

能够较好解决以上问题的一种方案,是考虑使用逻辑分析仪。而采用传统的逻辑分析仪又存在额外的设备采购开销。得益于FPGA的硬件定制自由属性,FPGA生产设计公司从自身发掘潜力,并配套以软件开发环境,推出了在一定程度上能够代替逻辑分析仪的在线调试工具。

FPGA两大厂商都有自己的在线调试工具。Intel的SinganlTap,xilinx的ILA工具。

二、方法

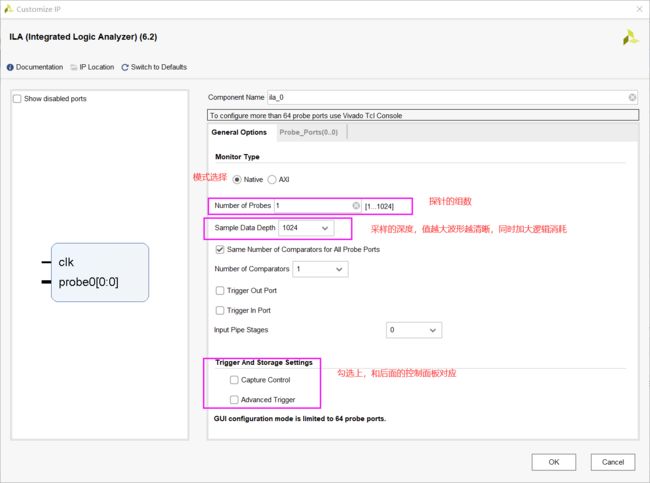

方法一:添加ILA IP核

将ila IP核在顶层文件中例化。例化模板可以在ip source–>ila_o–>instantiation template–>ila_0.veo中复制过来。

然后编译生成bit流文件下板验证即可

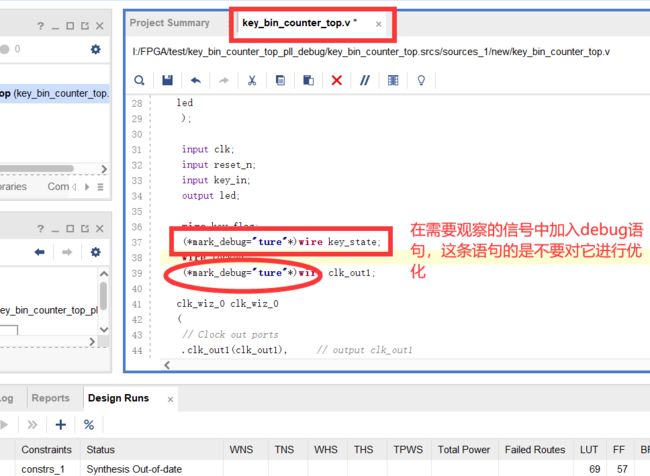

方法二:使用Debug标记创建ILA调试环境

直接使用debug标记的方法创建ILA调试环境,能够弱化抓线信号的位宽对抓线调试的影响。

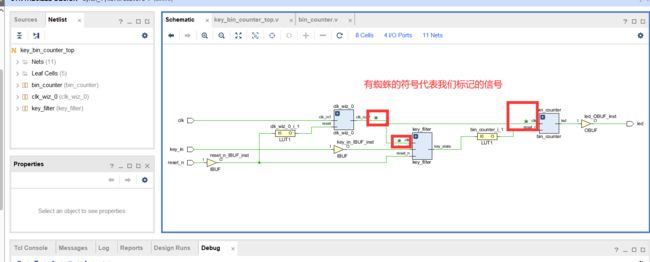

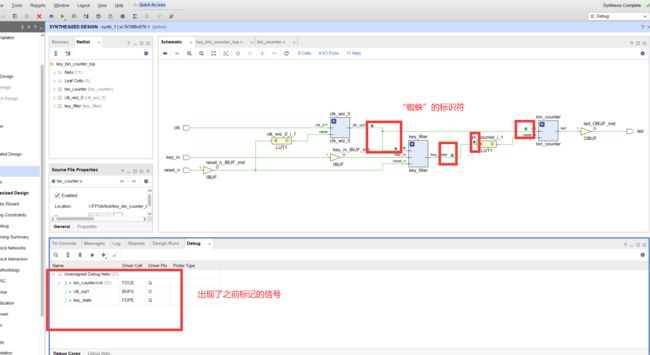

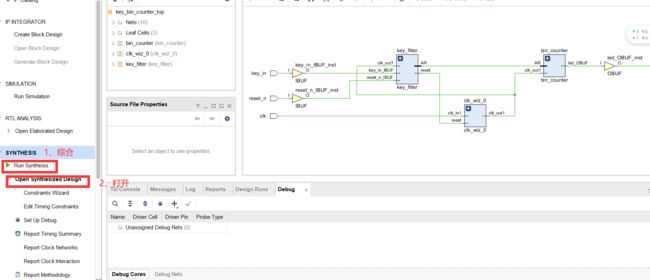

标记完之后对工程进行编译。编译完毕后点击open synthesized design ,再选择debug。

到这步之后,我发现我的图中并没有出现蜘蛛的符号,查看控制台发现警告:

[Netlist 29-72] Incorrect value 'ture' specified for property 'mark_debug'. Expecting type 'bool' with possible values of '1,0'. The system will either use the default value or the property value will be dropped. Please verify your source files.

Resolution: Please check the value of the property and set to a correct value.

大概的意思是:[网表29-72]为属性“mark_debug”指定的值“ture”不正确。应为可能值为“1,0”的类型“bool”。系统将使用默认值或删除属性值。请验证您的源文件。

解决方案:请检查属性的值并设置为正确的值。

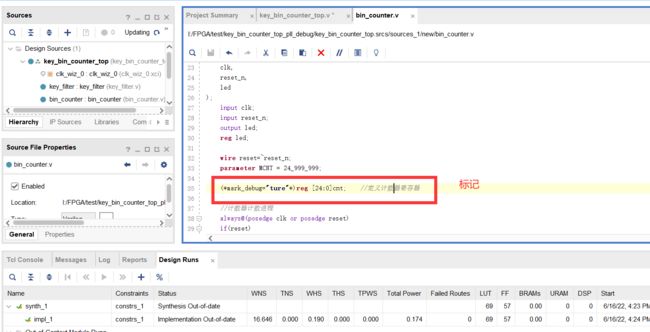

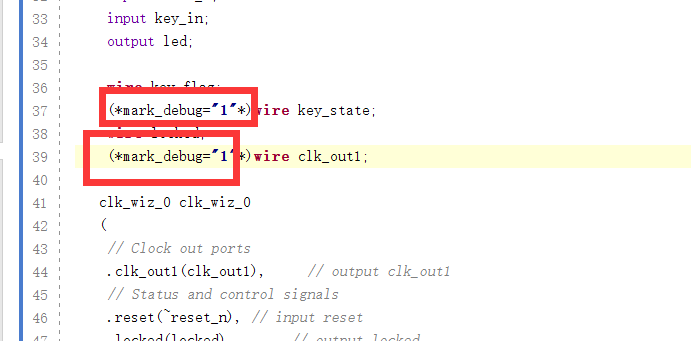

然后我根据提示将语句中的”ture“改为”1“,如下图

改好的结果:

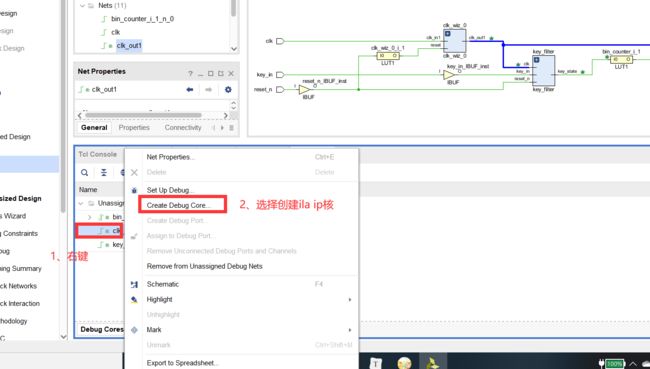

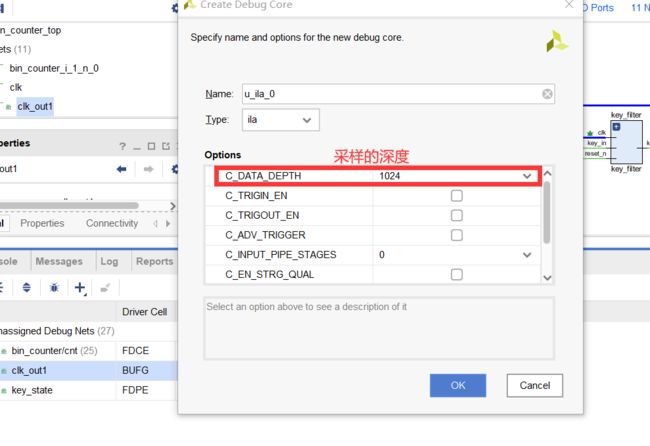

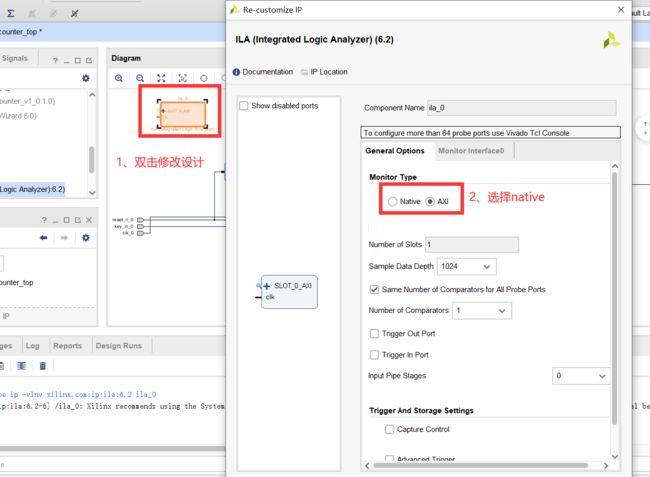

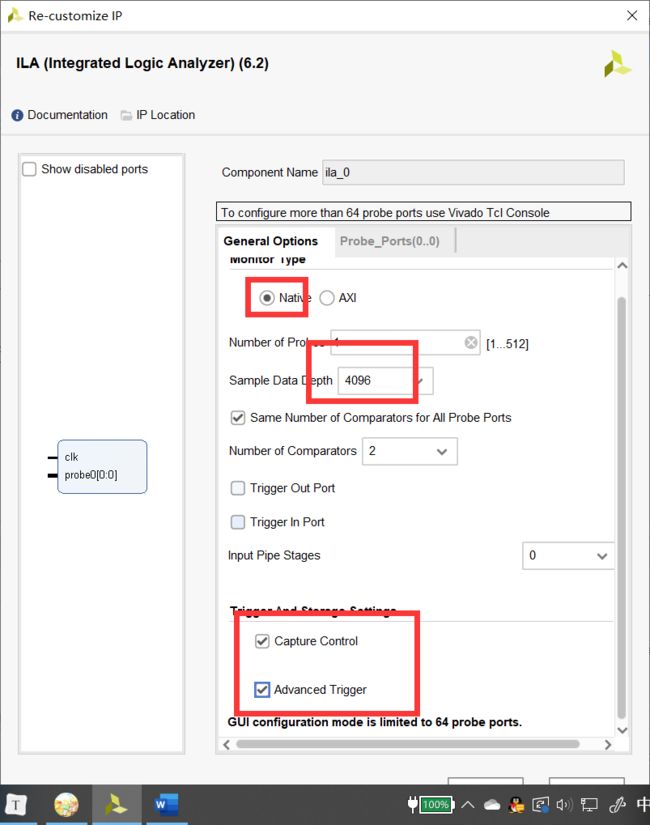

解决问题之后,继续:创建ila ip核

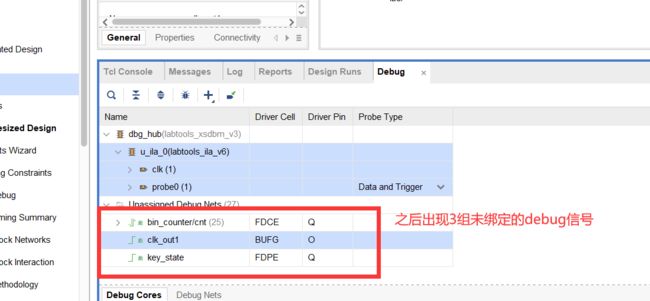

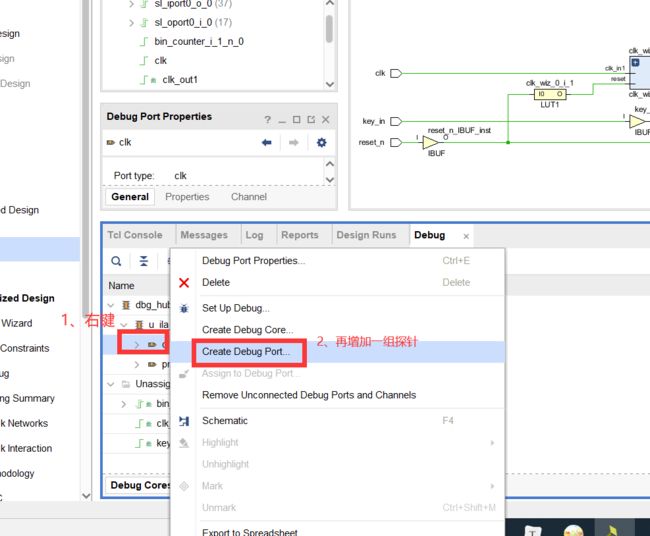

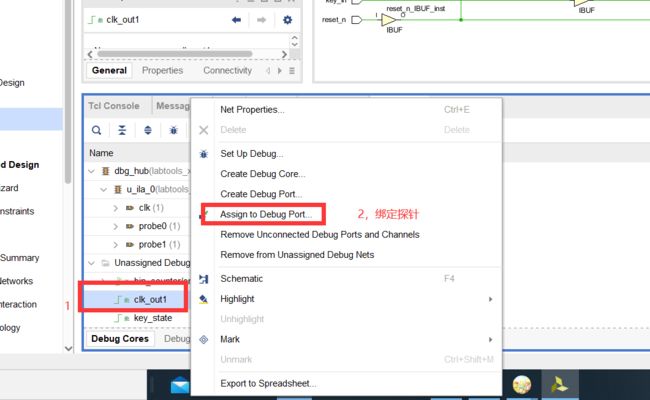

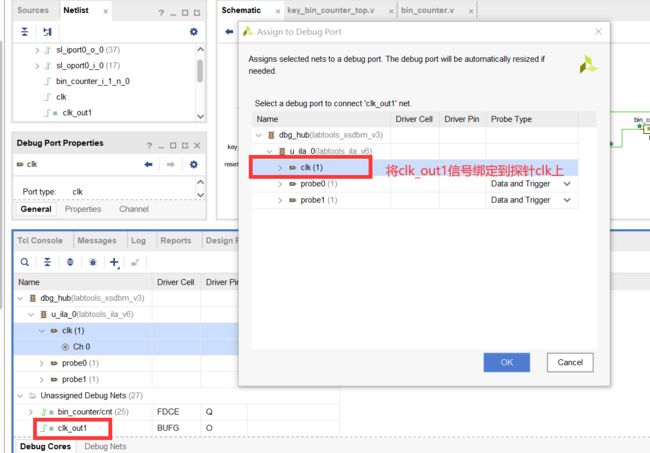

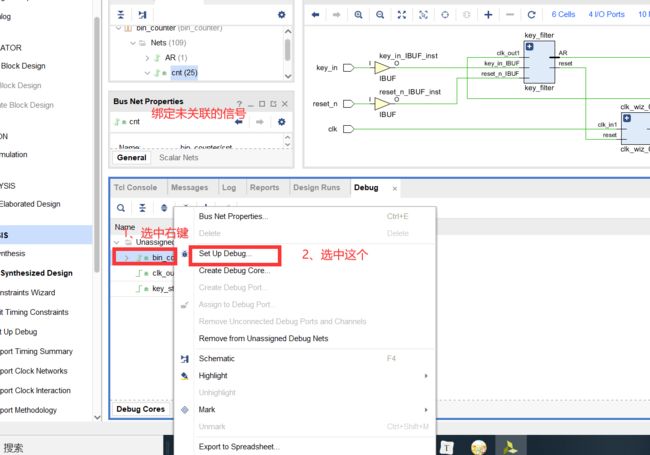

接下来将需要观察的信号绑定到探针上:

绑定完成之后就可以生成bit流文件,运行ila。

注意:在使用mark_debug方法抓线完成调试工作之后,需要记得删除源码中的mark_debug标记。否则,不但代码会留下杂乱的调试痕迹,而且被标记的信号会保持占用工程的逻辑资源,导致工程总逻辑资源使用量增大。

方法三:使用路径标记核set up debug 菜单创建ILA调试环境。

可以通过在综合后的原理图上直接进行调试标记,而简单的锁定需要观察的信号。这样,我们就不需要在代码中进行标记,也不需要承担在调试完成后忘记在代码中删除mark_debug标记的风险了。

在vivado的 tcl console中输入:reset_project。可以将工程复位到ready状态。

然后直接生成bit流文件上板调试。

方法四:使用IP核在block design界面创建ILA调试环境

首先创建block design工程,添加ila IP核。

把线连接好之后生成顶层

点击generate bitstream生成bit文件。

三、生成bit文件,板级调试

采用ila IP核的方法生成比特流下载到板子上。

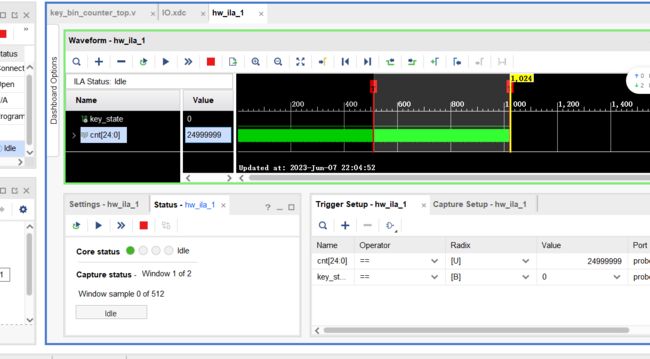

1、波形显示窗口,可以通过点击十添加想查看的波形的信号。因为在IP设置中对探针设置的时候,cnt和 key_state信号的 Probe Trigger or Data 属性设置为了“DATA AND TRIGGER”,所以这里可查看的信号有cnt和 key_state。当然,通常在下载完程序后,ILA能够非常智能的识别出设计师期望观察的信号,同时,在右键菜单也可以找到删除观察信号的指令。这样,有限的窗口面积就可以被充分利用,自由调配和增减所需观察信号的条目。

2、ILA core的状态控制和显示窗口

按钮①:设置采样执行过程为循环采样。如果该按钮按下,则其外框为灰色线条,且框内颜色微深于面板背景色。

按钮②:启动采样按钮。按下后将启动ILA采样。根据是单次采样还是循环采样,根据是有条件触发还是无条件触发,启动后会呈现ILA状态的周期性变化或等待触发条件的到来。

按钮③:无条件执行ILA采样。

按钮④:停止采样按钮。如果处于循环采样状态,按下此按钮后,本轮正在执行的循环结束则停止采样。

状态栏⑤:状态栏⑤由5个空心圈组成,唯一的实心绿色点所处的位置表征ILA的运行状态。

状态栏⑥:已采集的点数占总采集点数的关系。由于图1.7-8中TRIGGER设置的在波形窗口2048点展示,而 TRIGGER还未到来,所以采样完成了2048个点而正等待TRIGGER。

状态栏⑦:以进度条的方式结合状态名称,标明当前所处的状态以及采样过程中执行状态的百分比。

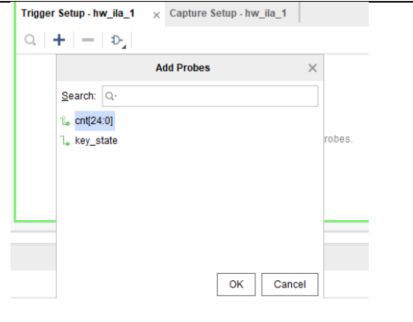

3、点击窗口内➕ 添加产生触发条件的信号

点击后,在弹出的Add Probes窗口选择需要添加的信号。因为在IP设置中对探针设置的时候,cnt和 key_state信号的Probe Trigger or Data 属性设置为了“DATAAND TRIGGER”,所以这里可查看的信号有cnt和 key_state。

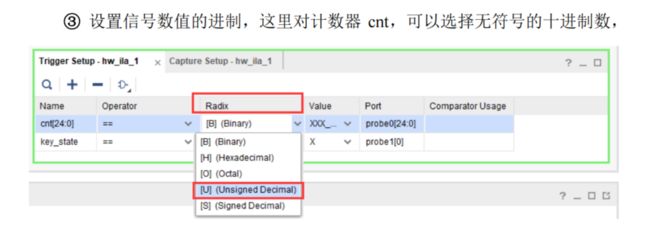

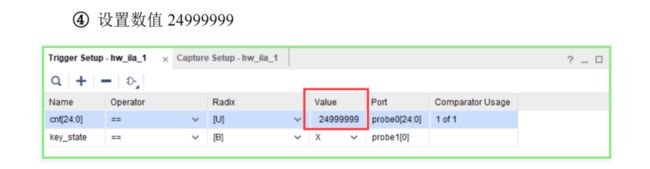

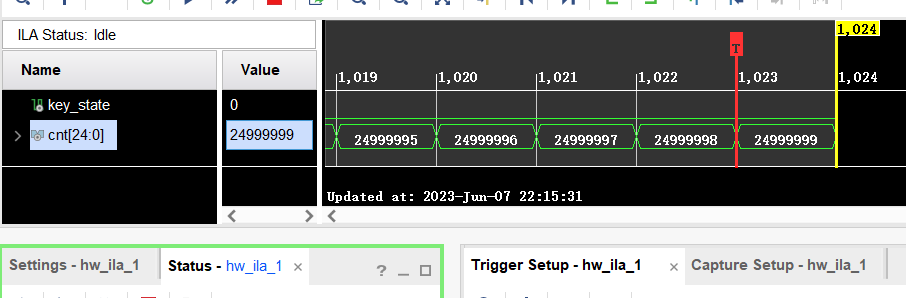

添加好触发信号后,需要设置触发条件,触发条件有多个地方可进行设置。假设现在我们想设置在满足cnt =- 24999999并且 key_state为时触发进行一次信号的抓取,设置如下:

设置触发情况,下面是设置多个信号产生触发信号时的条件,与、或、

同或、异或,这里根据需求设置“Set Trigger Condition to‘Global AND’”表示。

设置好之后按下开发板的按钮

结果:T的位置就是触发的位置

https://www.bilibili.com/video/BV1uG4y1q7pT/?p=7&spm_id_from=pageDriver&vd_source=58dae662e3d0551fcf0adfdc00c4e557

--晓凡 2023年6月6日于桂林书