【数字IC基础】从触发器到亚稳态

从触发器到亚稳态

- 单稳态和双稳态

-

- 三态门(高阻态)

- 单稳态电路

- 双稳态电路

- 锁存器

-

- SR锁存器

- 触发器

-

- 电平触发的触发器

-

- SR触发器

- D锁存器(电平触发的D触发器)

- 边沿触发的触发器

-

- 边沿触发 D 触发器

- 脉冲触发的触发器

- 建立时间和保持时间

- 恢复时间和去除时间

- 亚稳态

-

- 亚稳态的产生

- 减少亚稳态的方法

-

- 降低时钟频率

- 多级触发器

- 亚稳态检测电路

- 异步复位同步释放

- 单bit异步信号慢时钟域到快时钟域

- 脉冲信号快时钟域到慢时钟域

- 多bit异步信号同步器

- 参考资料

单稳态和双稳态

数字电路的信号只有两种状态:逻辑低或逻辑高,即通常所说的0状态或1状态、0电平或1电平。

单稳态电路指的是该电路的输出信号只能在一种状态(逻辑高或低)下是稳定的,而当电路的输出处在另一种状态下时不能稳定的保持住,会自动的回到稳定的状态。

双稳态电路就是说电路的输出信号在两种状态下(0或1)都可以稳定的存在。

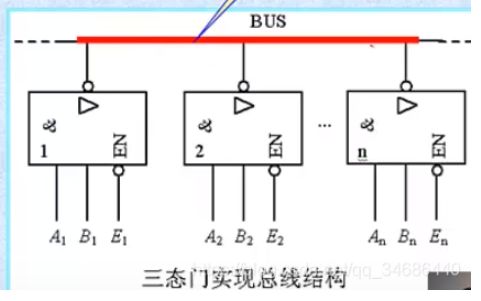

三态门(高阻态)

在看数字电路的资料时,有时看到“三态”的字样,三态指的是除了前面说的逻辑状态0、逻辑状态1以外,还有称为“高阻态”的第三种的状态。“高阻态”指(信号)线呈高阻抗状态,就像信号线“断开”一样。“高阻态”应理解为**“电路”的一种状态**而不是“信号”的一种状态(数字信号只有0或1)。

高阻态是电路的一种输出状态,既不是高电平也不是低电平,如果高阻态再输入下一级电路的话,对下级电路无任何影响,可以理解为断路,不被任何东西所驱动,也不驱动任何东西

高阻状态相当于隔离状态,因为高阻状态电阻很大,相当于开路。

通常三态门有一个EN使能控制端,用于控制门电路的通断(即通过EN使能控制,处于高阻态就是电路断开,非高阻态就是电路导通)

现如假设EN高电平有效,

当EN=1时,门电路导通,三态门电路呈现正常的 0 或 1 的输出;(电路导通)

当EN=0时,门电路断开,三态门电路给出高阻状态的输出;(电路断开)

高阻态相当于该门和它连接的电路处于断开的状态。(因为实际电路中你不可能去断开它,所以设置这样一个状态使它处于断开状态)。

三态门是一种扩展逻辑功能的输出级;三态门同样也是一种控制开关。(通过控制三态门是高阻态还是非高阻态,来表示三态门是导通还是断开。

三态门的应用:

① 实现总线结构

通常在数据总线上接有多个器件,每个器件通过OE/CE之类的信号选通。同一时刻只有一个设备选通,用于数据传输;其他设备处于高阻态,相当于没有接在总线上,不影响其它器件的工作。

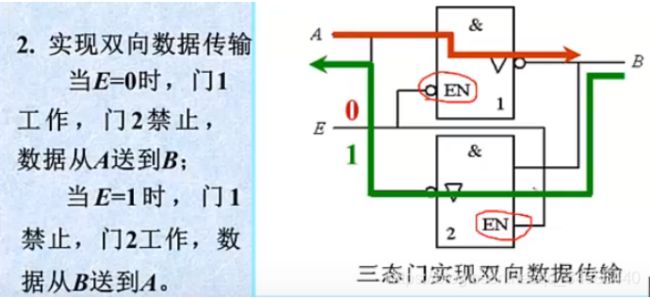

② 实现数据的双向传输

单稳态电路

电路只能保持在一个稳定状态上,当施加触发脉冲时,电路翻转,变为另一个状态,但这个状态无法稳定(称之为暂稳态)。不管触发脉冲撤销与否,电路都要自动回到原来的稳定状态。下一个触发脉冲的到来,再次重复一下这个翻转又返回的动作。

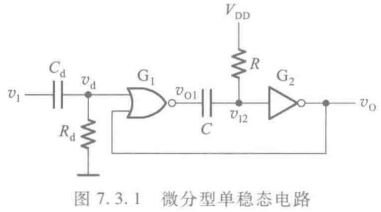

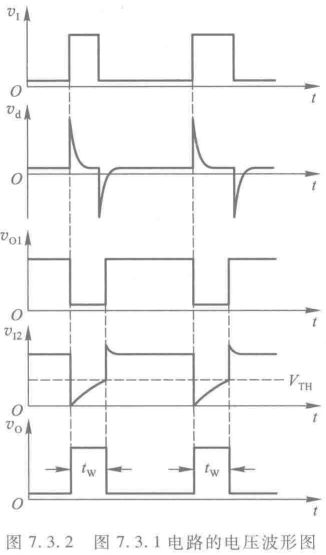

单稳态电路的暂稳态通常是靠RC电路的充放电过程来维持的,根据RC电路的不同解法,可以分为微分型和积分型。

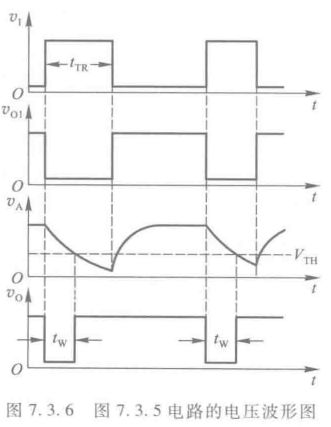

积分型单稳态电路:

积分型单稳态电路的工作过程:

双稳态电路

电路可以保持在两个稳态上,当施加触发脉冲时,电路翻转,变为另一个稳态。触发脉冲撤销后,能够保持在这个稳定状态上,直到下一个触发脉冲的到来,才再次改变状态。

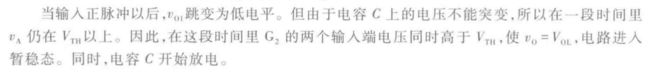

因为双稳态电路有两个稳定的状态,因此才可以拿它们来存储数据,交叉耦合反相器、锁存器和寄存器都是双稳态器件。

锁存器

交叉耦合反相器没有输入,是存储不了输入的数据的了,因此就需要有输入的类似“交叉耦合反相器”结构的双稳态电路,锁存器应运而生了,常见的基本的锁存器包括S-R锁存器、D锁存器等。

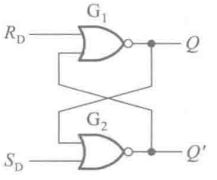

SR锁存器

SR锁存器(Set-Reset Latch)是静态存储单元的基本结构之一,由有两个或非门或者与非门组成。

- R=0,S=0 时,输出维持原来的状态;

- R=0,S=1 时,输出保持为1,称为置位功能;

- R=1,S=0 时,输出保持为0,称为复位功能;

- R=1,S=1 时,输出Q 和 Q’ 都为0,是一种错位的使出,是不允许出现的状态。(S和R不能同时有效)

锁存器(Latch)是双稳态的,因为根据其输入的不同,输出可以稳定为 1 或 0 。

如果将其看作一个存储单元,那么就是根据输入信号,改变自身的状态,置1、置0和保持不变。这样以来,锁存器的一个问题就是输入信号的任何变化都会反应在输出端口,所以很容易受到毛刺的影响。

触发器

触发器与锁存器的不同在于,除了置1、置0输出端之外,又增加了一个触发信号输入端,只有当触发信号到来的时候,触发器才能按照输入的置1、置0信号置成响应的状态,并保持下去。这个触发信号一般是时钟信号。

触发信号的工作方式可以分为电平触发、边沿触发和脉冲触发三种,对应的就有三种不同类型的触发器。

电平触发的触发器

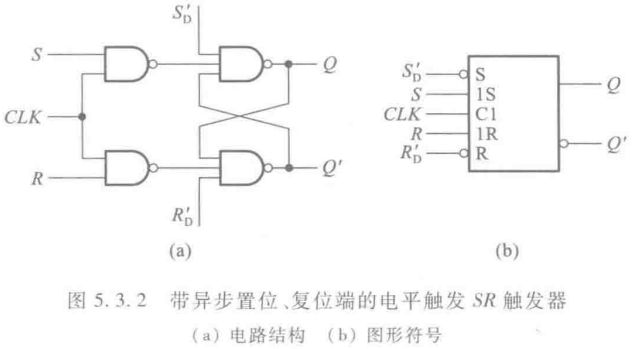

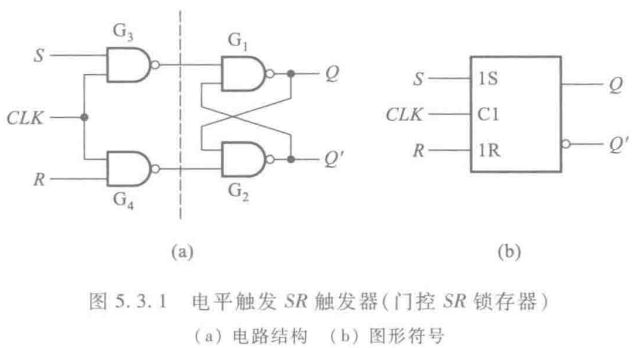

SR触发器

只有 CLK 信号为 1 的时候,才能根据 SR 的输入情况,“触发”电路状态的改变。

当CLK从 1 变为 0 的时候,SR锁存器的输入为 11,此时 Q 的状态保持 CLK 变为 0 之前的状态。

(CLK其实只是一个信号的名称,这个端口的作用其实算是“使能(Enable)”,所以也可以记作“EN”。)

对该电路的拓展是增加异步端口:

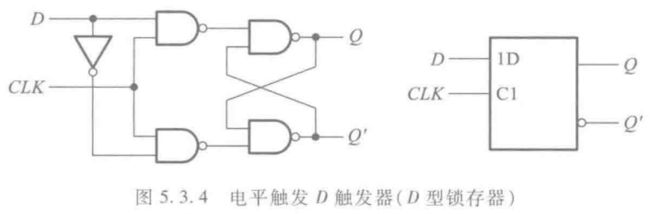

D锁存器(电平触发的D触发器)

在 CLK=1 期间,Q=D。

在clk=1时,数据通过D锁存器流到了Q;在Clk=0时,Q保持原来的值不变(SR的输入为11,输出状态取决于上一个状态),所以这样的锁存器也称为透明锁存器(CLK有效电平期间,输出状态和收入状态保持相同)。

- 适应但输入信号的需要

- 避免了 S 和 R 同时有效的情况的出现

- 可以用于防电路毛刺,具体应用时门控时钟

- 锁定锁存器( lockup latch)可以用于修复扫描链插入时引起的时钟偏移问题

边沿触发的触发器

为了提高触发器的可靠性,增强抗干扰能力,希望触发器的次态仅仅取决于CLK信号下降沿(或上升沿)到达时刻输入信号的状态。而在此之前和之后输入状态的变化对触发器的次态没有影响。为实现这一设想,人们相继研制成了各种边沿触发( edge-triggered)的触发器电路。

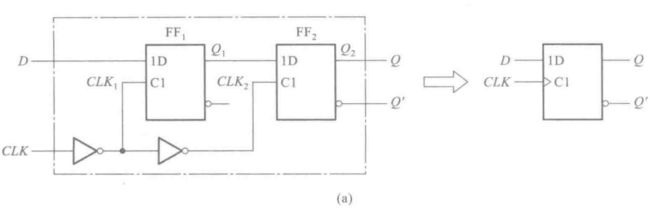

边沿触发 D 触发器

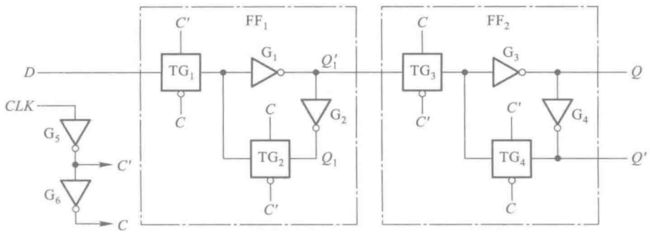

边沿触发的D触发器由两个电平触发的D触发器(又称D型锁存器)构成,其基本电路结构如下:

CLK=0的时候,CLK1=1,FF1处于工作状态,Q1=D;CLK2=0,FF2关闭状态,Q保持为原来的状态;

CLK=1的时候,FF1关闭,Q1不会改变,FF2开启,Q = Q1,输出还是一个稳定的状态。

当CLK从0变为1的时候,CLK1随之变成了低电平(FF1关闭),Q1保持为CLK上升沿到达前瞬间输入端口D的状态,此后不在跟随D的状态变化。与此同时,CLK2跳变为高电平(FF2开启),Q = Q1,也就是说,Q 被置成了CLK上升沿到达前瞬时D端口相同的状态,此后于D端的状态无关(因为Q1不会再随D端口变化了)。

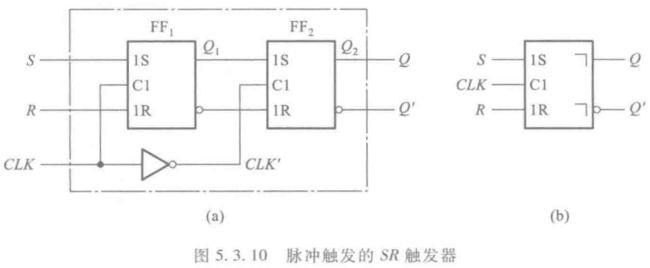

脉冲触发的触发器

在一个时钟周期里,输出端的状态只可能改变一次,而且发生在CLK的下降沿。这一点和边沿触发器类似。

但需要注意的是,现在输入端的主触发器FF,是一个电平触发的SR触发器,而不是电平触发的D触发器了。由于在CLK高电平期间主触发器输出的状态可能随S和R状态的变化而发生多次翻转,输出端的状态不可能始终与输入状态保持一致。因此,在脉冲触发SR触发器中,不能像边沿触发器那样,仅仅根据CLK下降沿到来时刻输入端S和R状态确定输出端Q的状态,而必须考察全部CLK=1期间主触发器状态的变化情况。这一点就是脉冲触发方式和边沿触发方式的区别所在。

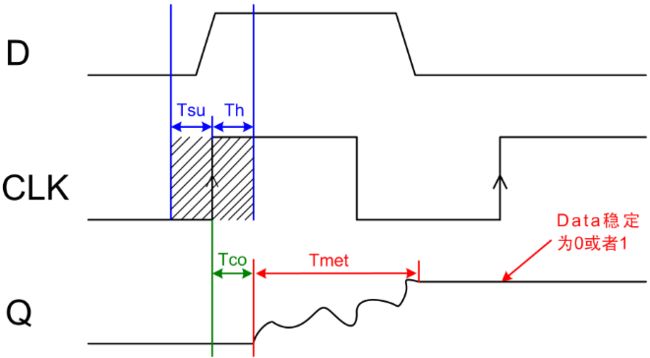

建立时间和保持时间

建立时间(Tsu)是指在时钟有效沿到来之前,数据必须保持稳定的最短时间。

保持时间(Th)是指在时钟有效沿到来之后,数据必须保持稳定的最短时间。

在STA中,这两个概念都是针对寄存器(Reg)提出的。寄存器时什么?寄存器其实就是由一组触发器组成的,每个触发器的输入和输出端口都有引出端,可以直接和周围电路连接,快速的及逆行数据交换。(触发器只能保存一个状态,0 或 1,而寄存器是由多个触发器构成的,每个触发器保存一个状态,触发器就可以保存多个01这种状态,这样就可以以二进制的方式保存数据。)

寄存器是由触发器构成的,那么就可以从触发器的角度考虑建立时间和保持时间。

当时钟上升沿到来的时候,从外部来看,就是将 D 的数据保存到 Q(此后在触发沿到来之前,Q的值保存不变,就好像在这里存了一个数据);

从内部来看,D 触发器是由两个 D 锁存器连接而成的,CLK上升沿到来的时候,其实是将 Q1 的数据保存到 Q。

数字电路的 0 和 1 其实是设置了一个电压阈值(VOL、VOH), 0、1 的传输其实就是充放电的过程,逻辑门和互联线在传输信号的时候(从输入状态的改变到输出状态的改变)是需要时间的(称之为延时)。

这里我们假定CMOS电路图中传输门从控制信号跳变到它的输出状态改变的延迟时间、反相器的传输延时时间都是 td 。

建立时间:

为了保证触发器可靠地翻转,在 C 和 C’ 状态改变之前,FF1中的Q1的状态必须稳定的建立起来,使Q1=D。

加到 D 端的输入信号需要经过传输门TG,和反向器G1和G2的传输延迟时间才能到达Q1端,而在CLK的上升沿到达后,只需经过反相器 G5 的传输延迟时间,C’ 的状态即开始改变,因此D端的输入信号必须先于CLK的上升沿至少2t的时间到达,故 tsu= 2td 。(这也可以看出为什么单元库可以给定时序单元的建立时间使多少。)

从D触发器的内部来看,因为是两级结构,时钟信号对第二级结构发挥作用的时间(td)要比输入端口的数据传输的时间(3td)更短,如果外部的 D 和 CLK 信号同时到达,CLK先起作用,就会把Q1之前的数据保存下来, 所以需要输入数据更早的到达,早的那一部分时间就是建立时间。

在 CLK = 0 的期间,FF1是开启的,FF2是关闭的,所以数据在时钟上升沿早些时候到达,FF1的开启可以保证Q1的值就是想要的值。

在CLK切换为高电平之后,FF2开启,同时关闭FF1,将Q1的数据传到输出端口。但是 FF1 的关闭和FF2的开启是需要时间的;如果在FF1没有完全关闭的时候,D端口的数据变化是会传输到Q1的,那么后续高电平期间(FF2)开启,就会将D端口的这种变化传输过去。

所以信号在时钟上升沿到来之后,必须保持稳定一段时间,保证FF1的完全关闭,这一段时间就是保持时间。

对于电路途中的情况,在 C 和 C’ 改变状态使 TG1 变为截止、TG2变为导通之前,D端的输人信号应当保持不变。为此,至少在CLK上升沿到达后2td(反相器和传输门)的时间内,输入信号应当保持不变,即保持时间应为 th = 2td 。

所以说,建立时间和保持时间都是为了时钟有效沿到达的时候,D端口的值能够稳定的传输到Q1端口,从而保证输出Q端口能够接收到正确的数据。

对于寄存器而言,内部可以由很多的D触发器,从而实现多bit数据的保存,如果其中一个D触发器没有保存到正确的值,就会导致真个寄存器的存储信息出现严重错误。

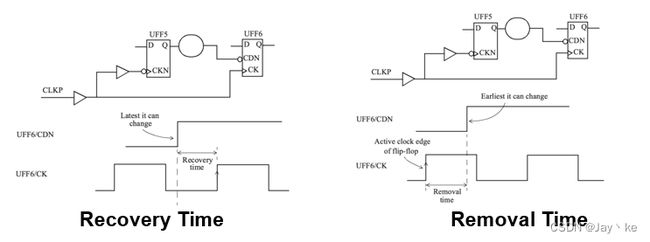

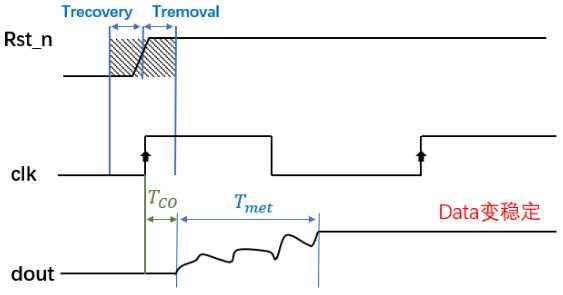

恢复时间和去除时间

此外,对于异步信号,也需要一定的时间来保证数据的稳定传输。

恢复时间(Recovery time):与同步电路中的建立时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)在“下个时钟沿”来临之前变无效的最小时间长度。这个时间的意义是,异步控制信号在时钟上升沿来临Trecovery时间就要保持稳定,如果保证不了这个最小恢复时间,也就是说“下个时钟沿”来临时,这个异步控制信号不能保证正常执行。

recovery time指的是复位信号释放之后要求距离下一个时钟沿的最小时间间隔。这个时间的意义是,如果保证不了这个最小恢复时间,也就是说这个异步复位信号的释放与“下个时钟沿”离得太近(但在这个时钟沿之前),没有给寄存器留有足够时间来恢复至正常状态,那么就不能保证“下个时钟沿”能正常作用,也就是说这个“时钟沿”可能会失效

去除时间(Removal time):与同步电路中的保持时间类似,是指异步控制信号(如寄存器的异步清除和置位控制信号)**在“有效时钟沿”之后变无效的最小时间长度。**这个时间的意义是,异步控制信号在时钟上升沿后仍需保持Tremoval的稳定时间,如果保证不了这个去除时间,也就是说这个异步控制信号的解除与“有效时钟沿”离得太近,那么就不能保证有效地屏蔽这个“时钟沿”,也就是说这个“时钟沿”可能会起作用,这样就不能保证这一异步控制信号能正常执行。

亚稳态

从字面上看,亚稳态就是亚于稳态,既0又不是1的状态。在时钟有效沿到来的前后,触发器的数据端的数据不稳定导致违反触发器的建立时间或者保持时间,引起触发器的输出处于未知的状态,这种未知的状态称为亚稳态。

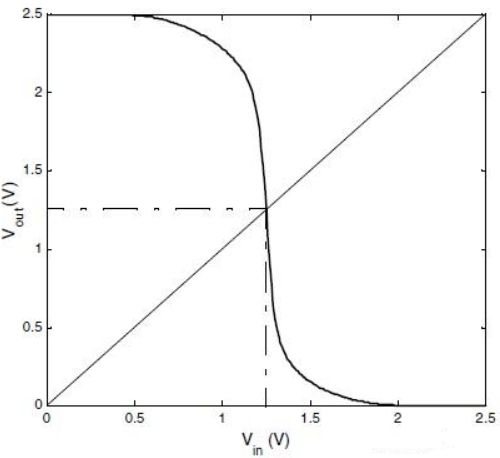

CMOS反相器的电平传输特性曲线如下所示:

Vout=Vin的点叫做反相器的阈值电压。CMOS反相器的特性是,在阈值电压附近输出迅速完成了电平的切换,而在其他区域输出电平几乎不变。

反相器对于输入输出是0还是1的判断其实是一个电压范围。

对于输入,可以假设 0-1V 的输入是低电平,1.5 - 2.5V 是高电平。那么在反相器输入在1-1.5V范围的时候,是没有定义的,也就是在阈值电压附近,反相器可能将它认为是高电平,也可能认为是低电平。

对于输出端口也是如此,假设输出2.25-2.5V是高电平,0-0.25V是低电平。如果输出在0.25-2.25V这个范围内,因为没有定义,输出就有可能使高电平,也有可能使低电平。

数字信号跳变,0->1 或者 1->0,对应的是电压的变化,实际情况下,这个变化需要时间的。如果输入信号刚好在寄存器不能判断的区间(VL~VH),那么,输出就不能判断是0还是1,也就是亚稳态。

也就是说,

当输入数据不满足寄存器的建立时间或者保持时间的时候,寄存器就很可能捕捉到输入数据的电平在未定义的电平区间,输出处于亚稳态。

基本概念

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。即:如果触发器的输入电压采样时间过短,则触发器需要花很长时间来实现输出逻辑达到标准电平,在这段时间里输出端在高低电平之间处于振荡状态,而不是等于理想输出值。也就是说,电路处于中间态的时间变长,使得电路“反应”迟钝,这就是“亚稳态”。

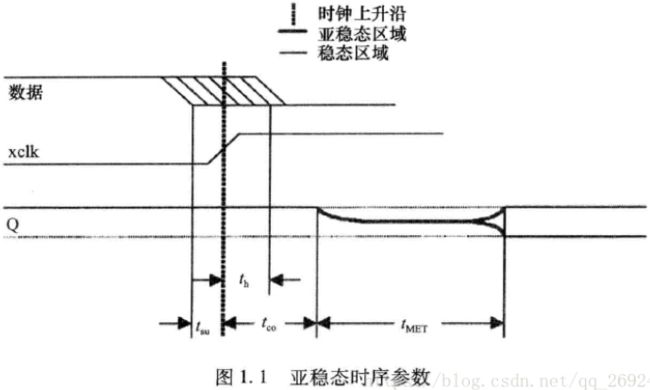

亚稳态是触发器的一个固有特性,正常采样也会有一个亚稳态时间。当建立时间和保持时间满足时,触发器也会经历采样—亚稳态—随后稳定输出。而出现亚稳态问题时,亚稳态(中间态)时间变长。

正常工作时,触发器经历较短的亚稳态时间,随后会正确输出;而出现亚稳态问题时,触发器经历较长的亚稳态时间,最终输出稳定但无法保证正确(是稳定的标准电平信号,但难以保证是输入对应输出)。

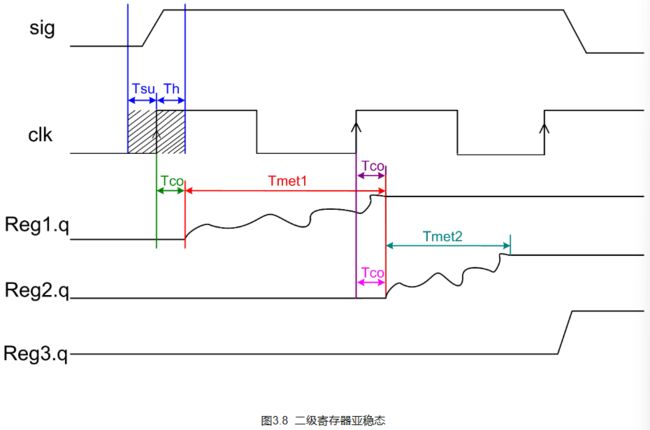

本来经过一定的延时值 tco 之后就会输出正确的稳定的电平值;由于产生了亚稳态,亚稳态持续了tMET时长后,恢复到稳定的电平状态(稳定,但不一定是正确的!),这段持续的时间叫做亚稳态的恢复时间,一般情况下这段时间不会超过一个或者两个时钟周期(取决于触发器的性能)。如果亚稳态持续时间过长(超过一个或者两个时钟周期),就有可能被下一级的触发器捕获,导致下一级触发器也处于亚稳态,这就是亚稳态的传播现象,这是很严重的。

亚稳态的产生

只要系统中有异步元件,亚稳态就是无法避免的,亚稳态主要发生在异步信号检测、跨时钟域信号传输以及复位电路等常用设计中。

在同步系统中,输入信号总是系统时钟同步,能够达到寄存器的时序要求,所以亚稳态不会发生。亚稳态问题通常发生在一些跨时钟域信号传输以及异步信号采集上。

发生的原因如下:

(1)在跨时钟域信号传输时,由于源寄存器时钟和目的寄存器时钟相移未知,所以源寄存器数据发出数据,数据可能在任何时间到达异步时钟域的目的寄存器,所以无法保证满足目的寄存器Tsu和Th的要求;

(2)在异步信号采集中,由于异步信号可以在任意时间点到达目的寄存器,所以也无法保证满足目的寄存器Tsu和Th的要求;

当数据在目的寄存器Tsu-Th时间窗口发生变化,也即当数据的建立时间或者保持时间不满足时,就可能发生亚稳态现象。如下图所示。

(3)在异步复位电路中,复位信号的释放时间不定,难以保证满足恢复时间(Recovery Time)以及去除时间(Removal Time),从而出现亚稳态。

Trecovery是rst_n信号的恢复时间,下一个时钟沿到来之前变成无效的最小时间。如果rst_n拉高和下一个时钟沿到来之间的时间间隔太短,小于Trecovery,那么下个时钟沿可能会失效,采样不到这个信号,类似setup时间。

Tremoval是rst_n信号的去除时间,在采样时钟到来之后,到rst_n无效之间的最小时间,类似hold时间。如果采样时钟上升沿到rst_n撤销之间的间隔时间太短,小于Tremoval时间,就不能有效的屏蔽当前这个采样时钟沿,有可能会采样到rst_n撤销掉。

换句话来说,如果你想让某个时钟沿起作用,那么你就应该在“恢复时间”之前是异步控制信号变无效,如果你想让某个时钟沿不起作用,那么你就应该在“去除时间”过后使控制信号变无效。如果你的控制信号在这两种情况之间,那么就没法确定时钟沿是否起作用或不起作用了,也就是说可能会造成寄存器处于不确定的状态。而这些情况是应该避免的。

减少亚稳态的方法

亚稳态是期间的固有属性,是不可避免的,但是我们可以减少亚稳态的产生和传播。

降低时钟频率

亚稳态产生概率 = (建立时间 + 保持时间)/ 采集时钟周期

(在一个时钟周期内,信号的变化发生在建立时间和保持时间这个范围内的时候,就会出现亚稳态。)

可以看出,亚稳态出现的概率与工作时钟频率以及触发器自身的特性(器件的工艺等因素决定了它的建立/保持时间)有关;所以在异步信号采集过程中,要想减少亚稳态发生的概率可以:

① 降低系统工作时钟,增大系统周期,亚稳态概率就会减小(降低工作频率,不常用);

② 采用更好的工艺,用反应更快的触发器,减小器件的建立时间和保持时间。

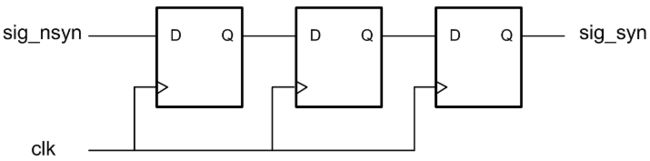

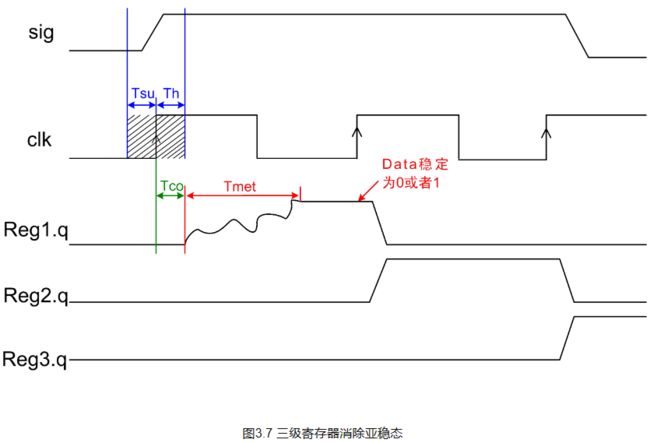

多级触发器

使用异步信号进行使用的时候,好的设计都会对异步信号进行同步处理,同步一般采用多级D触发器级联处理。

第一级寄存器产生亚稳态后,如果直接输出很可能将亚稳态传递下去导致系统崩溃;而添加了第二级D触发器后,相当于多给了寄存器一个时钟周期的时间恢复稳定,因此出现亚稳态的几率就会大大减小。由分析可见,触发器级数越多,出现亚稳态的几率就会越小,但是一般来说两级寄存器已经足够,而不需要再添加额外的级数导致资源浪费。(第二级寄存器稳定输出概率为90%,第三极寄存器稳定输出的概率为99%)

当第一个寄存器发生亚稳态后,经过Tmet的振荡稳定后,第二级寄存器能采集到一个稳定的值。但是为什么第二级寄存器还是可能会产生亚稳态呢?

由于振荡时间Tmet是受到很多因素影响的,所以Tmet时间又长有短,所以当Tmet时间长到大于一个采集周期后,那第二级寄存器就会采集到亚稳态

由上图可知,第二级也是一个亚稳态,所以在这种情况下,亚稳态产生了串扰,从第一级寄存器传到了第二级寄存器,同样也可能从第二级寄存器串扰到第三级寄存器。这样会让设计逻辑判断出错,产生亚稳态传输,可能导致系统死机奔溃。

所以说,多级触发器级联一定程度可以消除亚稳态,但是不能保证数据的正确性?(只要亚稳态产生了,数据就有可能出错,如果不想出错,就是要避免亚稳态的产生。对于多级触发器而言,他只是消除产生的亚稳态,避免因为亚稳态的传播造成更大的影响。)

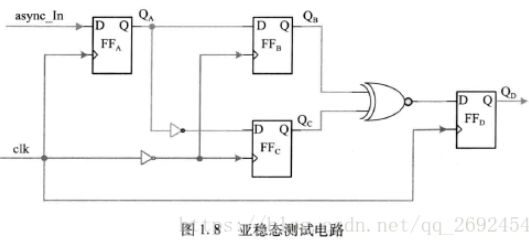

亚稳态检测电路

亚稳态可能无法完全消除,因此在系统中引入可靠性和冗余机制是一种有效解决方案。例如,在敏感路径上增加亚稳态检测电路,一旦检测到亚稳态发生,可以采取纠正措施,如重新采样或通过冗余计算来消除亚稳态结果。

一个有异步信号async_In输入的触发器FFA ,在时钟clk上升沿触发。触发器FFB 和FFC 在时钟的下降沿触发,为了捕获FFA 的亚稳态。

正常传递到触发器FFB 和FFC 的信号是两个互补的信号,经过异或非门之后,输出一定是低电平。但是FFA产生亚稳态的时候,异或非门的输出就会变成高电平,在触发器FFD 输出端捕获到高电平就表示已经检测到亚稳态事件。

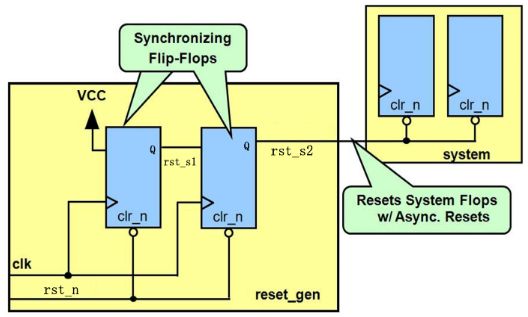

异步复位同步释放

外部给过来的异步复位信号,我们一般不会直接用在内部寄存器上,而是会先经过处理之后再在内部使用,这个过程就是异步复位同步撤离。

所谓异步复位同步释放,就是在rst_n信号为低时,立刻进行复位,即复位信号与时钟相互独立;而rst_n信号由低到高释放时,为了防止亚稳态的出现,将rst_n信号用DFF向后延一周期,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步。

基本电路图如下:

第一级FF的输入固定为“1”,第二级的FF用来消除解复位时可能带来的的亚稳态:

在resetn释放前,2个DFF的Q端都是0。

在resetn释放时,两个DFF的recovery/removal可能都出现不满足的情况,于是第1个DFF的Q会产生x值。

但对于第2个DFF来说,由于它的D/Q都是0,即使resetn会导致recovery/removal不满足,它的Q也依然是0,它的D端并不能马上就能看到第1个DFF的Q端产生的x值,而是会在下一个clk沿处才能看到这个x值。

很大概率在下一个clk沿处Q1会恢复稳定,一般不会出现亚稳态,若稳定后的值为1,则下一拍同步释放;若稳定后的值为0,则同步释放会延迟一拍,不会影响到后续电路。

Verilog代码:

module asyrst(

input clk,

intput asyrst_n,

output sysrst_n

);

reg rst1;

reg rst2;

always@(posedge clk or negedge asyrst_n) begin

if(!asyrst_n) begin

rst1 <= 1'b0;

rst2 <= 1'b0;

end

else begin

rst1 <= 1'b1;

rst2 <= rst1;

end

end

assgin sysrst_n = rst2;

endmodule

异步复位:显而易见,asyrst_n异步复位后,syrst_n将拉低,即实现异步复位。

同步释放:这个是关键,看如何实现同步释放,即当复位信号asyrst_n撤除时,由于双缓冲电路(双寄存器)的作用,asyrst_n复位信号不会随着asyrst_n的撤除而撤除。

假设第一级D触发器clk上升沿时asyrst_n正好撤除,则D触发器第一级有可能发生亚稳态,此时第二级触发器也会将输出更新为第一级触发器前一个周期的输出值,即低电平,所以亚稳态被阻隔或者是被缓冲。直到下一个clk来之后,第二级触发器才会更新最终的复位输出信号asyrst_n,但这个时候亚稳态多半已经恢复稳定了,即便恢复错了成了低电平其实也没关系,最多再等一个周期高电平就来了啊,关键是这个时候亚稳态已经没了,这就是同步释放。

单bit异步信号慢时钟域到快时钟域

脉冲信号快时钟域到慢时钟域

多bit异步信号同步器

当多位宽数据进行同步时,如果数据变化速率过快,用异步时钟进行打拍采样,可能会采集到因路径延迟不同而导致的错误数据。解决此类异步问题的常用方法包括:

- 格雷码编码

通过格雷码编码将多位信号转化为每次只有一位变化的信号,将“多比特”的跨时钟域变换成“单比特”进行处理。

- 握手处理

通过通信双方使用专用控制信号进行数据收发的状态指示的方法,使控制信号双向联系(可以发送域传给接收域的,也可以接收域给发送域),有别于单向控制信号检测方式。

- MUX同步器

带数据有效标志信号的多比特数据做跨时钟域。

- 异步FIFO

什么情况下都可以使用,尤其在有大量的数据需要进行跨时钟域传输, 并且对数据传输速度要求比较高的场合。和格雷码+异步双口RAM方法是一样的

参考资料

- 三态门——概念,作用,原理

- 什么叫单稳态,双稳态

- 亚稳态专题

- 异步复位同步释放

- 亚稳态后续可看看:芯动力——硬件加速设计方法

- 亚稳态