【CDC设计】跨时钟域处理(四)其他细节问题

目录

命名约定和设计划分

时钟和信号命名约定

没有命名约定的多时钟/多源模块

每个时钟域的时序验证

面向时钟的设计划分

时钟分区模块的时序分析

使用 MCP 方法进行分区

多时钟门级仿真问题

同步器门级 CDC 仿真问题

从门级仿真中去除 X 传播的策略

关闭时序检查的模拟器命令

将触发器建立和保持时间更改为 0

复制和修改新的触发器模型

使用多个 SDF 文件

总结与结论

单 bit CDC 技术

多 bit CDC 技术

推荐的命名约定和设计划分

多时钟门级 CDC 仿真的推荐解决方案

命名约定和设计划分

命名约定有助于确保良好的团队沟通,也有助于使用脚本语言来收集和分组设计中与特定时钟相关的所有信号。良好的设计分区可以显着减少综合和验证多时钟设计时序的工作量。本节将讨论推荐的命名约定和设计分区。

有两种方法可以解决潜在的 CDC 问题:

(1) 验证设计是否符合合格的 CDC 规则;

(2) 避免问题。

这两种方法都很有价值,应该用于确保无错误的设计。

第一种方法是验证 CDC 设计规则,通常需要使用特殊工具来检查设计是否存在可能的 CDC 违规行为。

第二种方法,避免问题,可以通过采用一些好的编码指南来完成,如下所述。

时钟和信号命名约定

团队中各种设计都使用了许多有用的时钟和信号命名约定。

指南:使用时钟命名约定来识别设计中每个信号的时钟源。

原因:命名约定有助于所有团队成员识别设计中每个信号的时钟域,并且还可以使用综合脚本中的正则表达式“通配符”更轻松地对信号进行分组以进行时序分析。

一种经过验证的命名约定要求使用前导前缀字符来标识各种异步时钟域。示例包括:uClk用于微处理器时钟, vClk用于视频时钟, dClk用于显示时钟。

然后将每个信号同步到设计中的一个时钟域,每个信号名称都标有前缀字符,以标识用于生成该信号的时钟域。例如,由uClk生成的任何信号在信号名称中都用 u‑prefix 标记,例如uaddr、 udata、 uwrite等。由vClk生成的任何信号在信号名称,例如vdata、 vhsync、 vframe等。相同的信号命名约定用于设计中任何其他时钟生成的所有信号。

使用这种技术,设计团队中的任何工程师都可以轻松识别设计中任何信号的时钟域源,并直接使用信号或通过适当的同步传递信号,以便可以在新的时钟域中使用信号。确切的命名约定并不重要,但至关重要的是项目中的每个工程师都同意遵守团队选择的命名约定。命名约定将显着提高设计团队的生产力。

没有命名约定的多时钟/多源模块

如果团队不使用任何特定的面向时钟的信号命名约定,并且如果允许模块具有多个时钟输入,则始终存在 CDC 分析工具可能无法正确设置的危险,并且很容易错过糟糕的 CDC 设计实践。

即使可以使用良好的 CDC 分析工具,建议采取一些简单的步骤来使对潜在 CDC 设计问题的分析和识别更容易识别和调试。

每个时钟域的时序验证

要验证任何设计的时序,必须验证设计中每个时钟域的时序是否满足。尽管工具在过去十年中有所改进,有助于自动分析和验证不同时钟域中的信号,但使用良好的分区和命名约定来处理多时钟设计仍然是一种很好的做法。

通过将设计划分为每个模块只允许一个时钟,静态时序分析对于设计中的每个域来说变得非常容易。

面向时钟的设计划分

一些最简单和最好的设计分区方法是使用时钟边界处的设计分区来实现的。

指南:每个模块只允许一个时钟

原因:在单时钟模块或单时钟模块组上更容易完成静态时序分析和创建综合脚本。

例外:将来自所有不同时钟域的信号连接在一起的顶层模块自然会将所有时钟作为该模块的输入。尽量减少多时钟验证工作,只允许顶层模块有多个时钟输入。

指南:将设计块划分为单时钟模块。

原因:完全同步子块的时序验证可以很容易地使用 STA(静态时序分析)工具进行验证,并将设计块划分为多个单时钟域子块将大型复杂的时序分析任务转变为多个完全同步的单时钟设计。

指南:创建同步器模块以将信号从一个时钟域传递到另一个时钟域,并且每个同步器模块只允许一个时钟。

原因:假设任何从一个时钟域传递到另一个时钟域的信号最终都会遇到建立和保持时间问题。隔离 CDC 边界逻辑可以显著减少多时钟设计的设计和验证工作。

在大多数情况下,同步器模块将是设计中唯一会遇到建立时间和保持时间违例的模块。在异步时钟域之间传递信号时,会发生时序违例,这就是为什么必须在设计中添加同步器的全部原因。

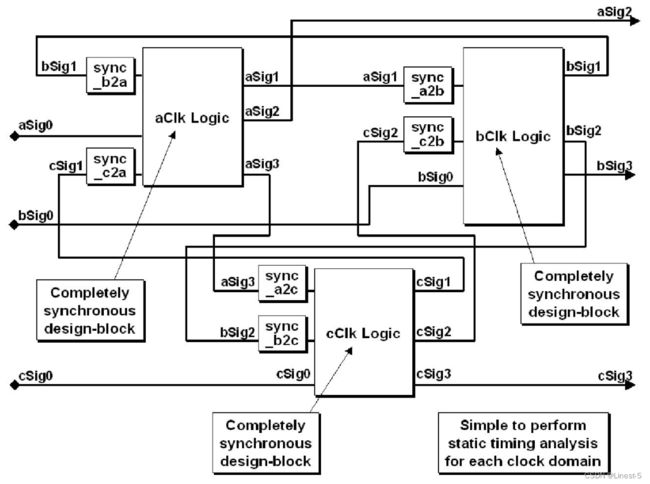

考虑一个具有三个时钟域的示例设计,分别标记为 aClk、 bClk 和 cClk ,如上图所示。在该设计中,所有 aClk 设计块都被分组到一个单一的 aClk 逻辑块中。所有的 bClk 设计块都被分组到一个 bClk 逻辑块中,同样我们创建了一个 cClk 逻辑块。任何源自异步的信号时钟域在被允许驱动另一个逻辑块的输入之前通过一个同步器模块。

时钟分区模块的时序分析

使用面向时钟的设计分区策略,每个设计块的所有输入和输出都与一个时钟完全同步。这是使用静态时序分析 (STA) 工具验证的最简单的设计类型,因为设计中没有错误路径。

将在每个时钟域中计时的所有设计模块组合在一起。应为设计中的每个时钟域形成一组。这些组将进行时序验证,就好像每个都是单独的、完全同步的设计一样。对于每个时钟域,我们都有一个设计块,我们可以轻松执行最坏情况(最大时间/设置时间检查)时序分析和最佳情况(最小时间/保持时间检查)时序分析。

同样使用这种面向时钟的分区策略,每个 CDC 边界都已使用同步器模块隔离。每个同步器模块仅包括由 ASIC 或 FPGA 供应商提供的同步器单元(首选),或者使用成对连接的触发器构建,以形成同步器等效单元。

如果 ASIC 或 FPGA 供应商提供同步器单元,并在设计中实例化,则无需验证这些模块的建立和保持时间,因为供应商应该已经创建了不违反建立或保持的单元布局触发器阶段之间的时间。

如果同步器是从 RTL 代码合成的,最重要的是执行最佳情况时序分析,以确保触发器不会靠得太近,以免第一级的输出变化太快满足第二级输入的保持时间要求。还应查看最坏情况时序分析,以防万一布局工具碰巧将两个同步器触发器放置在 ASIC 或 FPGA 芯片上相距很远的地方。

由于单独同步器的分区,门级仿真可以更容易地配置为忽略每个同步器第一阶段的建立和保持时间违例。RTL 同步器的静态时序分析需要简单的 set_false_path 命令来移除 STA 的输入。我们知道同步器的输入存在时序问题,这就是使用同步器的原因。

通过划分设计和同步器块以允许每个模块只允许一个时钟,静态时序分析成为一项非常容易执行的任务。用于解决多个时钟域问题的综合脚本命令现在变成了分组、识别错误路径和执行最小‑最大时序分析的问题。

使用 MCP 方法进行分区

大多数情况下,将时钟边界处的设计划分为单独的设计块和同步器块效果很好,但如果需要使用 MCP 公式在时钟域之间传递多个信号,那么传递到设计块的一些信号可能会出现来自不同的时钟域,如下图所示。

如果设计中的信号使用了基于时钟的命名约定,那么具有异步输入的设计块仍然可以轻松地进行定时。在对相关设计块执行 STA 之前,只需从分析中排除异步输入即可。

通常,只有同步器和 MCP 公式数据路径的输入需要“set_false_path”命令。如果使用时钟前缀命名方案,则可以使用通配符轻松识别所有异步输入。在上图中,要从 bClk逻辑块内的 STA 中排除数据总线,首先执行命令:

该命令用于去除来自bClk STA 的所有异步输入。

多时钟门级仿真问题

当同步器识别出 CDC 信号上的建立和保持时间违规时,数字仿真模型通常会生成 X。这经常会导致门级仿真失败。有哪些技术可以解决这个问题?

如前面所述,通过同步器跨越时钟边界的信号将遇到建立和保持违规。这就是为什么要在设计中添加同步器,以滤除太接近接收时钟域时钟信号的上升沿而变化的信号的亚稳态效应。

同步器门级 CDC 仿真问题

在多时钟设计上进行门级仿真时,触发器的 ASIC 库模型使用建立和保持时间表达式建模,以匹配实际触发器的时序规范。 ASIC 库通常对触发器进行建模,以在发生时序违规时在触发器输出上驱动 X(未知数)。在模拟门级同步器时,建立和保持时间违规可能会导致 ASIC 库发出建立和保持时间错误消息,并且违规信号经常被驱动到 X 值。这些 X 值传播到设计的其余部分,在尝试验证整个门级设计的功能时会出现问题,如下图所示。

从门级仿真中去除 X 传播的策略

由于 X 传播发生在违反建立或保持时间时,几乎所有解决此问题的方法都涉及将建立和保持时间更改为 0,这样就不会违反建立或保持时间,因此,没有 X‑传播。

有些方法不好,有些方法很好。以下是已考虑解决 X 传播问题的一些策略。

关闭时序检查的模拟器命令

大多数 SystemVerilog 仿真器都有一个命令选项来忽略所有时序检查,但这也会忽略设计其余部分所需的时序检查。

将触发器建立和保持时间更改为 0

可以将同步器中使用的任何 ASIC 库触发器的设置和保持时间设置更改为零,但这会导致对同一类型触发器的所有实

例的所有设置和保持时间检查设置为零,包括您可能想用来测试设计其余部分的触发器。

复制和修改新的触发器模型

可以从 ASIC 库复制触发器并将它们存储到具有不同名称的新 SystemVerilog 库中,将所有设置和保持时间设置为零,然后修改设计门级网表,替换所有第一级同步器 ASIC 库触发器‑ 带有修改过的库触发器的触发器没有时序检查,但这可能是一个容易出错且乏味的过程,每次生成新的网表时都可能需要重复该过程,或者可能需要创建生成文件和脚本来自动生成每次生成新的网表时进行修改。

使用多个 SDF 文件

请记住,消除不需要的 X 传播的关键是将同步器输入的建立和保持时间强制为 0,从而消除同步器输入上所有可能的建立和保持时间违规。

生成两个 SDF 文件。第一个 SDF 文件包含整个设计的所有实际延迟,包括准确的建立和保持时间。然生成第二个 SDF 文件,其中仅包含第一级触发器。在此文件中,设置和保持时间设置为 0。

然后使用 $sdf_annotate 命令读入第一个 SDF 文件。然后读入第二个 SDF 文件,该文件覆盖了第一阶段同步器数据输入的设置和保持时间。读取两个 SDF 文件时,每个实例的最后一个 SDF 文件获胜。所有计时都被准确注释,然后对第一级同步器的计时检查进行了修改。

这是一种巧妙的技术,可用于任何生成 SDF 文件的工具流。

总结与结论

时钟域交叉 (CDC) 错误会导致严重的设计失败。通过遵循一些关键指南并使用成熟的验证技术,可以避免这些代价高昂的故障。

单 bit CDC 技术

在时钟域之间传递 1 bit 时:

(1)在发送时钟域中寄存信号以消除组合稳定。

(2)将信号同步到接收时钟域。可能需要多循环路径 (MCP)

多 bit CDC 技术

在时钟域之间传递多个控制或数据信号时,请使用以下方法之一:

(1)在将信号同步到接收域之前合并,首先尝试在发送时钟域中将多个信号组合成一个 1 bit 表示。

(2)使用多周期路径(MCP) 公式跨时钟域传递多个信号(握手法)

(3)使用FIFO 传递多位总线,数据总线或控制总线。

(4)使用格雷码计数器。

推荐的命名约定和设计划分

使用基于时钟的命名约定。

尽可能将设计子块划分为完全同步的一个时钟设计。

多时钟门级 CDC 仿真的推荐解决方案

在门级仿真期间,有多种有用的解决方案可以解决 CDC X 传播仿真问题:

(1)使用 Synopsys 开关为同步器上的第一级触发器生成 0 建立时间和 0 保持时间。仅适用于 Synopsys 工具。

(2)使用多个 SDF 文件 。

(3)供应商提供同步器单元和适当的 SDF 工具。

(4)使用 SystemVerilog 模型来模拟同步问题。