4选1多路选择器的Verilog描述及仿真

多路选择器的功能:在选择信号的控制下,从多个输入中选择一个输出。

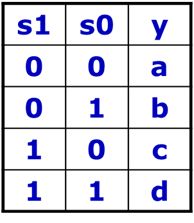

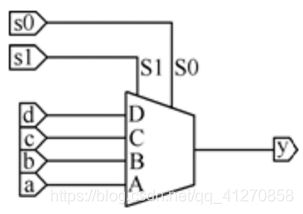

真值表 符号

Verilog描述

①采用case语句描述

module data_selector41(sel,in,out);

input [1:0] sel;

input [3:0] in;

output out;

reg out;

//若括号里均为0,则out必为0,完全可以不执行always语句

always @(sel or in)

begin

case({sel[1],sel[0]})

2'b00: out <= in[0];

2'b01: out <= in[1];

2'b10: out <= in[2];

2'b11: out <= in[3];

default: out <= 1'bx;

endcase

end

endmodule②采用assign语句描述

module data_selector41(a,b,c,d,s1,s0,y);

input a,b,c,d,s1,s0;

output y;

wire [1:0] SEL;

wire A,B,C,D;

assign SEL = {s1,s0};

assign A = (SEL == 2'b00);

assign B = (SEL == 2'b01);

assign C = (SEL == 2'b10);

assign D = (SEL == 2'b11);

assign y = (a & A)|(b & B)|(c & C)|(d & D);

endmodule③采用条件语句描述

module data_selector41(a,b,c,d,s1,s0,y);

input a,b,c,d,s1,s0;

output y;

reg [1:0] SEL;

reg y;

always @(a,b,c,d,s1,s0)

begin

SEL = {s1,s0};

if(SEL == 2'b00) y = a;

else if(SEL == 2'b01) y = b;

else if(SEL == 2'b10) y = c;

else y = d;

end

endmodule测试程序

module test_data_selector41;

reg [3:0] IN;

reg [1:0] S;

wire Y;

data_selector41 D41(.sel(S),

.in(IN),

.out(Y));

always #10 IN[0] =~ IN[0];

always #20 IN[1] =~ IN[1];

always #40 IN[2] =~ IN[2];

always #80 IN[3] =~ IN[3];

initial

begin

S = 1'b0; IN = 4'h0;

#160 $stop;

end

always #10 S = S+1;

endmodule

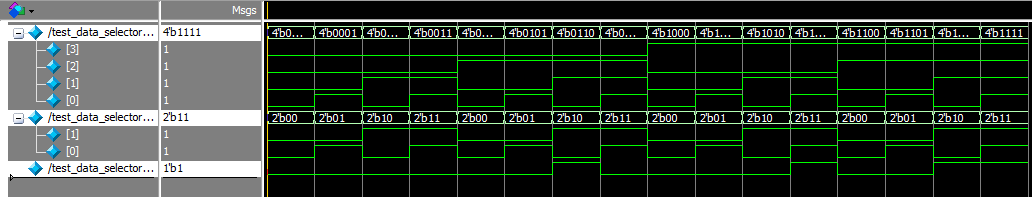

仿真结果