2、基于STM32CubeMX的FreeRTOS移植——第二章【FreeRTOS系统移植】

文章目录

- 一、STM32cubeMX详解

-

- 1.STM32CubeMX功能介绍

- 2.STM32CubeMX安装

- 二、配置FreeRTOS

-

- 1.使用STM32CubeMX配置FreeRTOS

- 2.工程代码分析

- 3.在任务中添加功能

一、STM32cubeMX详解

1.STM32CubeMX功能介绍

STM32CubeMX是一款功能强大的软件,为STM32微控制器应用程序开发提供了一种快捷方便的方法。它旨在提高开发效率,节省时间和费用,并用于优化STM32微控制器的性能和可靠性。STM32CubeMX的功能主要包括图形化配置HAL,性能分析,代码生成,仿真,调试和模拟功能。

1、图形化配置HAL: STM32CubeMX的图形化配置HAL功能支持使用图形化界面来配置STM32 HAL库,支持选择片上外设(如中断,DMA,ADC,TIM,GPIO等),使用图形化界面配置时序参数,从而可以支持STM32硬件定时器,硬件时钟,DMA等功能和参数。

2、性能分析: STM32CubeMX可以对STM32应用程序和性能进行分析,并可以识别内存使用情况,执行速度和电源使用情况。此外,STM32CubeMX还为客户提供了应用程序的基本性能参数,以识别系统性能的低点,提高系统性能。

3、代码生成: STM32CubeMX不仅可以使用图形化工具配置芯片,还可以生成相应的源代码用于程序开发。此外,STM32CubeMX还提供了配置文件和模板,可以帮助用户快速开发STM32应用程序。

4、仿真: STM32CubeMX支持仿真功能,可以模拟STM32应用程序的运行状况,进行检查和调试,并发现在程序中可能出现的错误,从而可以更好地控制应用程序的质量。

5、调试和模拟: STM32CubeMX支持基于串口的仿真和调试功能,可以实现双向调试,查看应用程序的运行状况,进行故障排查和程序调试。此外,STM32CubeMX还支持一些常用的硬件模拟器,可以通过模拟器来进行测试和调试。

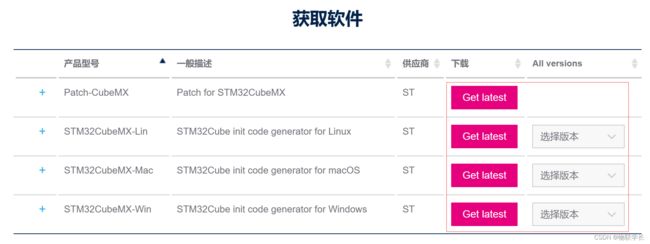

2.STM32CubeMX安装

二、配置FreeRTOS

1.使用STM32CubeMX配置FreeRTOS

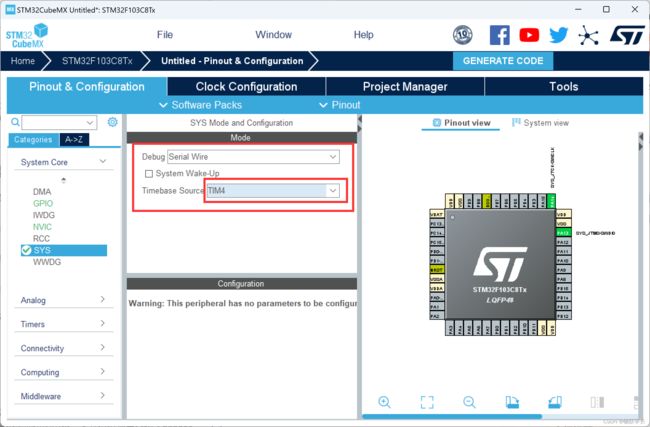

- 选择对应的芯片(本文选用STM32F103C8T6最小系统来进行教学)

- 系统时钟源选择除系统时钟的任意一个,本文选择TIM4作为时钟源,因为FreeRTOS会占用系统时钟。

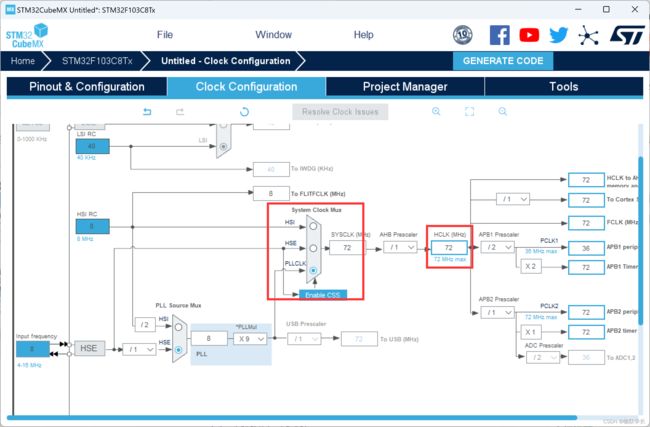

- 晶振选择外部高速晶振

- 时钟树配置

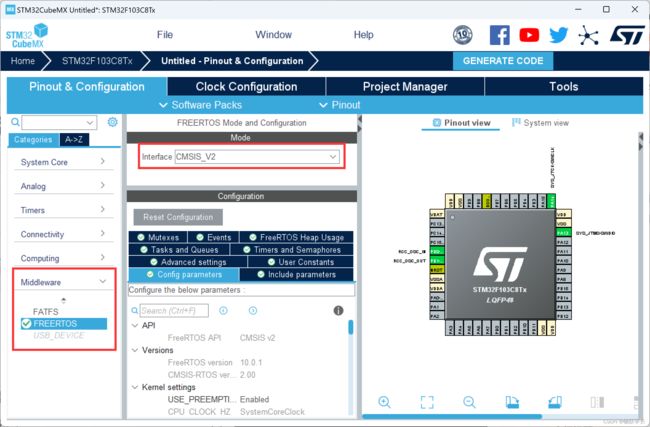

- FreeRTOS系统移植

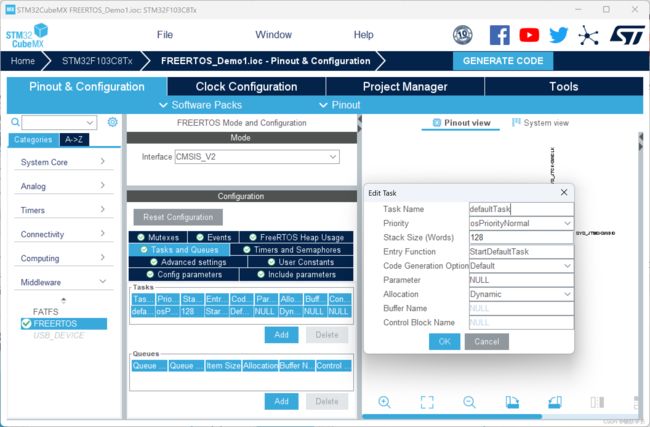

在Middleware下面选择FREERTOS,然后在Interface选择最新的版本CMISIS_V2。

在Task and Queues中双击默认的任务,系统自动生成了一个名为defaultTask的任务,优先级为osPriorityNormal,占空间大小128words,任务的函数名为StartDefaultTask。 - 生成工程代码

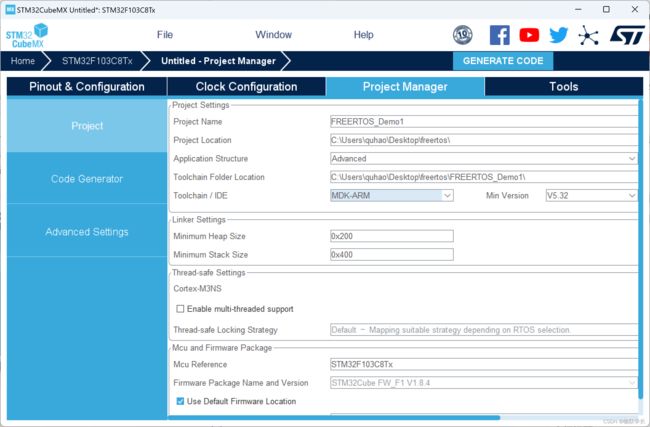

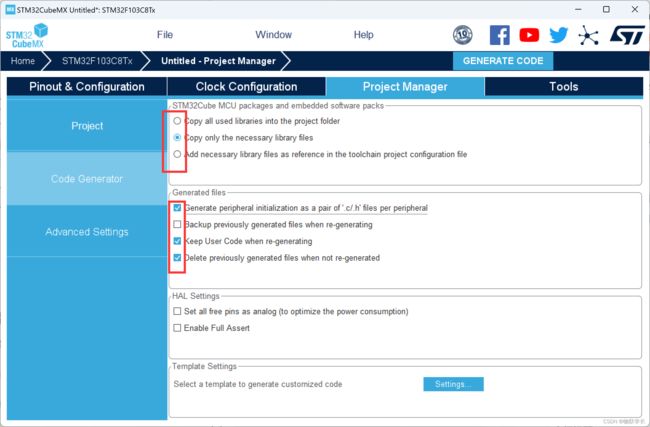

设置工程名称和保存路径后设置工程代码规范。

完成设置后点击GENERATE CODE生成工程文件。 - 打开工程编译项目

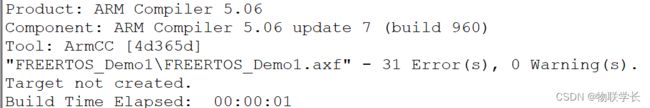

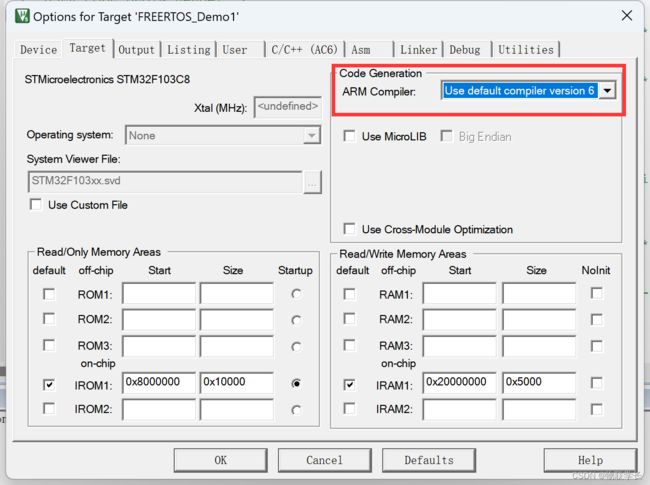

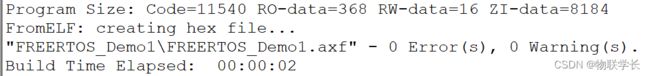

如果编译没问题,说明移植成功。如出现如下报错

这是因为安装的最新版的keil软件不包含5.x的编译器,选择魔术棒工具将编译器版本设置为6.x版本。 在FreeRTOS官网下载FreeRTOS的源代码。,将官方代码的FreeRTOSv10.4.1\FreeRTOSv10.4.1\FreeRTOS\Source\portable\RVDS\ARM_CM3文件夹下的文件(port.c和portmacro.h)复制到STM32CubeMX的Middlewares\Third_Party\FreeRTOS\Source\portable\RVDS\ARM_CM3路径下,再次编译就没有报错了。

在FreeRTOS官网下载FreeRTOS的源代码。,将官方代码的FreeRTOSv10.4.1\FreeRTOSv10.4.1\FreeRTOS\Source\portable\RVDS\ARM_CM3文件夹下的文件(port.c和portmacro.h)复制到STM32CubeMX的Middlewares\Third_Party\FreeRTOS\Source\portable\RVDS\ARM_CM3路径下,再次编译就没有报错了。 如果觉得麻烦,可以选择使用STM32CubeIDE。

如果觉得麻烦,可以选择使用STM32CubeIDE。

如果不想下载源代码,可以将文末的代码复制替换掉CubeMX生成的port.c和portmacro.h。

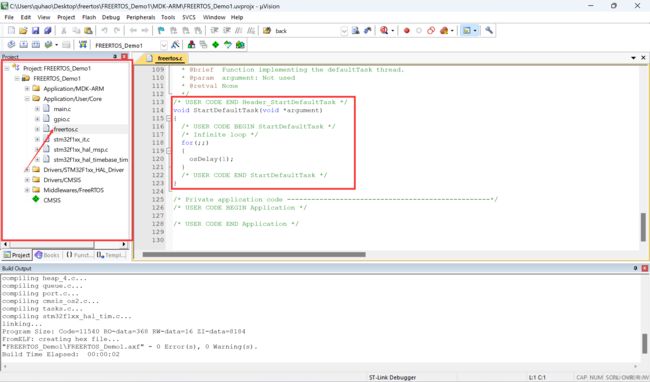

2.工程代码分析

刚刚使用CubeMX生成的工程中,找到freertos.c文件。下滑找到StartDefaultTask这个函数,就是defaultTask的任务函数。 代码的51到56行定义就是在任务配置界面配置的参数。

代码的51到56行定义就是在任务配置界面配置的参数。

osThreadId_t defaultTaskHandle; //任务defaultTask的任务句柄

const osThreadAttr_t defaultTask_attributes = {

.name = "defaultTask", //任务的注释名称

.stack_size = 128 * 4, //任务的栈空间大小

.priority = (osPriority_t) osPriorityNormal, //任务优先级

};

3.在任务中添加功能

STM32F103C8T6最小系统版的PC13引脚有一个LED灯,在STM32CubeMX中将该引脚设置为output模式,然后再任务函数中添加如下代码

void StartDefaultTask(void *argument)

{

/* USER CODE BEGIN StartDefaultTask */

/* Infinite loop */

for(;;)

{

HAL_GPIO_TogglePin(GPIOC,GPIO_PIN_13);//翻转GPIO PC13

osDelay(500); //延时500个时钟节拍

} /* USER CODE END StartDefaultTask */

}

编译后将程序下载进STM32F103C8T6中,LED每隔500ms反转一次。

将如下代码替换port.c文件

/*

* FreeRTOS Kernel V10.4.1

* Copyright (C) 2020 Amazon.com, Inc. or its affiliates. All Rights Reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy of

* this software and associated documentation files (the "Software"), to deal in

* the Software without restriction, including without limitation the rights to

* use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of

* the Software, and to permit persons to whom the Software is furnished to do so,

* subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS

* FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR

* COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER

* IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN

* CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

*

* https://www.FreeRTOS.org

* https://github.com/FreeRTOS

*

*/

/*-----------------------------------------------------------

* Implementation of functions defined in portable.h for the ARM CM3 port.

*----------------------------------------------------------*/

/* Scheduler includes. */

#include "FreeRTOS.h"

#include "task.h"

/* For backward compatibility, ensure configKERNEL_INTERRUPT_PRIORITY is

* defined. The value should also ensure backward compatibility.

* FreeRTOS.org versions prior to V4.4.0 did not include this definition. */

#ifndef configKERNEL_INTERRUPT_PRIORITY

#define configKERNEL_INTERRUPT_PRIORITY 255

#endif

#ifndef configSYSTICK_CLOCK_HZ

#define configSYSTICK_CLOCK_HZ configCPU_CLOCK_HZ

/* Ensure the SysTick is clocked at the same frequency as the core. */

#define portNVIC_SYSTICK_CLK_BIT ( 1UL << 2UL )

#else

/* The way the SysTick is clocked is not modified in case it is not the same

* as the core. */

#define portNVIC_SYSTICK_CLK_BIT ( 0 )

#endif

/* Constants required to manipulate the core. Registers first... */

#define portNVIC_SYSTICK_CTRL_REG ( *( ( volatile uint32_t * ) 0xe000e010 ) )

#define portNVIC_SYSTICK_LOAD_REG ( *( ( volatile uint32_t * ) 0xe000e014 ) )

#define portNVIC_SYSTICK_CURRENT_VALUE_REG ( *( ( volatile uint32_t * ) 0xe000e018 ) )

#define portNVIC_SHPR3_REG ( *( ( volatile uint32_t * ) 0xe000ed20 ) )

/* ...then bits in the registers. */

#define portNVIC_SYSTICK_INT_BIT ( 1UL << 1UL )

#define portNVIC_SYSTICK_ENABLE_BIT ( 1UL << 0UL )

#define portNVIC_SYSTICK_COUNT_FLAG_BIT ( 1UL << 16UL )

#define portNVIC_PENDSVCLEAR_BIT ( 1UL << 27UL )

#define portNVIC_PEND_SYSTICK_CLEAR_BIT ( 1UL << 25UL )

#define portNVIC_PENDSV_PRI ( ( ( uint32_t ) configKERNEL_INTERRUPT_PRIORITY ) << 16UL )

#define portNVIC_SYSTICK_PRI ( ( ( uint32_t ) configKERNEL_INTERRUPT_PRIORITY ) << 24UL )

/* Constants required to check the validity of an interrupt priority. */

#define portFIRST_USER_INTERRUPT_NUMBER ( 16 )

#define portNVIC_IP_REGISTERS_OFFSET_16 ( 0xE000E3F0 )

#define portAIRCR_REG ( *( ( volatile uint32_t * ) 0xE000ED0C ) )

#define portMAX_8_BIT_VALUE ( ( uint8_t ) 0xff )

#define portTOP_BIT_OF_BYTE ( ( uint8_t ) 0x80 )

#define portMAX_PRIGROUP_BITS ( ( uint8_t ) 7 )

#define portPRIORITY_GROUP_MASK ( 0x07UL << 8UL )

#define portPRIGROUP_SHIFT ( 8UL )

/* Masks off all bits but the VECTACTIVE bits in the ICSR register. */

#define portVECTACTIVE_MASK ( 0xFFUL )

/* Constants required to set up the initial stack. */

#define portINITIAL_XPSR ( 0x01000000UL )

/* The systick is a 24-bit counter. */

#define portMAX_24_BIT_NUMBER ( 0xffffffUL )

/* A fiddle factor to estimate the number of SysTick counts that would have

* occurred while the SysTick counter is stopped during tickless idle

* calculations. */

#define portMISSED_COUNTS_FACTOR ( 45UL )

/* For strict compliance with the Cortex-M spec the task start address should

* have bit-0 clear, as it is loaded into the PC on exit from an ISR. */

#define portSTART_ADDRESS_MASK ( ( StackType_t ) 0xfffffffeUL )

/* Let the user override the pre-loading of the initial LR with the address of

* prvTaskExitError() in case it messes up unwinding of the stack in the

* debugger. */

#ifdef configTASK_RETURN_ADDRESS

#define portTASK_RETURN_ADDRESS configTASK_RETURN_ADDRESS

#else

#define portTASK_RETURN_ADDRESS prvTaskExitError

#endif

/*

* Setup the timer to generate the tick interrupts. The implementation in this

* file is weak to allow application writers to change the timer used to

* generate the tick interrupt.

*/

void vPortSetupTimerInterrupt( void );

/*

* Exception handlers.

*/

void xPortPendSVHandler( void ) __attribute__( ( naked ) );

void xPortSysTickHandler( void );

void vPortSVCHandler( void ) __attribute__( ( naked ) );

/*

* Start first task is a separate function so it can be tested in isolation.

*/

static void prvPortStartFirstTask( void ) __attribute__( ( naked ) );

/*

* Used to catch tasks that attempt to return from their implementing function.

*/

static void prvTaskExitError( void );

/*-----------------------------------------------------------*/

/* Each task maintains its own interrupt status in the critical nesting

* variable. */

static UBaseType_t uxCriticalNesting = 0xaaaaaaaa;

/*

* The number of SysTick increments that make up one tick period.

*/

#if ( configUSE_TICKLESS_IDLE == 1 )

static uint32_t ulTimerCountsForOneTick = 0;

#endif /* configUSE_TICKLESS_IDLE */

/*

* The maximum number of tick periods that can be suppressed is limited by the

* 24 bit resolution of the SysTick timer.

*/

#if ( configUSE_TICKLESS_IDLE == 1 )

static uint32_t xMaximumPossibleSuppressedTicks = 0;

#endif /* configUSE_TICKLESS_IDLE */

/*

* Compensate for the CPU cycles that pass while the SysTick is stopped (low

* power functionality only.

*/

#if ( configUSE_TICKLESS_IDLE == 1 )

static uint32_t ulStoppedTimerCompensation = 0;

#endif /* configUSE_TICKLESS_IDLE */

/*

* Used by the portASSERT_IF_INTERRUPT_PRIORITY_INVALID() macro to ensure

* FreeRTOS API functions are not called from interrupts that have been assigned

* a priority above configMAX_SYSCALL_INTERRUPT_PRIORITY.

*/

#if ( configASSERT_DEFINED == 1 )

static uint8_t ucMaxSysCallPriority = 0;

static uint32_t ulMaxPRIGROUPValue = 0;

static const volatile uint8_t * const pcInterruptPriorityRegisters = ( const volatile uint8_t * const ) portNVIC_IP_REGISTERS_OFFSET_16;

#endif /* configASSERT_DEFINED */

/*-----------------------------------------------------------*/

/*

* See header file for description.

*/

StackType_t * pxPortInitialiseStack( StackType_t * pxTopOfStack,

TaskFunction_t pxCode,

void * pvParameters )

{

/* Simulate the stack frame as it would be created by a context switch

* interrupt. */

pxTopOfStack--; /* Offset added to account for the way the MCU uses the stack on entry/exit of interrupts. */

*pxTopOfStack = portINITIAL_XPSR; /* xPSR */

pxTopOfStack--;

*pxTopOfStack = ( ( StackType_t ) pxCode ) & portSTART_ADDRESS_MASK; /* PC */

pxTopOfStack--;

*pxTopOfStack = ( StackType_t ) portTASK_RETURN_ADDRESS; /* LR */

pxTopOfStack -= 5; /* R12, R3, R2 and R1. */

*pxTopOfStack = ( StackType_t ) pvParameters; /* R0 */

pxTopOfStack -= 8; /* R11, R10, R9, R8, R7, R6, R5 and R4. */

return pxTopOfStack;

}

/*-----------------------------------------------------------*/

static void prvTaskExitError( void )

{

volatile uint32_t ulDummy = 0UL;

/* A function that implements a task must not exit or attempt to return to

* its caller as there is nothing to return to. If a task wants to exit it

* should instead call vTaskDelete( NULL ).

*

* Artificially force an assert() to be triggered if configASSERT() is

* defined, then stop here so application writers can catch the error. */

configASSERT( uxCriticalNesting == ~0UL );

portDISABLE_INTERRUPTS();

while( ulDummy == 0 )

{

/* This file calls prvTaskExitError() after the scheduler has been

* started to remove a compiler warning about the function being defined

* but never called. ulDummy is used purely to quieten other warnings

* about code appearing after this function is called - making ulDummy

* volatile makes the compiler think the function could return and

* therefore not output an 'unreachable code' warning for code that appears

* after it. */

}

}

/*-----------------------------------------------------------*/

void vPortSVCHandler( void )

{

__asm volatile (

" ldr r3, pxCurrentTCBConst2 \n"/* Restore the context. */

" ldr r1, [r3] \n"/* Use pxCurrentTCBConst to get the pxCurrentTCB address. */

" ldr r0, [r1] \n"/* The first item in pxCurrentTCB is the task top of stack. */

" ldmia r0!, {r4-r11} \n"/* Pop the registers that are not automatically saved on exception entry and the critical nesting count. */

" msr psp, r0 \n"/* Restore the task stack pointer. */

" isb \n"

" mov r0, #0 \n"

" msr basepri, r0 \n"

" orr r14, #0xd \n"

" bx r14 \n"

" \n"

" .align 4 \n"

"pxCurrentTCBConst2: .word pxCurrentTCB \n"

);

}

/*-----------------------------------------------------------*/

static void prvPortStartFirstTask( void )

{

__asm volatile (

" ldr r0, =0xE000ED08 \n"/* Use the NVIC offset register to locate the stack. */

" ldr r0, [r0] \n"

" ldr r0, [r0] \n"

" msr msp, r0 \n"/* Set the msp back to the start of the stack. */

" cpsie i \n"/* Globally enable interrupts. */

" cpsie f \n"

" dsb \n"

" isb \n"

" svc 0 \n"/* System call to start first task. */

" nop \n"

" .ltorg \n"

);

}

/*-----------------------------------------------------------*/

/*

* See header file for description.

*/

BaseType_t xPortStartScheduler( void )

{

/* configMAX_SYSCALL_INTERRUPT_PRIORITY must not be set to 0.

* See https://www.FreeRTOS.org/RTOS-Cortex-M3-M4.html */

configASSERT( configMAX_SYSCALL_INTERRUPT_PRIORITY );

#if ( configASSERT_DEFINED == 1 )

{

volatile uint32_t ulOriginalPriority;

volatile uint8_t * const pucFirstUserPriorityRegister = ( volatile uint8_t * const ) ( portNVIC_IP_REGISTERS_OFFSET_16 + portFIRST_USER_INTERRUPT_NUMBER );

volatile uint8_t ucMaxPriorityValue;

/* Determine the maximum priority from which ISR safe FreeRTOS API

* functions can be called. ISR safe functions are those that end in

* "FromISR". FreeRTOS maintains separate thread and ISR API functions to

* ensure interrupt entry is as fast and simple as possible.

*

* Save the interrupt priority value that is about to be clobbered. */

ulOriginalPriority = *pucFirstUserPriorityRegister;

/* Determine the number of priority bits available. First write to all

* possible bits. */

*pucFirstUserPriorityRegister = portMAX_8_BIT_VALUE;

/* Read the value back to see how many bits stuck. */

ucMaxPriorityValue = *pucFirstUserPriorityRegister;

/* Use the same mask on the maximum system call priority. */

ucMaxSysCallPriority = configMAX_SYSCALL_INTERRUPT_PRIORITY & ucMaxPriorityValue;

/* Calculate the maximum acceptable priority group value for the number

* of bits read back. */

ulMaxPRIGROUPValue = portMAX_PRIGROUP_BITS;

while( ( ucMaxPriorityValue & portTOP_BIT_OF_BYTE ) == portTOP_BIT_OF_BYTE )

{

ulMaxPRIGROUPValue--;

ucMaxPriorityValue <<= ( uint8_t ) 0x01;

}

#ifdef __NVIC_PRIO_BITS

{

/* Check the CMSIS configuration that defines the number of

* priority bits matches the number of priority bits actually queried

* from the hardware. */

configASSERT( ( portMAX_PRIGROUP_BITS - ulMaxPRIGROUPValue ) == __NVIC_PRIO_BITS );

}

#endif

#ifdef configPRIO_BITS

{

/* Check the FreeRTOS configuration that defines the number of

* priority bits matches the number of priority bits actually queried

* from the hardware. */

configASSERT( ( portMAX_PRIGROUP_BITS - ulMaxPRIGROUPValue ) == configPRIO_BITS );

}

#endif

/* Shift the priority group value back to its position within the AIRCR

* register. */

ulMaxPRIGROUPValue <<= portPRIGROUP_SHIFT;

ulMaxPRIGROUPValue &= portPRIORITY_GROUP_MASK;

/* Restore the clobbered interrupt priority register to its original

* value. */

*pucFirstUserPriorityRegister = ulOriginalPriority;

}

#endif /* conifgASSERT_DEFINED */

/* Make PendSV and SysTick the lowest priority interrupts. */

portNVIC_SHPR3_REG |= portNVIC_PENDSV_PRI;

portNVIC_SHPR3_REG |= portNVIC_SYSTICK_PRI;

/* Start the timer that generates the tick ISR. Interrupts are disabled

* here already. */

vPortSetupTimerInterrupt();

/* Initialise the critical nesting count ready for the first task. */

uxCriticalNesting = 0;

/* Start the first task. */

prvPortStartFirstTask();

/* Should never get here as the tasks will now be executing! Call the task

* exit error function to prevent compiler warnings about a static function

* not being called in the case that the application writer overrides this

* functionality by defining configTASK_RETURN_ADDRESS. Call

* vTaskSwitchContext() so link time optimisation does not remove the

* symbol. */

vTaskSwitchContext();

prvTaskExitError();

/* Should not get here! */

return 0;

}

/*-----------------------------------------------------------*/

void vPortEndScheduler( void )

{

/* Not implemented in ports where there is nothing to return to.

* Artificially force an assert. */

configASSERT( uxCriticalNesting == 1000UL );

}

/*-----------------------------------------------------------*/

void vPortEnterCritical( void )

{

portDISABLE_INTERRUPTS();

uxCriticalNesting++;

/* This is not the interrupt safe version of the enter critical function so

* assert() if it is being called from an interrupt context. Only API

* functions that end in "FromISR" can be used in an interrupt. Only assert if

* the critical nesting count is 1 to protect against recursive calls if the

* assert function also uses a critical section. */

if( uxCriticalNesting == 1 )

{

configASSERT( ( portNVIC_INT_CTRL_REG & portVECTACTIVE_MASK ) == 0 );

}

}

/*-----------------------------------------------------------*/

void vPortExitCritical( void )

{

configASSERT( uxCriticalNesting );

uxCriticalNesting--;

if( uxCriticalNesting == 0 )

{

portENABLE_INTERRUPTS();

}

}

/*-----------------------------------------------------------*/

void xPortPendSVHandler( void )

{

/* This is a naked function. */

__asm volatile

(

" mrs r0, psp \n"

" isb \n"

" \n"

" ldr r3, pxCurrentTCBConst \n"/* Get the location of the current TCB. */

" ldr r2, [r3] \n"

" \n"

" stmdb r0!, {r4-r11} \n"/* Save the remaining registers. */

" str r0, [r2] \n"/* Save the new top of stack into the first member of the TCB. */

" \n"

" stmdb sp!, {r3, r14} \n"

" mov r0, %0 \n"

" msr basepri, r0 \n"

" bl vTaskSwitchContext \n"

" mov r0, #0 \n"

" msr basepri, r0 \n"

" ldmia sp!, {r3, r14} \n"

" \n"/* Restore the context, including the critical nesting count. */

" ldr r1, [r3] \n"

" ldr r0, [r1] \n"/* The first item in pxCurrentTCB is the task top of stack. */

" ldmia r0!, {r4-r11} \n"/* Pop the registers. */

" msr psp, r0 \n"

" isb \n"

" bx r14 \n"

" \n"

" .align 4 \n"

"pxCurrentTCBConst: .word pxCurrentTCB \n"

::"i" ( configMAX_SYSCALL_INTERRUPT_PRIORITY )

);

}

/*-----------------------------------------------------------*/

void xPortSysTickHandler( void )

{

/* The SysTick runs at the lowest interrupt priority, so when this interrupt

* executes all interrupts must be unmasked. There is therefore no need to

* save and then restore the interrupt mask value as its value is already

* known. */

portDISABLE_INTERRUPTS();

{

/* Increment the RTOS tick. */

if( xTaskIncrementTick() != pdFALSE )

{

/* A context switch is required. Context switching is performed in

* the PendSV interrupt. Pend the PendSV interrupt. */

portNVIC_INT_CTRL_REG = portNVIC_PENDSVSET_BIT;

}

}

portENABLE_INTERRUPTS();

}

/*-----------------------------------------------------------*/

#if ( configUSE_TICKLESS_IDLE == 1 )

__attribute__( ( weak ) ) void vPortSuppressTicksAndSleep( TickType_t xExpectedIdleTime )

{

uint32_t ulReloadValue, ulCompleteTickPeriods, ulCompletedSysTickDecrements;

TickType_t xModifiableIdleTime;

/* Make sure the SysTick reload value does not overflow the counter. */

if( xExpectedIdleTime > xMaximumPossibleSuppressedTicks )

{

xExpectedIdleTime = xMaximumPossibleSuppressedTicks;

}

/* Stop the SysTick momentarily. The time the SysTick is stopped for

* is accounted for as best it can be, but using the tickless mode will

* inevitably result in some tiny drift of the time maintained by the

* kernel with respect to calendar time. */

portNVIC_SYSTICK_CTRL_REG &= ~portNVIC_SYSTICK_ENABLE_BIT;

/* Calculate the reload value required to wait xExpectedIdleTime

* tick periods. -1 is used because this code will execute part way

* through one of the tick periods. */

ulReloadValue = portNVIC_SYSTICK_CURRENT_VALUE_REG + ( ulTimerCountsForOneTick * ( xExpectedIdleTime - 1UL ) );

if( ulReloadValue > ulStoppedTimerCompensation )

{

ulReloadValue -= ulStoppedTimerCompensation;

}

/* Enter a critical section but don't use the taskENTER_CRITICAL()

* method as that will mask interrupts that should exit sleep mode. */

__asm volatile ( "cpsid i" ::: "memory" );

__asm volatile ( "dsb" );

__asm volatile ( "isb" );

/* If a context switch is pending or a task is waiting for the scheduler

* to be unsuspended then abandon the low power entry. */

if( eTaskConfirmSleepModeStatus() == eAbortSleep )

{

/* Restart from whatever is left in the count register to complete

* this tick period. */

portNVIC_SYSTICK_LOAD_REG = portNVIC_SYSTICK_CURRENT_VALUE_REG;

/* Restart SysTick. */

portNVIC_SYSTICK_CTRL_REG |= portNVIC_SYSTICK_ENABLE_BIT;

/* Reset the reload register to the value required for normal tick

* periods. */

portNVIC_SYSTICK_LOAD_REG = ulTimerCountsForOneTick - 1UL;

/* Re-enable interrupts - see comments above the cpsid instruction()

* above. */

__asm volatile ( "cpsie i" ::: "memory" );

}

else

{

/* Set the new reload value. */

portNVIC_SYSTICK_LOAD_REG = ulReloadValue;

/* Clear the SysTick count flag and set the count value back to

* zero. */

portNVIC_SYSTICK_CURRENT_VALUE_REG = 0UL;

/* Restart SysTick. */

portNVIC_SYSTICK_CTRL_REG |= portNVIC_SYSTICK_ENABLE_BIT;

/* Sleep until something happens. configPRE_SLEEP_PROCESSING() can

* set its parameter to 0 to indicate that its implementation contains

* its own wait for interrupt or wait for event instruction, and so wfi

* should not be executed again. However, the original expected idle

* time variable must remain unmodified, so a copy is taken. */

xModifiableIdleTime = xExpectedIdleTime;

configPRE_SLEEP_PROCESSING( xModifiableIdleTime );

if( xModifiableIdleTime > 0 )

{

__asm volatile ( "dsb" ::: "memory" );

__asm volatile ( "wfi" );

__asm volatile ( "isb" );

}

configPOST_SLEEP_PROCESSING( xExpectedIdleTime );

/* Re-enable interrupts to allow the interrupt that brought the MCU

* out of sleep mode to execute immediately. see comments above

* __disable_interrupt() call above. */

__asm volatile ( "cpsie i" ::: "memory" );

__asm volatile ( "dsb" );

__asm volatile ( "isb" );

/* Disable interrupts again because the clock is about to be stopped

* and interrupts that execute while the clock is stopped will increase

* any slippage between the time maintained by the RTOS and calendar

* time. */

__asm volatile ( "cpsid i" ::: "memory" );

__asm volatile ( "dsb" );

__asm volatile ( "isb" );

/* Disable the SysTick clock without reading the

* portNVIC_SYSTICK_CTRL_REG register to ensure the

* portNVIC_SYSTICK_COUNT_FLAG_BIT is not cleared if it is set. Again,

* the time the SysTick is stopped for is accounted for as best it can

* be, but using the tickless mode will inevitably result in some tiny

* drift of the time maintained by the kernel with respect to calendar

* time*/

portNVIC_SYSTICK_CTRL_REG = ( portNVIC_SYSTICK_CLK_BIT | portNVIC_SYSTICK_INT_BIT );

/* Determine if the SysTick clock has already counted to zero and

* been set back to the current reload value (the reload back being

* correct for the entire expected idle time) or if the SysTick is yet

* to count to zero (in which case an interrupt other than the SysTick

* must have brought the system out of sleep mode). */

if( ( portNVIC_SYSTICK_CTRL_REG & portNVIC_SYSTICK_COUNT_FLAG_BIT ) != 0 )

{

uint32_t ulCalculatedLoadValue;

/* The tick interrupt is already pending, and the SysTick count

* reloaded with ulReloadValue. Reset the

* portNVIC_SYSTICK_LOAD_REG with whatever remains of this tick

* period. */

ulCalculatedLoadValue = ( ulTimerCountsForOneTick - 1UL ) - ( ulReloadValue - portNVIC_SYSTICK_CURRENT_VALUE_REG );

/* Don't allow a tiny value, or values that have somehow

* underflowed because the post sleep hook did something

* that took too long. */

if( ( ulCalculatedLoadValue < ulStoppedTimerCompensation ) || ( ulCalculatedLoadValue > ulTimerCountsForOneTick ) )

{

ulCalculatedLoadValue = ( ulTimerCountsForOneTick - 1UL );

}

portNVIC_SYSTICK_LOAD_REG = ulCalculatedLoadValue;

/* As the pending tick will be processed as soon as this

* function exits, the tick value maintained by the tick is stepped

* forward by one less than the time spent waiting. */

ulCompleteTickPeriods = xExpectedIdleTime - 1UL;

}

else

{

/* Something other than the tick interrupt ended the sleep.

* Work out how long the sleep lasted rounded to complete tick

* periods (not the ulReload value which accounted for part

* ticks). */

ulCompletedSysTickDecrements = ( xExpectedIdleTime * ulTimerCountsForOneTick ) - portNVIC_SYSTICK_CURRENT_VALUE_REG;

/* How many complete tick periods passed while the processor

* was waiting? */

ulCompleteTickPeriods = ulCompletedSysTickDecrements / ulTimerCountsForOneTick;

/* The reload value is set to whatever fraction of a single tick

* period remains. */

portNVIC_SYSTICK_LOAD_REG = ( ( ulCompleteTickPeriods + 1UL ) * ulTimerCountsForOneTick ) - ulCompletedSysTickDecrements;

}

/* Restart SysTick so it runs from portNVIC_SYSTICK_LOAD_REG

* again, then set portNVIC_SYSTICK_LOAD_REG back to its standard

* value. */

portNVIC_SYSTICK_CURRENT_VALUE_REG = 0UL;

portNVIC_SYSTICK_CTRL_REG |= portNVIC_SYSTICK_ENABLE_BIT;

vTaskStepTick( ulCompleteTickPeriods );

portNVIC_SYSTICK_LOAD_REG = ulTimerCountsForOneTick - 1UL;

/* Exit with interrupts enabled. */

__asm volatile ( "cpsie i" ::: "memory" );

}

}

#endif /* configUSE_TICKLESS_IDLE */

/*-----------------------------------------------------------*/

/*

* Setup the systick timer to generate the tick interrupts at the required

* frequency.

*/

__attribute__( ( weak ) ) void vPortSetupTimerInterrupt( void )

{

/* Calculate the constants required to configure the tick interrupt. */

#if ( configUSE_TICKLESS_IDLE == 1 )

{

ulTimerCountsForOneTick = ( configSYSTICK_CLOCK_HZ / configTICK_RATE_HZ );

xMaximumPossibleSuppressedTicks = portMAX_24_BIT_NUMBER / ulTimerCountsForOneTick;

ulStoppedTimerCompensation = portMISSED_COUNTS_FACTOR / ( configCPU_CLOCK_HZ / configSYSTICK_CLOCK_HZ );

}

#endif /* configUSE_TICKLESS_IDLE */

/* Stop and clear the SysTick. */

portNVIC_SYSTICK_CTRL_REG = 0UL;

portNVIC_SYSTICK_CURRENT_VALUE_REG = 0UL;

/* Configure SysTick to interrupt at the requested rate. */

portNVIC_SYSTICK_LOAD_REG = ( configSYSTICK_CLOCK_HZ / configTICK_RATE_HZ ) - 1UL;

portNVIC_SYSTICK_CTRL_REG = ( portNVIC_SYSTICK_CLK_BIT | portNVIC_SYSTICK_INT_BIT | portNVIC_SYSTICK_ENABLE_BIT );

}

/*-----------------------------------------------------------*/

#if ( configASSERT_DEFINED == 1 )

void vPortValidateInterruptPriority( void )

{

uint32_t ulCurrentInterrupt;

uint8_t ucCurrentPriority;

/* Obtain the number of the currently executing interrupt. */

__asm volatile ( "mrs %0, ipsr" : "=r" ( ulCurrentInterrupt )::"memory" );

/* Is the interrupt number a user defined interrupt? */

if( ulCurrentInterrupt >= portFIRST_USER_INTERRUPT_NUMBER )

{

/* Look up the interrupt's priority. */

ucCurrentPriority = pcInterruptPriorityRegisters[ ulCurrentInterrupt ];

/* The following assertion will fail if a service routine (ISR) for

* an interrupt that has been assigned a priority above

* configMAX_SYSCALL_INTERRUPT_PRIORITY calls an ISR safe FreeRTOS API

* function. ISR safe FreeRTOS API functions must *only* be called

* from interrupts that have been assigned a priority at or below

* configMAX_SYSCALL_INTERRUPT_PRIORITY.

*

* Numerically low interrupt priority numbers represent logically high

* interrupt priorities, therefore the priority of the interrupt must

* be set to a value equal to or numerically *higher* than

* configMAX_SYSCALL_INTERRUPT_PRIORITY.

*

* Interrupts that use the FreeRTOS API must not be left at their

* default priority of zero as that is the highest possible priority,

* which is guaranteed to be above configMAX_SYSCALL_INTERRUPT_PRIORITY,

* and therefore also guaranteed to be invalid.

*

* FreeRTOS maintains separate thread and ISR API functions to ensure

* interrupt entry is as fast and simple as possible.

*

* The following links provide detailed information:

* https://www.FreeRTOS.org/RTOS-Cortex-M3-M4.html

* https://www.FreeRTOS.org/FAQHelp.html */

configASSERT( ucCurrentPriority >= ucMaxSysCallPriority );

}

/* Priority grouping: The interrupt controller (NVIC) allows the bits

* that define each interrupt's priority to be split between bits that

* define the interrupt's pre-emption priority bits and bits that define

* the interrupt's sub-priority. For simplicity all bits must be defined

* to be pre-emption priority bits. The following assertion will fail if

* this is not the case (if some bits represent a sub-priority).

*

* If the application only uses CMSIS libraries for interrupt

* configuration then the correct setting can be achieved on all Cortex-M

* devices by calling NVIC_SetPriorityGrouping( 0 ); before starting the

* scheduler. Note however that some vendor specific peripheral libraries

* assume a non-zero priority group setting, in which cases using a value

* of zero will result in unpredictable behaviour. */

configASSERT( ( portAIRCR_REG & portPRIORITY_GROUP_MASK ) <= ulMaxPRIGROUPValue );

}

#endif /* configASSERT_DEFINED */

如下代码替换portmacro.h文件

/*

* FreeRTOS Kernel V10.4.1

* Copyright (C) 2020 Amazon.com, Inc. or its affiliates. All Rights Reserved.

*

* Permission is hereby granted, free of charge, to any person obtaining a copy of

* this software and associated documentation files (the "Software"), to deal in

* the Software without restriction, including without limitation the rights to

* use, copy, modify, merge, publish, distribute, sublicense, and/or sell copies of

* the Software, and to permit persons to whom the Software is furnished to do so,

* subject to the following conditions:

*

* The above copyright notice and this permission notice shall be included in all

* copies or substantial portions of the Software.

*

* THE SOFTWARE IS PROVIDED "AS IS", WITHOUT WARRANTY OF ANY KIND, EXPRESS OR

* IMPLIED, INCLUDING BUT NOT LIMITED TO THE WARRANTIES OF MERCHANTABILITY, FITNESS

* FOR A PARTICULAR PURPOSE AND NONINFRINGEMENT. IN NO EVENT SHALL THE AUTHORS OR

* COPYRIGHT HOLDERS BE LIABLE FOR ANY CLAIM, DAMAGES OR OTHER LIABILITY, WHETHER

* IN AN ACTION OF CONTRACT, TORT OR OTHERWISE, ARISING FROM, OUT OF OR IN

* CONNECTION WITH THE SOFTWARE OR THE USE OR OTHER DEALINGS IN THE SOFTWARE.

*

* https://www.FreeRTOS.org

* https://github.com/FreeRTOS

*

* 1 tab == 4 spaces!

*/

#ifndef PORTMACRO_H

#define PORTMACRO_H

#ifdef __cplusplus

extern "C" {

#endif

/*-----------------------------------------------------------

* Port specific definitions.

*

* The settings in this file configure FreeRTOS correctly for the

* given hardware and compiler.

*

* These settings should not be altered.

*-----------------------------------------------------------

*/

/* Type definitions. */

#define portCHAR char

#define portFLOAT float

#define portDOUBLE double

#define portLONG long

#define portSHORT short

#define portSTACK_TYPE uint32_t

#define portBASE_TYPE long

typedef portSTACK_TYPE StackType_t;

typedef long BaseType_t;

typedef unsigned long UBaseType_t;

#if ( configUSE_16_BIT_TICKS == 1 )

typedef uint16_t TickType_t;

#define portMAX_DELAY ( TickType_t ) 0xffff

#else

typedef uint32_t TickType_t;

#define portMAX_DELAY ( TickType_t ) 0xffffffffUL

/* 32-bit tick type on a 32-bit architecture, so reads of the tick count do

* not need to be guarded with a critical section. */

#define portTICK_TYPE_IS_ATOMIC 1

#endif

/*-----------------------------------------------------------*/

/* Architecture specifics. */

#define portSTACK_GROWTH ( -1 )

#define portTICK_PERIOD_MS ( ( TickType_t ) 1000 / configTICK_RATE_HZ )

#define portBYTE_ALIGNMENT 8

#define portDONT_DISCARD __attribute__( ( used ) )

/*-----------------------------------------------------------*/

/* Scheduler utilities. */

#define portYIELD() \

{ \

/* Set a PendSV to request a context switch. */ \

portNVIC_INT_CTRL_REG = portNVIC_PENDSVSET_BIT; \

\

/* Barriers are normally not required but do ensure the code is completely \

* within the specified behaviour for the architecture. */ \

__asm volatile ( "dsb" ::: "memory" ); \

__asm volatile ( "isb" ); \

}

#define portNVIC_INT_CTRL_REG ( *( ( volatile uint32_t * ) 0xe000ed04 ) )

#define portNVIC_PENDSVSET_BIT ( 1UL << 28UL )

#define portEND_SWITCHING_ISR( xSwitchRequired ) if( xSwitchRequired != pdFALSE ) portYIELD()

#define portYIELD_FROM_ISR( x ) portEND_SWITCHING_ISR( x )

/*-----------------------------------------------------------*/

/* Critical section management. */

extern void vPortEnterCritical( void );

extern void vPortExitCritical( void );

#define portSET_INTERRUPT_MASK_FROM_ISR() ulPortRaiseBASEPRI()

#define portCLEAR_INTERRUPT_MASK_FROM_ISR( x ) vPortSetBASEPRI( x )

#define portDISABLE_INTERRUPTS() vPortRaiseBASEPRI()

#define portENABLE_INTERRUPTS() vPortSetBASEPRI( 0 )

#define portENTER_CRITICAL() vPortEnterCritical()

#define portEXIT_CRITICAL() vPortExitCritical()

/*-----------------------------------------------------------*/

/* Task function macros as described on the FreeRTOS.org WEB site. These are

* not necessary for to use this port. They are defined so the common demo files

* (which build with all the ports) will build. */

#define portTASK_FUNCTION_PROTO( vFunction, pvParameters ) void vFunction( void * pvParameters )

#define portTASK_FUNCTION( vFunction, pvParameters ) void vFunction( void * pvParameters )

/*-----------------------------------------------------------*/

/* Tickless idle/low power functionality. */

#ifndef portSUPPRESS_TICKS_AND_SLEEP

extern void vPortSuppressTicksAndSleep( TickType_t xExpectedIdleTime );

#define portSUPPRESS_TICKS_AND_SLEEP( xExpectedIdleTime ) vPortSuppressTicksAndSleep( xExpectedIdleTime )

#endif

/*-----------------------------------------------------------*/

/* Architecture specific optimisations. */

#ifndef configUSE_PORT_OPTIMISED_TASK_SELECTION

#define configUSE_PORT_OPTIMISED_TASK_SELECTION 1

#endif

#if configUSE_PORT_OPTIMISED_TASK_SELECTION == 1

/* Generic helper function. */

__attribute__( ( always_inline ) ) static inline uint8_t ucPortCountLeadingZeros( uint32_t ulBitmap )

{

uint8_t ucReturn;

__asm volatile ( "clz %0, %1" : "=r" ( ucReturn ) : "r" ( ulBitmap ) : "memory" );

return ucReturn;

}

/* Check the configuration. */

#if ( configMAX_PRIORITIES > 32 )

#error configUSE_PORT_OPTIMISED_TASK_SELECTION can only be set to 1 when configMAX_PRIORITIES is less than or equal to 32. It is very rare that a system requires more than 10 to 15 difference priorities as tasks that share a priority will time slice.

#endif

/* Store/clear the ready priorities in a bit map. */

#define portRECORD_READY_PRIORITY( uxPriority, uxReadyPriorities ) ( uxReadyPriorities ) |= ( 1UL << ( uxPriority ) )

#define portRESET_READY_PRIORITY( uxPriority, uxReadyPriorities ) ( uxReadyPriorities ) &= ~( 1UL << ( uxPriority ) )

/*-----------------------------------------------------------*/

#define portGET_HIGHEST_PRIORITY( uxTopPriority, uxReadyPriorities ) uxTopPriority = ( 31UL - ( uint32_t ) ucPortCountLeadingZeros( ( uxReadyPriorities ) ) )

#endif /* configUSE_PORT_OPTIMISED_TASK_SELECTION */

/*-----------------------------------------------------------*/

#ifdef configASSERT

void vPortValidateInterruptPriority( void );

#define portASSERT_IF_INTERRUPT_PRIORITY_INVALID() vPortValidateInterruptPriority()

#endif

/* portNOP() is not required by this port. */

#define portNOP()

#define portINLINE __inline

#ifndef portFORCE_INLINE

#define portFORCE_INLINE inline __attribute__( ( always_inline ) )

#endif

/*-----------------------------------------------------------*/

portFORCE_INLINE static BaseType_t xPortIsInsideInterrupt( void )

{

uint32_t ulCurrentInterrupt;

BaseType_t xReturn;

/* Obtain the number of the currently executing interrupt. */

__asm volatile ( "mrs %0, ipsr" : "=r" ( ulCurrentInterrupt )::"memory" );

if( ulCurrentInterrupt == 0 )

{

xReturn = pdFALSE;

}

else

{

xReturn = pdTRUE;

}

return xReturn;

}

/*-----------------------------------------------------------*/

portFORCE_INLINE static void vPortRaiseBASEPRI( void )

{

uint32_t ulNewBASEPRI;

__asm volatile

(

" mov %0, %1 \n"\

" msr basepri, %0 \n"\

" isb \n"\

" dsb \n"\

: "=r" ( ulNewBASEPRI ) : "i" ( configMAX_SYSCALL_INTERRUPT_PRIORITY ) : "memory"

);

}

/*-----------------------------------------------------------*/

portFORCE_INLINE static uint32_t ulPortRaiseBASEPRI( void )

{

uint32_t ulOriginalBASEPRI, ulNewBASEPRI;

__asm volatile

(

" mrs %0, basepri \n"\

" mov %1, %2 \n"\

" msr basepri, %1 \n"\

" isb \n"\

" dsb \n"\

: "=r" ( ulOriginalBASEPRI ), "=r" ( ulNewBASEPRI ) : "i" ( configMAX_SYSCALL_INTERRUPT_PRIORITY ) : "memory"

);

/* This return will not be reached but is necessary to prevent compiler

* warnings. */

return ulOriginalBASEPRI;

}

/*-----------------------------------------------------------*/

portFORCE_INLINE static void vPortSetBASEPRI( uint32_t ulNewMaskValue )

{

__asm volatile

(

" msr basepri, %0 "::"r" ( ulNewMaskValue ) : "memory"

);

}

/*-----------------------------------------------------------*/

#define portMEMORY_BARRIER() __asm volatile ( "" ::: "memory" )

#ifdef __cplusplus

}

#endif

#endif /* PORTMACRO_H */