中科亿海微ROM使用

标题

ROM(Read-Only Memory,只读存储器)是一种在FPGA(Field-Programmable Gate Array,现场可编程门阵列)中常用的存储器类型。与RAM(Random Access Memory,机存取存储器)不同,ROM的内容在制造过程中被预先编程,并且无法在运行时修改。

1 :ROM通常用于存储固定的程序代码、常量数据或查找表等,因为它们具有不可变的特性。它的主要特点包括:

①:只读性:ROM中的数据在制造过程中被写入,一旦编程完成,就无法进行修改。这确保了数据的安全性和稳定性;

②:非易失性:ROM中的数据在断电或重启后仍然保持不变,不会丢失。这是与RAM的一个重要区别;

③:高密度:ROM具有较高的存储密度,因为它可以在硬件级别上实现,而不需要像RAM那样用传统的逻辑门来实现。

2:FPGA中通常会使用不同类型的ROM,包括:

①:M4K(Memory 4K):这是Xilinx FPGA系列中常见的一种ROM资源,可以存储4K个数据位。M4K ROM具有灵活的读写接口和配置选项,可以满足不同应用的需求;

②:Block RAM:FPGA中的Block RAM也可以用作ROM,通过在初始化时将数据加载到Block RAM中来实现。Block RAM通常具有较大的存储容量和更高的读写速度;

使用ROM的好处是可以提高系统的性能和资源效率,特别是对于一些不需要在运行时修改的数据和代码。但是,由于ROM的内容无法修改,因此对于需要动态更新的数据,需要使用其他类型的存储器,如RAM。

简介

FPGA中的ROM(Read-Only Memory,只读存储器)起源于计算机系统中的存储器技术。在早期的计算机系统中,ROM被用于存储固定的程序代码和常量数据,以及用于查找表和数据转换等应用。随着FPGA技术的发展,ROM成为了FPGA设计中常用的一种存储器类型。与传统的硬件设计相比,FPGA具有可编程性的优势,可以根据特定的应用需求进行灵活的配置和重新编程。在FPGA中,ROM的设计和实现方式通常是通过在硬件级别上配置逻辑电路来实现。它可以在FPGA芯片制造过程中被预先编程,也可以在设计过程中使用特定的工具和语言来描述和生成ROM的内容。ROM在FPGA设计中具有多种应用,包括存储固定的程序代码、常量数据、查找表和数据转换等。由于ROM具有只读性和非易失性的特点,它可以提供稳定和安全的存储,同时具有较高的存储密度和快速的读取速度。这使得ROM成为了一种重要的存储器类型,被广泛应用于FPGA设计中的不同领域,如数字信号处理、通信系统、图像处理和嵌入式系统等。

正文

引言

-

存储常量数据:ROM常用于存储常量数据,如查找表、预先计算的数学函数值、校正数据等。这些数据在设计过程中是固定的,不需要在运行时进行修改;

-

存储程序代码:在一些应用中,特定的程序代码可以被预先存储在ROM中。这样可以节省FPGA的逻辑资源,并且可以提高系统的性能和响应时间;

-

替代逻辑电路:FPGA中的ROM可以替代一些逻辑电路的功能,特别是对于复杂的查找表和数据转换。使用ROM可以简化设计,并且可以提供更高的性能和资源效率;

-

快速数据存取:由于ROM具有快速的读取特性,它常用于需要快速存取数据的应用,如数字信号处理、图像处理和通信系统等;

-

存储初始化数据:在FPGA设计中,ROM可以用于存储初始化数据,如启动配置、初始化寄存器值等。这些数据在设备上电时被加载到相应的寄存器中,用于初始化系统状态;

-

安全存储:ROM中的数据是只读的,无法被修改。这使得ROM成为存储安全相关数据的理想选择,如加密密钥、安全配置等。

总而言之,FPGA中的ROM提供了一种灵活、高性能和资源高效的存储器选项,可用于存储常量数据、程序代码、查找表和初始化数据等。它在各种应用领域中发挥着重要的作用,使得FPGA设计更加灵活和高效。

主体

使用中科亿海微eLinx开发工具进行编程:

①:以下是使用Verilog开发一套ROM(软核)的示例代码:

module ROM (

input wire [N-1:0] address,

output wire [M-1:0] data

);

reg [M-1:0] rom [0:(2**N)-1];

initial begin

rom[0] = 8'b00000000;

rom[1] = 8'b00000001;

// ...

rom[(2**N)-1] = 8'b11111111;

end

assign data = rom[address];

endmodule

在这个示例中,我们定义了一个名为ROM的模块,该模块具有一个输入端口address(用于指定ROM中的地址)和一个输出端口data(用于输出对应地址的数据)。

在模块内部,我们使用reg类型的数组rom来表示ROM的存储单元。数组的大小为2的N次方,其中N是地址位宽。例如,如果地址位宽为8位,则数组大小为256。

在initial块中,我们可以初始化rom数组中的数据。根据您的需求,将存储在ROM中的数据写入到rom数组的相应位置。在示例中,我们使用8位宽的数据,每个地址存储一个8位的字节。

最后,我们使用assign语句将rom数组中对应地址的数据赋值给输出端口data。

请注意,这只是一个简单的示例,用于说明如何使用Verilog开发一套ROM的软核。实际的ROM设计可能需要更多的功能和控制逻辑,例如读取使能、写使能、读写时序等。具体的设计取决于您的需求和目标平台。

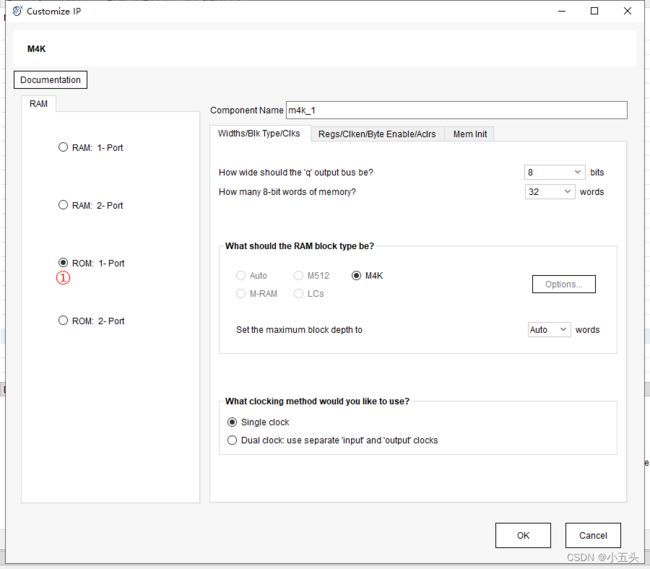

②:使用定制好的IP核进行开发:

注意: 需要手动修改ROM IP核的底层程序,手动添加MIF文件:

手动修改我们需要读取的MIF文件:

module ROM_TOP(

input wire clk,

output [7:0] rom_data

);

reg [4:0] address;

always @ (posedge clk)

address <= address + 1'b1;

m4k_1 u_m4k_1(

.address (address),

.clock (clk),

.q (rom_data)

);

结论

在使用FPGA开发ROM时,有一些要注意的关键点:

-

内存容量:确定所需的ROM容量,即地址位宽和数据位宽。根据应用需求和数据量大小,选择合适的ROM大小。确保ROM的存储容量足够存储所需的数据。

-

内存布局:考虑如何组织ROM的内存布局。根据应用场景和数据存储需求,确定存储单元的分配,如按字节、字、行或其他方式进行分配。合理的内存布局可以提高存取效率和资源利用率。

-

数据初始化:在设计过程中,确保在ROM中正确初始化所需的数据。根据应用需求,编写初始化代码或使用工具进行数据初始化。确认ROM中存储的数据与设计要求一致。

-

读写时序:了解ROM的读写时序要求。根据FPGA芯片和ROM规格,设置正确的时钟频率、读写使能信号和时序约束。确保读取操作和写入操作在正确的时钟周期内完成,并满足ROM的时序要求。

-

仿真验证:使用仿真工具对设计进行验证,确保ROM的功能和数据正确性。通过仿真测试,检查ROM在各种情况下是否按预期工作,并验证所需数据的正确性。

-

优化和资源利用:优化ROM的设计,以减少资源使用和功耗。使用合理的编码方式、压缩算法和存储器布局来提高ROM的效率和资源利用率。

-

灵活性和可扩展性:考虑将ROM设计为可灵活扩展和可配置的。根据需求,设计ROM以支持动态数据更新或通过编程重新配置ROM内容的功能。

-

设计验证和调试:进行系统级验证和调试,确保ROM与其他模块和外设的正确集成。验证ROM与其他电路之间的接口和数据通信是否正常。

通过注意以上关键点,能够更好地开发和使用FPGA中的ROM,确保其功能正确性、性能优化和资源利用率。