【SpinalHDL】Windows10系统搭建SpinalHDL 开发环境

本文主要记载如何从零开始在win平台搭建SpinalHDL开发环境并跑通第一个spinal project demo。

1、环境准备

1.1 软件下载

首先列出需要安装的软件,并逐一对这些软件的功能和其必要性进行说明.

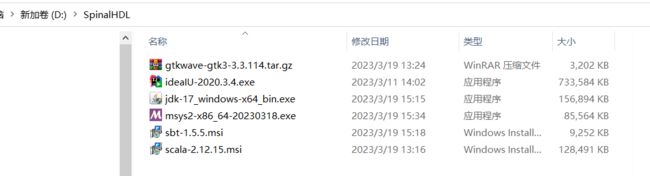

需要安装的软件:IDEA、JDK17、Scala2.12.15、Sbt1.5.5、msys2(verilator)、gtkwave。

各软件说明:首先spinal并不能说是一种编程语言,它只是scala 的一个库,所以我们实际上是在用scala进行开发,scala需要用到JVM,所以需要安装JDK。此外,在win平台开发一个好用的IDE是必要的,IDEA就是这么一个软件,它提供了scala的开发环境。当然仅仅有IDEA是不够的,还需要安装scala插件(在IDEA中装),然后还需要安装scala和sbt,我都是用的.msi独立安装的,sbt是用来构建scala工程的。

上面说的那些软件已经足以建立一个scala工程,至于verilator和gtkwave是为了仿真用的,注意verilator只能对verilog进行仿真,如果是VHDL使用GHDL,具体可以spinal官方DOC

安装verilator要使用msys2进行安装,同时还有一些其他的package需要安装,gtkwave只是一个波形查看工具,安装也非常简单。

IDEA下载网址:https://www.jetbrains.com/zh-cn/idea/

JDK17下载网址:https://www.oracle.com/cn/java/technologies/downloads/#jdk17-windows

Scala下载网址:https://www.scala-lang.org/download/2.12.15.html

sbt下载网址:https://www.scala-sbt.org/download.html

msys2下载网址:https://www.msys2.org/

gtkwave:https://sourceforge.net/projects/gtkwave/

开始安装之前,不妨对所有文件的安装路径做个统一管理,D盘新建SpinalHDL文件夹,后面所有的软件均安装到此路径下。

1.2 安装参考

SpinalHDL环境搭建

基于Windows系统的SpinalHDL开发环境搭建

2021 最新版 JDK 17 下载与安装 步骤演示 (图示版)

SpinalHDL-sim Verilator Windows安装问题

Windows福音——解决仿真工具安装问题

SpinalHDL从建立工程到查看仿真波形

SpinalHDL 开发环境 Windows 安装

2、软件安装

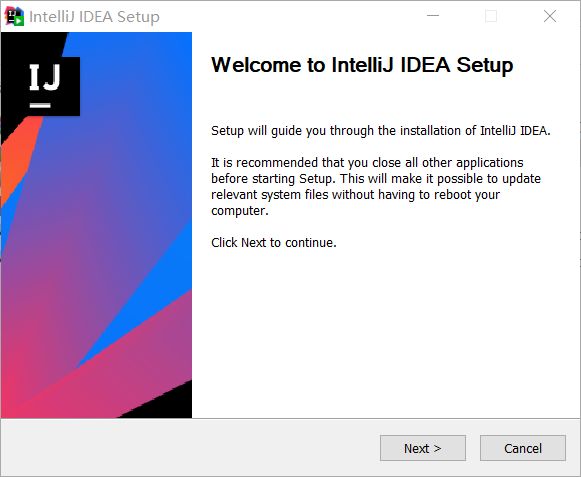

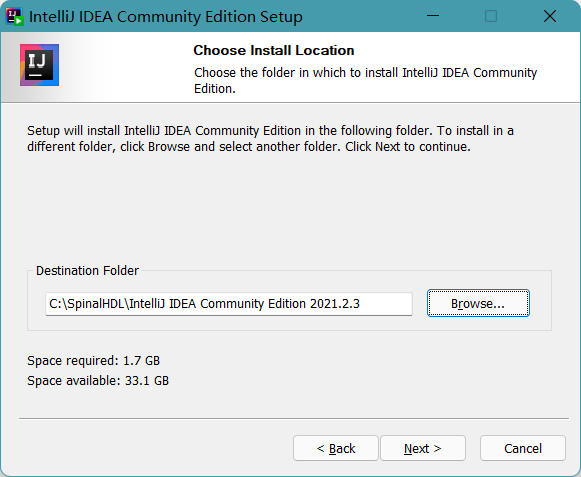

2.1 IntelliJ IDEA安装

修改安装路径

安装IDEA过程中可以勾选加入环境变量

安装成功

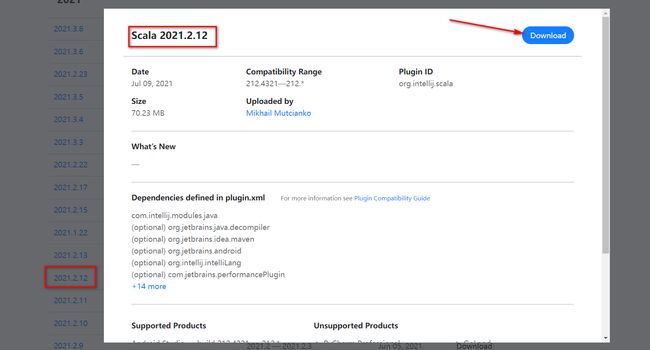

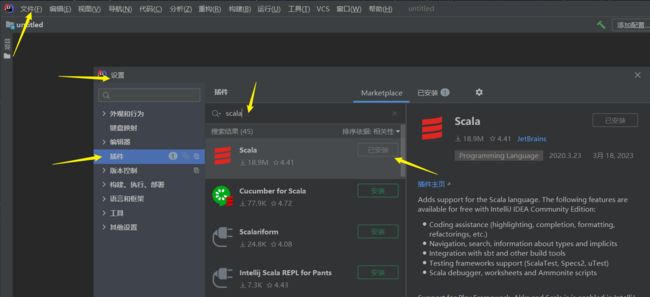

IDEA安装好之后需要安装scala插件,我使用的是离线安装的方式,将插件下载下来,放到D:\SpinalHDL\IntelliJ IDEA Community Edition 2021.2.3\plugins路径下,然后再IDEA里加载一下就可以了。这个路径就是IDEA安装路径,注意一定要放在...\plugins文件夹下。

scala插件下载地址

切到versions页,下拉选择2021.2.12,下载!

下载后的文件名为“scala-intellij-bin-2021.2.12.zip”,将压缩包放到IDEA的安装路径下的...\plugins文件夹下,然后再IDEA里添加激活scala即可。

IDEA内部插件安装如下:

2.2 JDK安装

直接到官网下载安装包JDK官网下载,下软ORACLE软件需要提前注册账号。

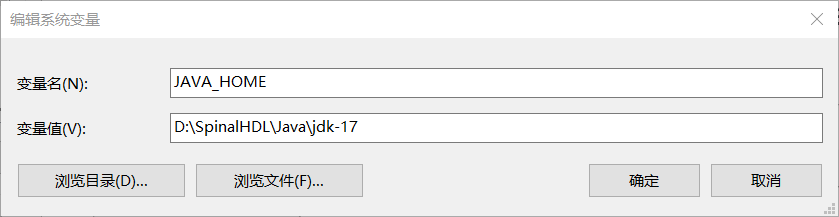

JDK的安装没什么好说的,安装完需要配置环境变量

新建系统变量 变量名:JAVA_HOME 变量值: D:\SpinalHDL\JAVA\jdk-17变量值就是你的安装路径

新建系统变量 变量名:JRE_HOME 变量值: D:\SpinalHDL\JAVA\jdk-17变量值就是你的安装路径

新建系统变量 变量名:CLASSPATH 变量值: .;%JAVA_HOME%\lib;

在系统变量path的 值里面添加%JAVA_HOME%\bin和%JRE_HOME%\jre\bin

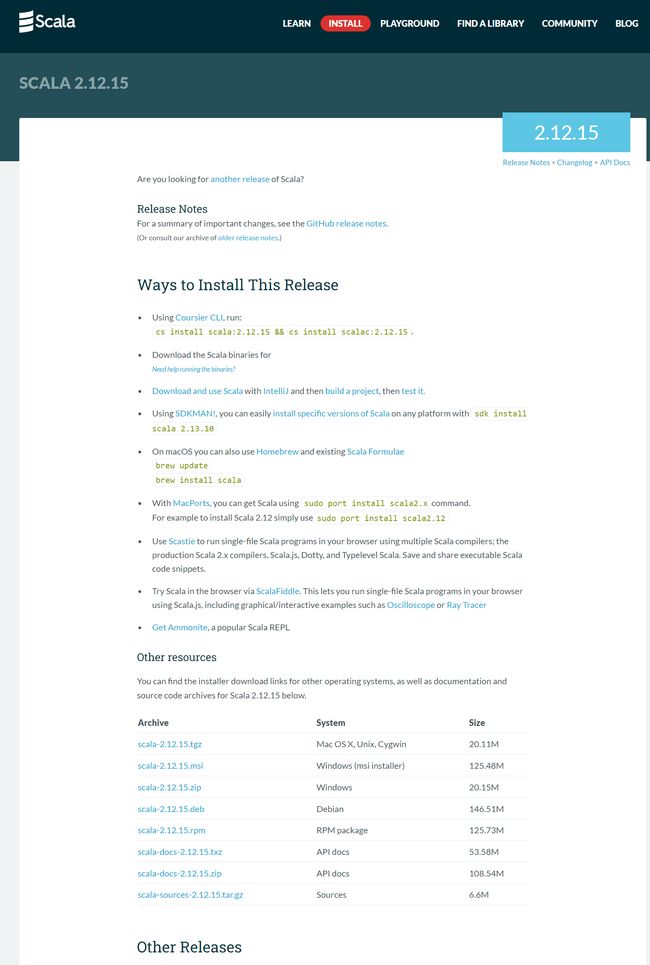

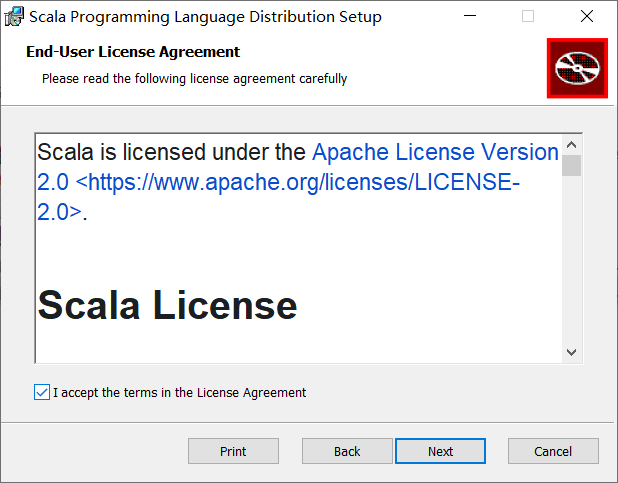

2.3 Scala安装

直接到官网下载安装包Scala下载地址

点击安装msi文件

修改安装路径

安装完之后同样需要添加环境变量

新建系统变量 变量名:SCALA_HOME 变量值: D:\SpinalHDL\scala变量值就是你的安装路径

在系统变量path的 值里面添加%SCALA_HOME%\bin,即安装路径的bin文件夹

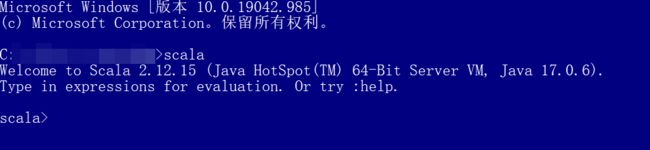

环境变量设置好保存退出后,可以命令行敲 scala 回车后会出现提示信息,包括scala版本以及一些其他信息

命令行启动方式:win+R 输入cmd 回车

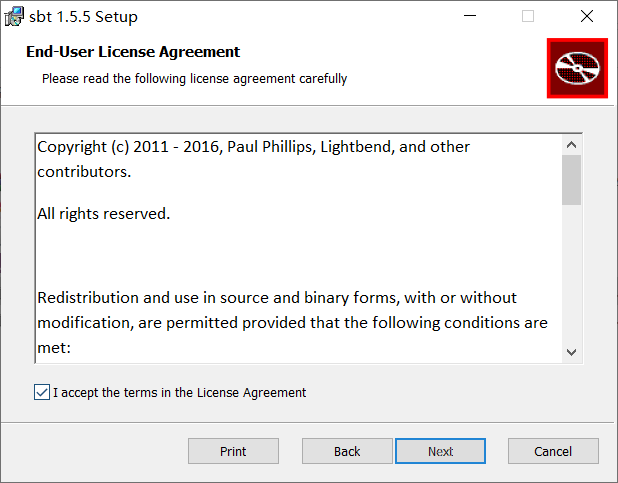

2.4 Sbt安装

直接到官网下载安装包Sbt下载地址

修改路径

安装完之后同样需要添加环境变量

在系统变量path的 值里面添加D:\SpinalHDL\sbt\bin,即安装路径的bin文件夹

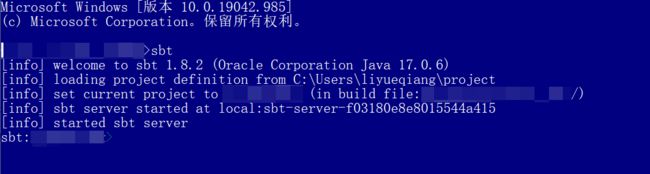

sbt安装好应该也可以在命令行方式验证下

sbt切换国内镜像

安装完后面需要用sbt构建spinal依赖库,默认是国外的源,过程实在是太慢了,而且还有可能失败,所以最好是切换成国内的源。

切换方法:

找到sbt安装目录下conf文件夹下sbtconfig.txt,增加下面两行代码

-Dsbt.global.base=C:/Sbt/.sbt

-Dsbt.repository.config=C:/Sbt/properties在安装目录的.sbt文件夹下新建properties文件(注意没有后缀),打开文件添加代码

[repositories]

local

aliyun: http://maven.aliyun.com/nexus/content/groups/public/

central: http://repo1.maven.org/maven2/这里安装目录下可能并没有.sbt文件夹,新建一个即可,我是直接放在安装目录(D:\SpinalHDL\sbt\)下的,以上方法是网上找来的,这里附上链接sbt配置国内镜像

【SBT】getting org.scala-sbt sbt 1.8.2 (this may take some time)...问题解决

仿真注意事项

接下来得2.5和2.6小节是仿真环境的安装,用verilator进行仿真,然后用Gtkwave查看波形文件,但是我在安装完之后使用一个例子测试的时候仿真总是跑不过去,尝试了很多方法,比如重装msys2和verilator,环境变量清理等等,但是都没有效果,最终发现是安装的iverilog和verilator存在冲突,本来想着iverilog自带Gtkwave,所以就安装了iverilog,但是由于我平时并不适用vhdl,所以安装verilator和Gtkwave就足够了,所以卸载iverilog之后仿真就能跑通了。至于Gtkwave只需要独立安装就行了。

后面3.2小节部分也会放出没解决时的具体报错截图,避免踩坑!

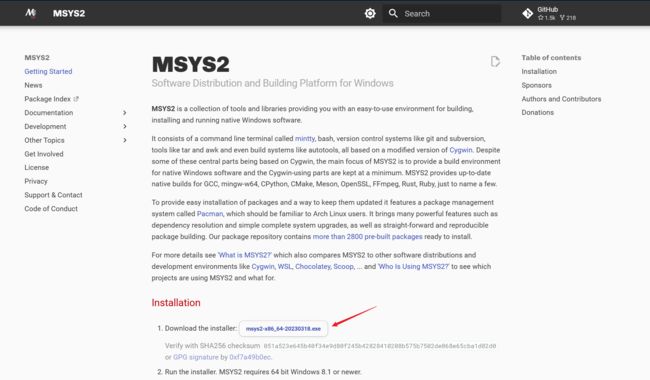

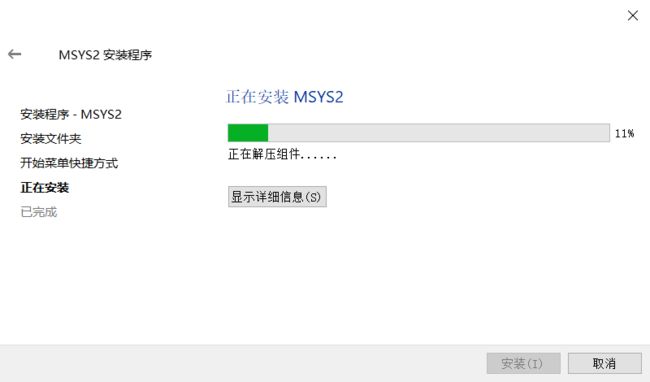

2.5 msys2 安装

直接到官网下载安装包msys2下载地址

安装步骤

修改路径(经验:尽量把msys2安装在C盘)

安装完添加环境变量

在系统变量path里面添加C:\SpinalHDL\msys64\usr\bin;C:\SpinalHDL\msys64\mingw64\bin

2.6 verilator

msys2安装好之后就是verilator的安装了,这里官方文档给出了具体需要安装的指令,我这里给出详细安装过程

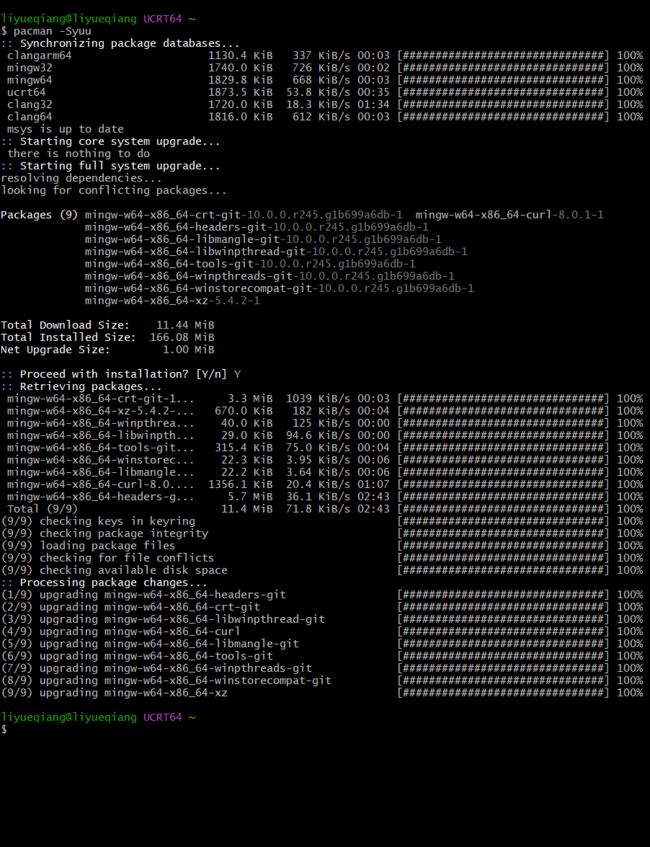

启动msys2之后,先输入pacman -Syuu,然后问你是否安装,敲 Y 确认安装,安装完之后会关掉终端,输入Y确认关闭

然后再次启动msys2,按照指令安装,整个安装过程如下

pacman -Syuu

Y

pacman -S --needed base-devel mingw-w64-x86_64-toolchain

//gcc

Y

pacman -S --needed base-devel mingw-w64-x86_64-toolchain

//make

Y

pacman -S --needed base-devel mingw-w64-x86_64-toolchain

//git

Y

pacman -S mingw-w64-x86_64-verilator

Y总结下来整个过程就是:安装Syuu,确认安装,安装flex,确认安装,安装make,确认安装,安装git,确认安装,安装verilator,确认安装。

2.7 gtkwave安装

直接到官网下载安装包gtkwave安装地址,软件包下载中间出现了输入用户名及密码场景,我这里是忽略重新下载就可以了,可以多下载几次。

gtkwave下载后直接解压到D:\SpinalHDL\ 路径下就行了,然后将bin文件夹下的gtkwave.exe文件发送到桌面快捷方式就行。

3、demo开发

3.1 新建工程

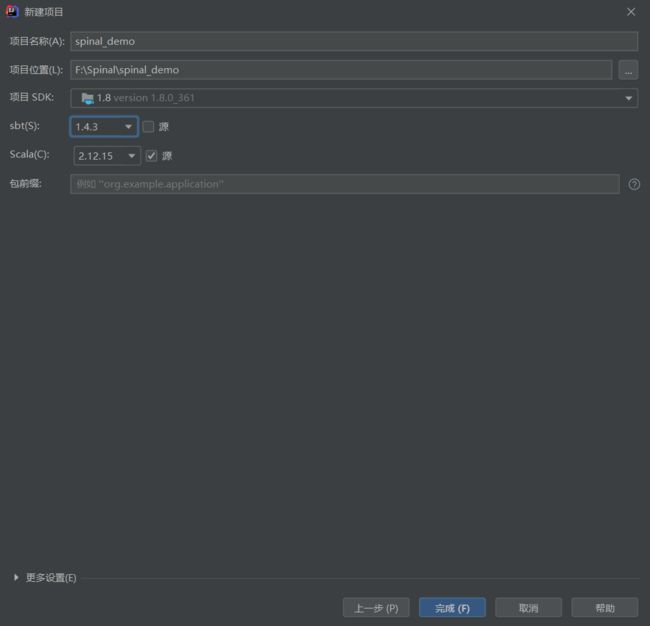

准备好自己的工作空间(自己指定)新建scala工程均放在此路径下

比如我的F:\Spinal\下,以便后面查看,复制一些源文件和波形文件

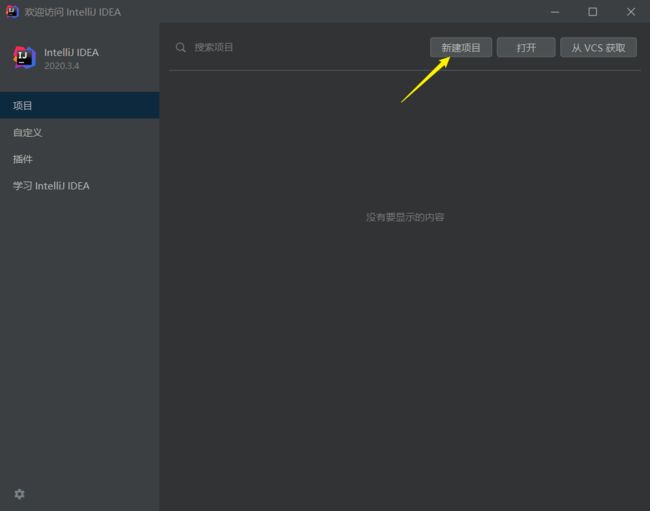

新建工程

打开IDEA,新建工程,完全没有IDEA使用经验的可以一步步跟着来。

3.2 环境准备

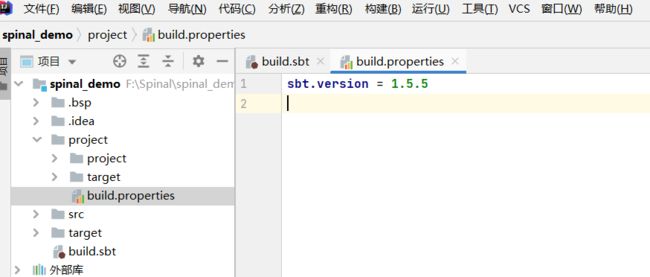

打开build.sbt文件和build.properties文件,.sbt文件新建工程里面只有前三行,然后改成和图中一致。

name := "test"

ThisBuild / version := "1.0"

ThisBuild / scalaVersion := "2.12.15"

val spinalVersion = "1.6.0"

val spinalCore = "com.github.spinalhdl" %% "spinalhdl-core" % spinalVersion

val spinalLib = "com.github.spinalhdl" %% "spinalhdl-lib" % spinalVersion

val spinalIdslPlugin = compilerPlugin("com.github.spinalhdl" %% "spinalhdl-idsl-plugin" % spinalVersion)

lazy val mylib = (project in file("."))

.settings(

name := "SpinalTemplateSbt",

libraryDependencies ++= Seq(spinalCore, spinalLib, spinalIdslPlugin)

)

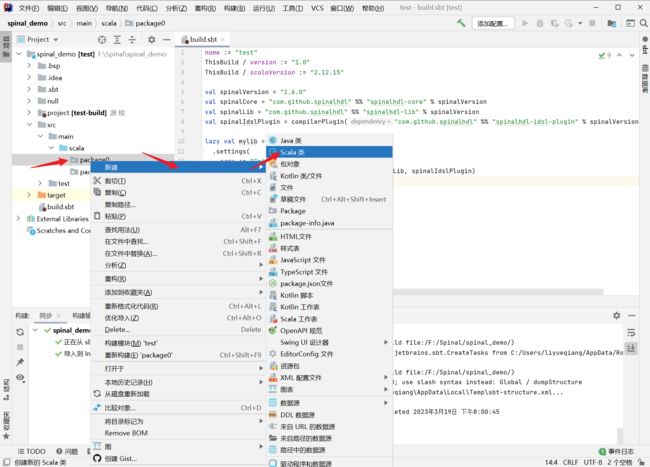

fork := true接下来就是编译sbt关联spinal的库了,具体步骤就是选中build.sbt,右键选件build module test,如果之前编译过出错了,在build窗口点击下那个循环图标Reload sbt project就行了,这个过程需要等待一段时间,如果通不过的话试试换国内的镜像看。

完成之后可以从External Libraries这里看到spinal库都已经关联进来了,之前这里是没有的。

3.3 新建文件

接下来就可以真正建立我们的spinal project了,新建一个package,在package中新建scala 文件,当然你也可以不建package直接新建scala文件,新建package的话比较方便不同rtl设计的文件管理

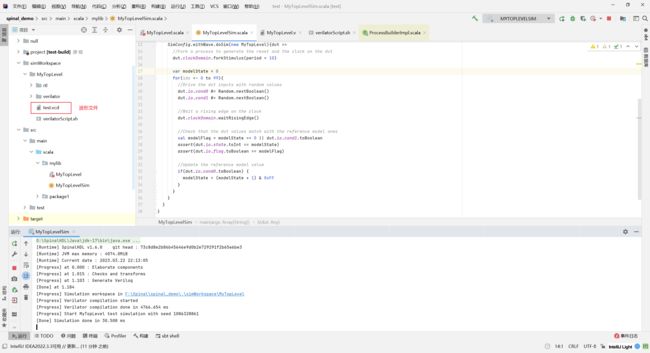

然后把在test_top1.scala文件中就可以开始你的spinal设计了,为了快速跑通整个开发流程,我们先把这段代码复制进去。

3.4 代码开发

注意这段代码实际上是一个计数器,我的设计文件名(test_top1)和module名(Counter)没有统一,只是为了演示这个过程而已

package package1

import spinal.core._

class Counter(width : Int) extends Component{

val io = new Bundle{

val clear = in Bool()

val value = out UInt(width bits)

}

val register = Reg(UInt(width bits)) init(0)

register.addAttribute("keep")

when(io.clear){

register := 0

}.otherwise{

register := register + 1

}

io.value := register

}

object CounterInst {

def main(args: Array[String]) {

SpinalVerilog(new Counter(8))

}

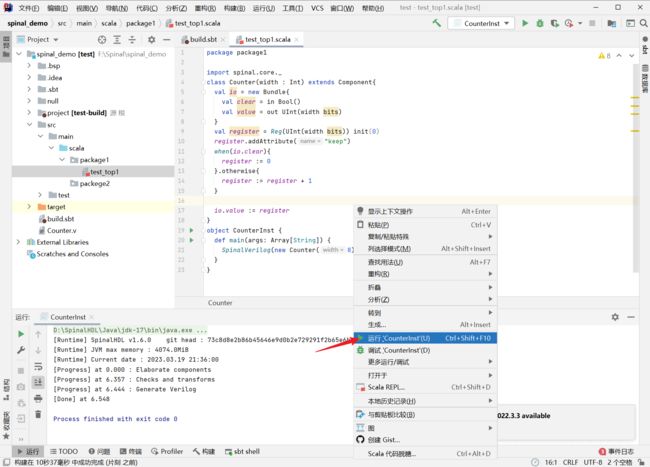

}3.5 编译工程

然后就是运行代码,右键运行或者使用快捷键(Ctrl + Shift +F10)

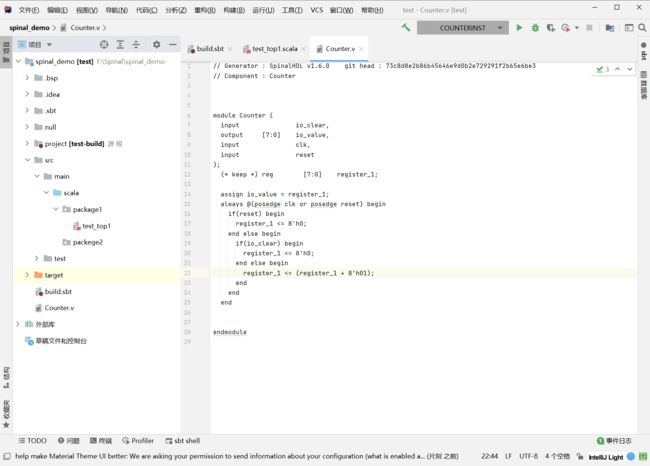

运行完之后你会发现project路径下多了一个Counter.v文件

打开Counter.v就可以查看生成的verilog代码了。

到了这里设计部分就结束了,当然对于FPGAer来讲仿真是必不可少的,接下来就是仿真环境的测试。

4、仿真测试

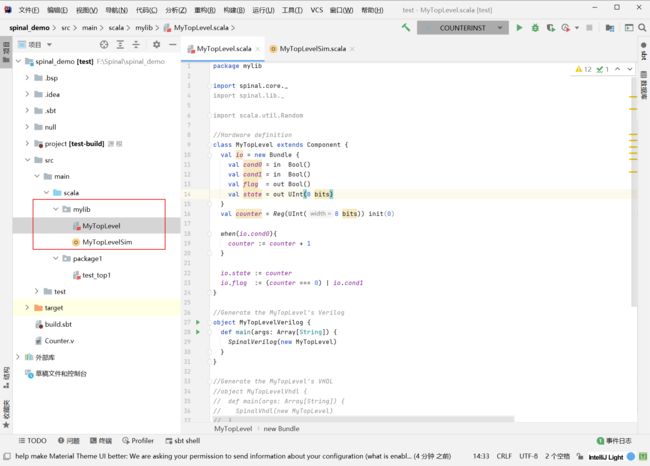

4.1 新建工程

仿真过程遇到的最大的问题是仿真一致跑不过去,报错是找不到verilator.dll,最后发现卸载iverilog之后就可以正常跑通了。

这里新建一个package,然后把设计和仿真文件都放在package里面,然后运行仿真文件就可以跑通了。

package mylib

import spinal.core._

import spinal.lib._

import scala.util.Random

//Hardware definition

class MyTopLevel extends Component {

val io = new Bundle {

val cond0 = in Bool()

val cond1 = in Bool()

val flag = out Bool()

val state = out UInt(8 bits)

}

val counter = Reg(UInt(8 bits)) init(0)

when(io.cond0){

counter := counter + 1

}

io.state := counter

io.flag := (counter === 0) | io.cond1

}

//Generate the MyTopLevel's Verilog

object MyTopLevelVerilog {

def main(args: Array[String]) {

SpinalVerilog(new MyTopLevel)

}

}

//Generate the MyTopLevel's VHDL

//object MyTopLevelVhdl {

// def main(args: Array[String]) {

// SpinalVhdl(new MyTopLevel)

// }

//}

//Define a custom SpinalHDL configuration with synchronous reset instead of the default asynchronous one. This configuration can be resued everywhere

object MySpinalConfig extends SpinalConfig(defaultConfigForClockDomains = ClockDomainConfig(resetKind = SYNC))

//Generate the MyTopLevel's Verilog using the above custom configuration.

object MyTopLevelVerilogWithCustomConfig {

def main(args: Array[String]) {

MySpinalConfig.generateVerilog(new MyTopLevel)

}

}package mylib

import spinal.core._

import spinal.sim._

import spinal.core.sim._

import scala.util.Random

//MyTopLevel's testbench

object MyTopLevelSim {

def main(args: Array[String]) {

SimConfig.withWave.doSim(new MyTopLevel){dut =>

//Fork a process to generate the reset and the clock on the dut

dut.clockDomain.forkStimulus(period = 10)

var modelState = 0

for(idx <- 0 to 99){

//Drive the dut inputs with random values

dut.io.cond0 #= Random.nextBoolean()

dut.io.cond1 #= Random.nextBoolean()

//Wait a rising edge on the clock

dut.clockDomain.waitRisingEdge()

//Check that the dut values match with the reference model ones

val modelFlag = modelState == 0 || dut.io.cond1.toBoolean

assert(dut.io.state.toInt == modelState)

assert(dut.io.flag.toBoolean == modelFlag)

//Update the reference model value

if(dut.io.cond0.toBoolean) {

modelState = (modelState + 1) & 0xFF

}

}

}

}

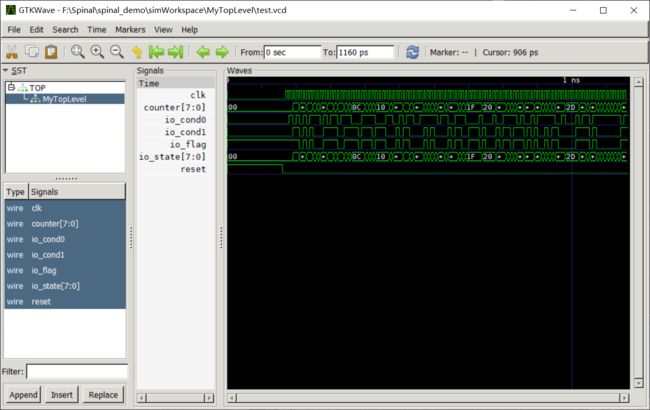

}运行通过之后就会生成波形文件,然后用Gtkwave打开波形文件皆可以查看波形了。

4.2 查看波形

用Gtkwave打开波形文件皆可以查看波形了。

4.3 问题记录

报错是找不到verilator.dll

仿真过程遇到的最大的问题是仿真一致跑不过去,报错是找不到verilator.dll,最后发现卸载iverilog之后就可以正常跑通了。这里是第2章中仿真注意事项的具体情况,如果遇到相同报错的下载iverilog即可解决。

verilatorScript.sh: line 1: verilator_bin.exe: command not found

解决办法

Cannot run program "sh.exe"

解决办法