【ARM 调试】如何从 crash 信息找出问题原因

一、问题背景

粉丝在进行 ARM-A 系列软件编程时遇到以下问题,串口打印这段日志后就重启了,粉丝求助问是什么原因?

Unhandled Exception in EL3.

x30 = 0x0000000000b99b84

x0 = 0x00000000179a25b0

x1 = 0x0000ffffb5b20040

x2 = 0x000000000000ff70

x3 = 0x00000000179a25b0

x4 = 0x0000ffffb5b30000

x5 = 0x00000000179b25b0

x6 = 0x0000000000000000

x7 = 0x0000000000000000

x8 = 0x0000000000000000

x9 = 0x0000000000000000

x10 = 0x0000000000000000

x11 = 0x0000000000000000

x12 = 0x0000000000000000

x13 = 0x0000000000000000

x14 = 0x0000000000000000

x15 = 0x0000000000000000

x16 = 0x0000000000426000

x17 = 0x0000ffffb5bb2dd0

x18 = 0x0000000000000010

x19 = 0x0000000000000003

x20 = 0x00000000179a25b0

x21 = 0x00000000000f0000

x22 = 0x0000000000010000

x23 = 0x000000000040d198

x24 = 0x0000000000000000

x25 = 0x0000ffffb5b20000

x26 = 0x0000000000010000

x27 = 0x0000000000000000

x28 = 0x0000000000000000

x29 = 0x0000fffffaf92680

scr_el3 = 0x000000000403073d

sctlr_el3 = 0x0000000030cd183f

cptr_el3 = 0x0000000000000100

tcr_el3 = 0x0000000080853510

daif = 0x00000000000003c0

mair_el3 = 0x00000000004404ff

spsr_el3 = 0x00000000620002cd

elr_el3 = 0x0000000000b99d84

ttbr0_el3 = 0x0000000000c80001

esr_el3 = 0x00000000be000011

far_el3 = 0x2abf2e72a2b2cff8

spsr_el1 = 0x0000000000000000

elr_el1 = 0x0000000000000000

spsr_abt = 0x0000000000000000

spsr_und = 0x0000000000000000

spsr_irq = 0x0000000000000000

spsr_fiq = 0x0000000000000000

sctlr_el1 = 0x0000000030d00800

actlr_el1 = 0x0000000000000000

cpacr_el1 = 0x0000000000000000

csselr_el1 = 0x0000000000000000

sp_el1 = 0x0000000000000000

esr_el1 = 0x0000000000000000

ttbr0_el1 = 0x0000000000000000

ttbr1_el1 = 0x0000000000000000

mair_el1 = 0x0000000000000000

amair_el1 = 0x0000000000000000

cpupwrctlr_el1 = 0x0000000000000000

icc_ctlr = 0x00000000000a8410

icc_hppir0 = 0x00000000000003fd

icc_hppir1 = 0x000000000000001a

icc_rpr_el1 = 0x00000000000000ff

icc_ap0r0_el1 = 0x0000000000000000

gicd_ispendr regs (Offsets 0x200-0x210)

Offset Value

0x200: 0x0000000000000000

0x204: 0x0000000000000000

0x208: 0x0000000000000000

0x20c: 0x0000000000000000

0x210: 0x0000000000000000

[40759.276246] rcu: INFO: rcu_preempt detected stalls on CPUs/tasks:

[40759.282339] rcu: 7-...!: (411978 GPs behind) idle=32c/0/0x0 softirq=0/0 fqs=1

[40759.289643] (detected by 0, t=5255 jiffies, g=1646721, q=270)

[40759.295468] Task dump for CPU 7:

[40759.298688] octep_cp_agent R running task 0 812 1 0x00000080

[40759.305730] Call trace:

[40759.308174] __switch_to+0x11c/0x154

[40759.311744] rcu: rcu_preempt kthread starved for 5258 jiffies! g1646721 f0x0 RCU_GP_WAIT_FQS(5) ->state=0x402 ->cpu=1

[40759.322346] rcu: RCU grace-period kthread stack dump:

[40759.327389] rcu_preempt I 0 10 2 0x000000a8

[40759.332867] Call trace:

[40759.335305] __switch_to+0x11c/0x154

[40759.338875] __schedule+0x22c/0x650

[40759.342356] schedule+0x40/0xe0

[40759.345489] schedule_timeout+0x78/0xf0

[40759.349317] rcu_gp_kthread+0x4d8/0xa10

[40759.353146] kthread+0x15c/0x160

[40759.356366] ret_from_fork+0x10/0x18

[40780.656230] rcu: INFO: rcu_preempt detected stalls on CPUs/tasks:

[40780.662324] rcu: 1-...0: (1 GPs behind) idle=302/1/0x4000000000000000 softirq=629758/629761 fqs=2625

[40780.671625] (detected by 0, t=5255 jiffies, g=1646725, q=324)

[40780.677450] Task dump for CPU 1:

[40780.680672] dmidecode R running task 0 1247 1246 0x00000082

[40780.687715] Call trace:

[40780.690158] __switch_to+0x11c/0x154

[40780.693728] noop_backing_dev_info+0x0/0x438

Unhandled Exception in EL3.

x30 = 0x0000000000b99b84

x0 = 0x00000000304c25b0

x1 = 0x0000ffffa20a0040

x2 = 0x000000000000ff70

x3 = 0x00000000304c25b0

x4 = 0x0000ffffa20b0000

x5 = 0x00000000304d25b0

x6 = 0x0000000000000000

x7 = 0x0000000000000000

x8 = 0x0000000000000000

x9 = 0x0000000000000000

x10 = 0x0000000000000000

x11 = 0x0000000000000000

x12 = 0x0000000000000000

x13 = 0x0000000000000000

x14 = 0x0000000000000000

x15 = 0x0000000000000000

x16 = 0x0000000000426000

x17 = 0x0000ffffa2132dd0

x18 = 0x0000000000000010

x19 = 0x0000000000000003

x20 = 0x00000000304c25b0

x21 = 0x00000000000f0000

x22 = 0x0000000000010000

x23 = 0x000000000040d198

x24 = 0x0000000000000000

x25 = 0x0000ffffa20a0000

x26 = 0x0000000000010000

x27 = 0x0000000000000000

x28 = 0x0000000000000000

x29 = 0x0000ffffc93ac150

scr_el3 = 0x000000000403073d

sctlr_el3 = 0x0000000030cd183f

cptr_el3 = 0x0000000000000100

tcr_el3 = 0x0000000080853510

daif = 0x00000000000003c0

mair_el3 = 0x00000000004404ff

spsr_el3 = 0x00000000620002cd

elr_el3 = 0x0000000000b99d84

ttbr0_el3 = 0x0000000000c80001

esr_el3 = 0x00000000be000011

far_el3 = 0x3b8cb54bb6d8c910

spsr_el1 = 0x0000000000000000

elr_el1 = 0x0000000000000000

spsr_abt = 0x0000000000000000

spsr_und = 0x0000000000000000

spsr_irq = 0x0000000000000000

spsr_fiq = 0x0000000000000000

sctlr_el1 = 0x0000000030d00800

actlr_el1 = 0x0000000000000000

cpacr_el1 = 0x0000000000000000

csselr_el1 = 0x0000000000000000

sp_el1 = 0x0000000000000000

esr_el1 = 0x0000000000000000

ttbr0_el1 = 0x0000000000000000

ttbr1_el1 = 0x0000000000000000

mair_el1 = 0x0000000000000000

amair_el1 = 0x0000000000000000

cpupwrctlr_el1 = 0x0000000000000000

icc_ctlr = 0x00000000000a8410

icc_hppir0 = 0x000000000000001d

icc_hppir1 = 0x00000000000003ff

icc_rpr_el1 = 0x00000000000000ff

icc_ap0r0_el1 = 0x0000000000000000

gicd_ispendr regs (Offsets 0x200-0x210)

Offset Value

0x200: 0x0000000000000000

0x204: 0x0000000000800000

0x208: 0x0000000000000000

0x20c: 0x0000000000000000

0x210: 0x0000000000000000

SCP: SCP BL1 detected Core Domain reset

SCP: coresighSCP:

SCP: SCP BL1 is Alive!

SCP: 11.23.03.gbd75d75d gbd75d75d Sun, 12 Mar 2023 02:54:24 +0000

SCP: Detected chip ba, platform 0

SCP: Boot security state: new chip

SCP: RST_LBOOT=0x8: CHIP_SOFT

SCP: Previous RST_LBOOT=0x200002000: CORE_WDOG二、问题分析

我们来先看第一段:

Unhandled Exception in EL3.

x30 = 0x0000000000b99b84

x0 = 0x00000000179a25b0

x1 = 0x0000ffffb5b20040

x2 = 0x000000000000ff70

x3 = 0x00000000179a25b0

x4 = 0x0000ffffb5b30000

x5 = 0x00000000179b25b0

x6 = 0x0000000000000000

x7 = 0x0000000000000000

x8 = 0x0000000000000000

x9 = 0x0000000000000000

x10 = 0x0000000000000000

x11 = 0x0000000000000000

x12 = 0x0000000000000000

x13 = 0x0000000000000000

x14 = 0x0000000000000000

x15 = 0x0000000000000000

x16 = 0x0000000000426000

x17 = 0x0000ffffb5bb2dd0

x18 = 0x0000000000000010

x19 = 0x0000000000000003

x20 = 0x00000000179a25b0

x21 = 0x00000000000f0000

x22 = 0x0000000000010000

x23 = 0x000000000040d198

x24 = 0x0000000000000000

x25 = 0x0000ffffb5b20000

x26 = 0x0000000000010000

x27 = 0x0000000000000000

x28 = 0x0000000000000000

x29 = 0x0000fffffaf92680

scr_el3 = 0x000000000403073d

sctlr_el3 = 0x0000000030cd183f

cptr_el3 = 0x0000000000000100

tcr_el3 = 0x0000000080853510

daif = 0x00000000000003c0

mair_el3 = 0x00000000004404ff

spsr_el3 = 0x00000000620002cd

elr_el3 = 0x0000000000b99d84

ttbr0_el3 = 0x0000000000c80001

esr_el3 = 0x00000000be000011

far_el3 = 0x2abf2e72a2b2cff8

spsr_el1 = 0x0000000000000000

elr_el1 = 0x0000000000000000

spsr_abt = 0x0000000000000000

spsr_und = 0x0000000000000000

spsr_irq = 0x0000000000000000

spsr_fiq = 0x0000000000000000

sctlr_el1 = 0x0000000030d00800

actlr_el1 = 0x0000000000000000

cpacr_el1 = 0x0000000000000000

csselr_el1 = 0x0000000000000000

sp_el1 = 0x0000000000000000

esr_el1 = 0x0000000000000000

ttbr0_el1 = 0x0000000000000000

ttbr1_el1 = 0x0000000000000000

mair_el1 = 0x0000000000000000

amair_el1 = 0x0000000000000000

cpupwrctlr_el1 = 0x0000000000000000

icc_ctlr = 0x00000000000a8410

icc_hppir0 = 0x00000000000003fd

icc_hppir1 = 0x000000000000001a

icc_rpr_el1 = 0x00000000000000ff

icc_ap0r0_el1 = 0x0000000000000000

gicd_ispendr regs (Offsets 0x200-0x210)

Offset Value

0x200: 0x0000000000000000

0x204: 0x0000000000000000

0x208: 0x0000000000000000

0x20c: 0x0000000000000000

0x210: 0x0000000000000000这里主要将发生问题时的相关的寄存器 dump 出来,包括通用寄存器 x0 ~ x29,EL3/EL1 模式下的控制寄存器和状态寄存器以及 GIC 相关寄存器。

首先我们要了解 EL3 模式是系统里最高的运行模式,EL1 模式(linux 内核运行的模式)发生的严重异常会陷入到 EL3 模式中,这些异常包括内存非法访问、指令非法访问等。

2.1 ESR 寄存器分析

在生发问题时,EL3 的错误状态寄存器 ESR_EL3 会报告异常的类型等信息,这个寄存器也是异常症状诊断的寄存器,我们先看看这个寄存器的格式:

![]()

里面 EC(31:26) 域是错误代码, 这个案例里 esr_el3 为 0xbe000011,对应的值为 0b101111(0x2f),对应值解释为:

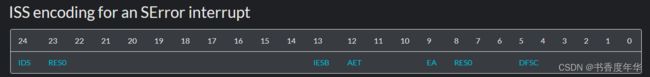

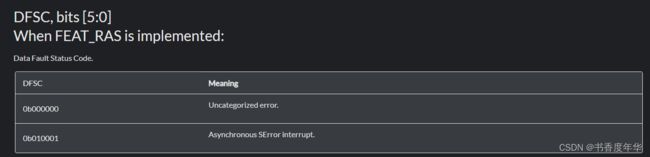

即发生了 SError,需要看 ISS 部分的编码来具体分析。SError 是系统错误的意思,通常是发生了异步异常,通常来自 external aborts。那我们继续看 ISS[24:0],我们这里 ISS 值为 0x11。

由上图不难发现,系统是发生了异步异常,异步通常是说异常同步在错误发生的同时抛出的,而是有一段延迟,比如在关闭中断情况下发生的 data abort,就会在开启中断后触发,表现为异步异常。所以,ESR_EL3 寄存器给我提供的信息就是这些。

由上图不难发现,系统是发生了异步异常,异步通常是说异常同步在错误发生的同时抛出的,而是有一段延迟,比如在关闭中断情况下发生的 data abort,就会在开启中断后触发,表现为异步异常。所以,ESR_EL3 寄存器给我提供的信息就是这些。

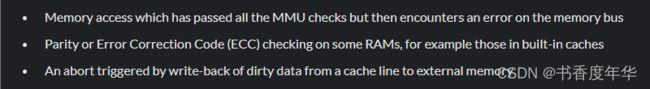

2.2 SError

通常有三种类型的 SError:

- 内存访问经过 MMU 检查,但是在内存总线上遇到了问题。可能是内存映射错误,访问了不存在的地址

- 内存或者 cache 的 ECC 校验失败,通常是硬件问题

- 将 cache 中的脏数据写回到外存中

2.3 错误返回地址

通过 elr_el3 = 0x0000000000b99d84 可以看出,EL1 发生问题的程序地址为 0x0000000000b99d84,我们也能看到不同 cpu dump 出来的信息是一致的,这个地址需要将 Linux 内核反汇编来查看在哪里。

2.4 错误访问地址

FAR_EL3 记录了发生同步异常时,访问的数据或者指令的虚拟地址。但是由于这里发生的是异步异常,所以没有参考价值

建议

1.再截取更早的错误日志

2.查找内核中关于内存映射部分的修改

参考 Arm Armv9-A Architecture Registers

AArch64 System Registers

ACCDATA_EL1: Accelerator Data

ACTLR_EL1: Auxiliary Control Register (EL1)

ACTLR_EL2: Auxiliary Control Register (EL2)

ACTLR_EL3: Auxiliary Control Register (EL3)

AFSR0_EL1: Auxiliary Fault Status Register 0 (EL1)

AFSR0_EL2: Auxiliary Fault Status Register 0 (EL2)

AFSR0_EL3: Auxiliary Fault Status Register 0 (EL3)

AFSR1_EL1: Auxiliary Fault Status Register 1 (EL1)

AFSR1_EL2: Auxiliary Fault Status Register 1 (EL2)

AFSR1_EL3: Auxiliary Fault Status Register 1 (EL3)

AIDR_EL1: Auxiliary ID Register

ALLINT: All Interrupt Mask Bit

AMAIR_EL1: Auxiliary Memory Attribute Indirection Register (EL1)

AMAIR_EL2: Auxiliary Memory Attribute Indirection Register (EL2)

AMAIR_EL3: Auxiliary Memory Attribute Indirection Register (EL3)

AMCFGR_EL0: Activity Monitors Configuration Register

AMCG1IDR_EL0: Activity Monitors Counter Group 1 Identification Register

AMCGCR_EL0: Activity Monitors Counter Group Configuration Register

AMCNTENCLR0_EL0: Activity Monitors Count Enable Clear Register 0

AMCNTENCLR1_EL0: Activity Monitors Count Enable Clear Register 1

AMCNTENSET0_EL0: Activity Monitors Count Enable Set Register 0

AMCNTENSET1_EL0: Activity Monitors Count Enable Set Register 1

AMCR_EL0: Activity Monitors Control Register

AMEVCNTR0

AMEVCNTR1

AMEVCNTVOFF0

AMEVCNTVOFF1

AMEVTYPER0

AMEVTYPER1

AMUSERENR_EL0: Activity Monitors User Enable Register

APDAKeyHi_EL1: Pointer Authentication Key A for Data (bits[127:64])

APDAKeyLo_EL1: Pointer Authentication Key A for Data (bits[63:0])

APDBKeyHi_EL1: Pointer Authentication Key B for Data (bits[127:64])

APDBKeyLo_EL1: Pointer Authentication Key B for Data (bits[63:0])

APGAKeyHi_EL1: Pointer Authentication Key A for Code (bits[127:64])

APGAKeyLo_EL1: Pointer Authentication Key A for Code (bits[63:0])

APIAKeyHi_EL1: Pointer Authentication Key A for Instruction (bits[127:64])

APIAKeyLo_EL1: Pointer Authentication Key A for Instruction (bits[63:0])

APIBKeyHi_EL1: Pointer Authentication Key B for Instruction (bits[127:64])

APIBKeyLo_EL1: Pointer Authentication Key B for Instruction (bits[63:0])

BRBCR_EL1: Branch Record Buffer Control Register (EL1)

BRBCR_EL2: Branch Record Buffer Control Register (EL2)

BRBFCR_EL1: Branch Record Buffer Function Control Register

BRBIDR0_EL1: Branch Record Buffer ID0 Register

BRBINF

BRBINFINJ_EL1: Branch Record Buffer Information Injection Register

BRBSRC

BRBSRCINJ_EL1: Branch Record Buffer Source Address Injection Register

BRBTGT

BRBTGTINJ_EL1: Branch Record Buffer Target Address Injection Register

BRBTS_EL1: Branch Record Buffer Timestamp Register

CCSIDR2_EL1: Current Cache Size ID Register 2

CCSIDR_EL1: Current Cache Size ID Register

CLIDR_EL1: Cache Level ID Register

CNTFRQ_EL0: Counter-timer Frequency register

CNTHCTL_EL2: Counter-timer Hypervisor Control register

CNTHPS_CTL_EL2: Counter-timer Secure Physical Timer Control register (EL2)

CNTHPS_CVAL_EL2: Counter-timer Secure Physical Timer CompareValue register (EL2)

CNTHPS_TVAL_EL2: Counter-timer Secure Physical Timer TimerValue register (EL2)

CNTHP_CTL_EL2: Counter-timer Hypervisor Physical Timer Control register

CNTHP_CVAL_EL2: Counter-timer Physical Timer CompareValue register (EL2)

CNTHP_TVAL_EL2: Counter-timer Physical Timer TimerValue register (EL2)

CNTHVS_CTL_EL2: Counter-timer Secure Virtual Timer Control register (EL2)

CNTHVS_CVAL_EL2: Counter-timer Secure Virtual Timer CompareValue register (EL2)

CNTHVS_TVAL_EL2: Counter-timer Secure Virtual Timer TimerValue register (EL2)

CNTHV_CTL_EL2: Counter-timer Virtual Timer Control register (EL2)

CNTHV_CVAL_EL2: Counter-timer Virtual Timer CompareValue register (EL2)

CNTHV_TVAL_EL2: Counter-timer Virtual Timer TimerValue Register (EL2)

CNTKCTL_EL1: Counter-timer Kernel Control register

CNTPCTSS_EL0: Counter-timer Self-Synchronized Physical Count register

CNTPCT_EL0: Counter-timer Physical Count register

CNTPOFF_EL2: Counter-timer Physical Offset register

CNTPS_CTL_EL1: Counter-timer Physical Secure Timer Control register

CNTPS_CVAL_EL1: Counter-timer Physical Secure Timer CompareValue register

CNTPS_TVAL_EL1: Counter-timer Physical Secure Timer TimerValue register

CNTP_CTL_EL0: Counter-timer Physical Timer Control register

CNTP_CVAL_EL0: Counter-timer Physical Timer CompareValue register

CNTP_TVAL_EL0: Counter-timer Physical Timer TimerValue register

CNTVCTSS_EL0: Counter-timer Self-Synchronized Virtual Count register

CNTVCT_EL0: Counter-timer Virtual Count register

CNTVOFF_EL2: Counter-timer Virtual Offset register

CNTV_CTL_EL0: Counter-timer Virtual Timer Control register

CNTV_CVAL_EL0: Counter-timer Virtual Timer CompareValue register

CNTV_TVAL_EL0: Counter-timer Virtual Timer TimerValue register

CONTEXTIDR_EL1: Context ID Register (EL1)

CONTEXTIDR_EL2: Context ID Register (EL2)

CPACR_EL1: Architectural Feature Access Control Register

CPTR_EL2: Architectural Feature Trap Register (EL2)

CPTR_EL3: Architectural Feature Trap Register (EL3)

CSSELR_EL1: Cache Size Selection Register

CTR_EL0: Cache Type Register

CurrentEL: Current Exception Level

DACR32_EL2: Domain Access Control Register

DAIF: Interrupt Mask Bits

DBGAUTHSTATUS_EL1: Debug Authentication Status register

DBGBCR

DBGBVR

DBGCLAIMCLR_EL1: Debug CLAIM Tag Clear register

DBGCLAIMSET_EL1: Debug CLAIM Tag Set register

DBGDTRRX_EL0: Debug Data Transfer Register, Receive

DBGDTRTX_EL0: Debug Data Transfer Register, Transmit

DBGDTR_EL0: Debug Data Transfer Register, half-duplex

DBGPRCR_EL1: Debug Power Control Register

DBGVCR32_EL2: Debug Vector Catch Register

DBGWCR

DBGWVR

DCZID_EL0: Data Cache Zero ID register

DISR_EL1: Deferred Interrupt Status Register

DIT: Data Independent Timing

DLR_EL0: Debug Link Register

DSPSR_EL0: Debug Saved Program Status Register

ELR_EL1: Exception Link Register (EL1)

ELR_EL2: Exception Link Register (EL2)

ELR_EL3: Exception Link Register (EL3)

ERRIDR_EL1: Error Record ID Register

ERRSELR_EL1: Error Record Select Register

ERXADDR_EL1: Selected Error Record Address Register

ERXCTLR_EL1: Selected Error Record Control Register

ERXFR_EL1: Selected Error Record Feature Register

ERXMISC0_EL1: Selected Error Record Miscellaneous Register 0

ERXMISC1_EL1: Selected Error Record Miscellaneous Register 1

ERXMISC2_EL1: Selected Error Record Miscellaneous Register 2

ERXMISC3_EL1: Selected Error Record Miscellaneous Register 3

ERXPFGCDN_EL1: Selected Pseudo-fault Generation Countdown register

ERXPFGCTL_EL1: Selected Pseudo-fault Generation Control register

ERXPFGF_EL1: Selected Pseudo-fault Generation Feature register

ERXSTATUS_EL1: Selected Error Record Primary Status Register

ESR_EL1: Exception Syndrome Register (EL1)

ESR_EL2: Exception Syndrome Register (EL2)

ESR_EL3: Exception Syndrome Register (EL3)

FAR_EL1: Fault Address Register (EL1)

FAR_EL2: Fault Address Register (EL2)

FAR_EL3: Fault Address Register (EL3)

FPCR: Floating-point Control Register

FPEXC32_EL2: Floating-Point Exception Control register

FPSR: Floating-point Status Register

GCR_EL1: Tag Control Register.

GMID_EL1: Multiple tag transfer ID register

GPCCR_EL3: Granule Protection Check Control Register (EL3)

GPTBR_EL3: Granule Protection Table Base Register

HACR_EL2: Hypervisor Auxiliary Control Register

HAFGRTR_EL2: Hypervisor Activity Monitors Fine-Grained Read Trap Register

HCRX_EL2: Extended Hypervisor Configuration Register

HCR_EL2: Hypervisor Configuration Register

HDFGRTR_EL2: Hypervisor Debug Fine-Grained Read Trap Register

HDFGWTR_EL2: Hypervisor Debug Fine-Grained Write Trap Register

HFGITR_EL2: Hypervisor Fine-Grained Instruction Trap Register

HFGRTR_EL2: Hypervisor Fine-Grained Read Trap Register

HFGWTR_EL2: Hypervisor Fine-Grained Write Trap Register

HPFAR_EL2: Hypervisor IPA Fault Address Register

HSTR_EL2: Hypervisor System Trap Register

ICC_AP0R

ICC_AP1R

ICC_ASGI1R_EL1: Interrupt Controller Alias Software Generated Interrupt Group 1 Register

ICC_BPR0_EL1: Interrupt Controller Binary Point Register 0

ICC_BPR1_EL1: Interrupt Controller Binary Point Register 1

ICC_CTLR_EL1: Interrupt Controller Control Register (EL1)

ICC_CTLR_EL3: Interrupt Controller Control Register (EL3)

ICC_DIR_EL1: Interrupt Controller Deactivate Interrupt Register

ICC_EOIR0_EL1: Interrupt Controller End Of Interrupt Register 0

ICC_EOIR1_EL1: Interrupt Controller End Of Interrupt Register 1

ICC_HPPIR0_EL1: Interrupt Controller Highest Priority Pending Interrupt Register 0

ICC_HPPIR1_EL1: Interrupt Controller Highest Priority Pending Interrupt Register 1

ICC_IAR0_EL1: Interrupt Controller Interrupt Acknowledge Register 0

ICC_IAR1_EL1: Interrupt Controller Interrupt Acknowledge Register 1

ICC_IGRPEN0_EL1: Interrupt Controller Interrupt Group 0 Enable register

ICC_IGRPEN1_EL1: Interrupt Controller Interrupt Group 1 Enable register

ICC_IGRPEN1_EL3: Interrupt Controller Interrupt Group 1 Enable register (EL3)

ICC_NMIAR1_EL1: Interrupt Controller Non-maskable Interrupt Acknowledge Register 1

ICC_PMR_EL1: Interrupt Controller Interrupt Priority Mask Register

ICC_RPR_EL1: Interrupt Controller Running Priority Register

ICC_SGI0R_EL1: Interrupt Controller Software Generated Interrupt Group 0 Register

ICC_SGI1R_EL1: Interrupt Controller Software Generated Interrupt Group 1 Register

ICC_SRE_EL1: Interrupt Controller System Register Enable register (EL1)

ICC_SRE_EL2: Interrupt Controller System Register Enable register (EL2)

ICC_SRE_EL3: Interrupt Controller System Register Enable register (EL3)

ICH_AP0R

ICH_AP1R

ICH_EISR_EL2: Interrupt Controller End of Interrupt Status Register

ICH_ELRSR_EL2: Interrupt Controller Empty List Register Status Register

ICH_HCR_EL2: Interrupt Controller Hyp Control Register

ICH_LR

ICH_MISR_EL2: Interrupt Controller Maintenance Interrupt State Register

ICH_VMCR_EL2: Interrupt Controller Virtual Machine Control Register

ICH_VTR_EL2: Interrupt Controller VGIC Type Register

ICV_AP0R

ICV_AP1R

ICV_BPR0_EL1: Interrupt Controller Virtual Binary Point Register 0

ICV_BPR1_EL1: Interrupt Controller Virtual Binary Point Register 1

ICV_CTLR_EL1: Interrupt Controller Virtual Control Register

ICV_DIR_EL1: Interrupt Controller Deactivate Virtual Interrupt Register

ICV_EOIR0_EL1: Interrupt Controller Virtual End Of Interrupt Register 0

ICV_EOIR1_EL1: Interrupt Controller Virtual End Of Interrupt Register 1

ICV_HPPIR0_EL1: Interrupt Controller Virtual Highest Priority Pending Interrupt Register 0

ICV_HPPIR1_EL1: Interrupt Controller Virtual Highest Priority Pending Interrupt Register 1

ICV_IAR0_EL1: Interrupt Controller Virtual Interrupt Acknowledge Register 0

ICV_IAR1_EL1: Interrupt Controller Virtual Interrupt Acknowledge Register 1

ICV_IGRPEN0_EL1: Interrupt Controller Virtual Interrupt Group 0 Enable register

ICV_IGRPEN1_EL1: Interrupt Controller Virtual Interrupt Group 1 Enable register

ICV_NMIAR1_EL1: Interrupt Controller Virtual Non-maskable Interrupt Acknowledge Register 1

ICV_PMR_EL1: Interrupt Controller Virtual Interrupt Priority Mask Register

ICV_RPR_EL1: Interrupt Controller Virtual Running Priority Register

ID_AA64AFR0_EL1: AArch64 Auxiliary Feature Register 0

ID_AA64AFR1_EL1: AArch64 Auxiliary Feature Register 1

ID_AA64DFR0_EL1: AArch64 Debug Feature Register 0

ID_AA64DFR1_EL1: AArch64 Debug Feature Register 1

ID_AA64ISAR0_EL1: AArch64 Instruction Set Attribute Register 0

ID_AA64ISAR1_EL1: AArch64 Instruction Set Attribute Register 1

ID_AA64ISAR2_EL1: AArch64 Instruction Set Attribute Register 2

ID_AA64MMFR0_EL1: AArch64 Memory Model Feature Register 0

ID_AA64MMFR1_EL1: AArch64 Memory Model Feature Register 1

ID_AA64MMFR2_EL1: AArch64 Memory Model Feature Register 2

ID_AA64PFR0_EL1: AArch64 Processor Feature Register 0

ID_AA64PFR1_EL1: AArch64 Processor Feature Register 1

ID_AA64SMFR0_EL1: SME Feature ID register 0

ID_AA64ZFR0_EL1: SVE Feature ID register 0

ID_AFR0_EL1: AArch32 Auxiliary Feature Register 0

ID_DFR0_EL1: AArch32 Debug Feature Register 0

ID_DFR1_EL1: Debug Feature Register 1

ID_ISAR0_EL1: AArch32 Instruction Set Attribute Register 0

ID_ISAR1_EL1: AArch32 Instruction Set Attribute Register 1

ID_ISAR2_EL1: AArch32 Instruction Set Attribute Register 2

ID_ISAR3_EL1: AArch32 Instruction Set Attribute Register 3

ID_ISAR4_EL1: AArch32 Instruction Set Attribute Register 4

ID_ISAR5_EL1: AArch32 Instruction Set Attribute Register 5

ID_ISAR6_EL1: AArch32 Instruction Set Attribute Register 6

ID_MMFR0_EL1: AArch32 Memory Model Feature Register 0

ID_MMFR1_EL1: AArch32 Memory Model Feature Register 1

ID_MMFR2_EL1: AArch32 Memory Model Feature Register 2

ID_MMFR3_EL1: AArch32 Memory Model Feature Register 3

ID_MMFR4_EL1: AArch32 Memory Model Feature Register 4

ID_MMFR5_EL1: AArch32 Memory Model Feature Register 5

ID_PFR0_EL1: AArch32 Processor Feature Register 0

ID_PFR1_EL1: AArch32 Processor Feature Register 1

ID_PFR2_EL1: AArch32 Processor Feature Register 2

IFSR32_EL2: Instruction Fault Status Register (EL2)

ISR_EL1: Interrupt Status Register

LORC_EL1: LORegion Control (EL1)

LOREA_EL1: LORegion End Address (EL1)

LORID_EL1: LORegionID (EL1)

LORN_EL1: LORegion Number (EL1)

LORSA_EL1: LORegion Start Address (EL1)

MAIR_EL1: Memory Attribute Indirection Register (EL1)

MAIR_EL2: Memory Attribute Indirection Register (EL2)

MAIR_EL3: Memory Attribute Indirection Register (EL3)

MDCCINT_EL1: Monitor DCC Interrupt Enable Register

MDCCSR_EL0: Monitor DCC Status Register

MDCR_EL2: Monitor Debug Configuration Register (EL2)

MDCR_EL3: Monitor Debug Configuration Register (EL3)

MDRAR_EL1: Monitor Debug ROM Address Register

MDSCR_EL1: Monitor Debug System Control Register

MFAR_EL3: PA Fault Address Register

MIDR_EL1: Main ID Register

MPAM0_EL1: MPAM0 Register (EL1)

MPAM1_EL1: MPAM1 Register (EL1)

MPAM2_EL2: MPAM2 Register (EL2)

MPAM3_EL3: MPAM3 Register (EL3)

MPAMHCR_EL2: MPAM Hypervisor Control Register (EL2)

MPAMIDR_EL1: MPAM ID Register (EL1)

MPAMSM_EL1: MPAM Streaming Mode Register

MPAMVPM0_EL2: MPAM Virtual PARTID Mapping Register 0

MPAMVPM1_EL2: MPAM Virtual PARTID Mapping Register 1

MPAMVPM2_EL2: MPAM Virtual PARTID Mapping Register 2

MPAMVPM3_EL2: MPAM Virtual PARTID Mapping Register 3

MPAMVPM4_EL2: MPAM Virtual PARTID Mapping Register 4

MPAMVPM5_EL2: MPAM Virtual PARTID Mapping Register 5

MPAMVPM6_EL2: MPAM Virtual PARTID Mapping Register 6

MPAMVPM7_EL2: MPAM Virtual PARTID Mapping Register 7

MPAMVPMV_EL2: MPAM Virtual Partition Mapping Valid Register

MPIDR_EL1: Multiprocessor Affinity Register

MVFR0_EL1: AArch32 Media and VFP Feature Register 0

MVFR1_EL1: AArch32 Media and VFP Feature Register 1

MVFR2_EL1: AArch32 Media and VFP Feature Register 2

NZCV: Condition Flags

OSDLR_EL1: OS Double Lock Register

OSDTRRX_EL1: OS Lock Data Transfer Register, Receive

OSDTRTX_EL1: OS Lock Data Transfer Register, Transmit

OSECCR_EL1: OS Lock Exception Catch Control Register

OSLAR_EL1: OS Lock Access Register

OSLSR_EL1: OS Lock Status Register

PAN: Privileged Access Never

PAR_EL1: Physical Address Register

PMBIDR_EL1: Profiling Buffer ID Register

PMBLIMITR_EL1: Profiling Buffer Limit Address Register

PMBPTR_EL1: Profiling Buffer Write Pointer Register

PMBSR_EL1: Profiling Buffer Status/syndrome Register

PMCCFILTR_EL0: Performance Monitors Cycle Count Filter Register

PMCCNTR_EL0: Performance Monitors Cycle Count Register

PMCEID0_EL0: Performance Monitors Common Event Identification register 0

PMCEID1_EL0: Performance Monitors Common Event Identification register 1

PMCNTENCLR_EL0: Performance Monitors Count Enable Clear register

PMCNTENSET_EL0: Performance Monitors Count Enable Set register

PMCR_EL0: Performance Monitors Control Register

PMEVCNTR

PMEVTYPER

PMINTENCLR_EL1: Performance Monitors Interrupt Enable Clear register

PMINTENSET_EL1: Performance Monitors Interrupt Enable Set register

PMMIR_EL1: Performance Monitors Machine Identification Register

PMOVSCLR_EL0: Performance Monitors Overflow Flag Status Clear Register

PMOVSSET_EL0: Performance Monitors Overflow Flag Status Set register

PMSCR_EL1: Statistical Profiling Control Register (EL1)

PMSCR_EL2: Statistical Profiling Control Register (EL2)

PMSELR_EL0: Performance Monitors Event Counter Selection Register

PMSEVFR_EL1: Sampling Event Filter Register

PMSFCR_EL1: Sampling Filter Control Register

PMSICR_EL1: Sampling Interval Counter Register

PMSIDR_EL1: Sampling Profiling ID Register

PMSIRR_EL1: Sampling Interval Reload Register

PMSLATFR_EL1: Sampling Latency Filter Register

PMSNEVFR_EL1: Sampling Inverted Event Filter Register

PMSWINC_EL0: Performance Monitors Software Increment register

PMUSERENR_EL0: Performance Monitors User Enable Register

PMXEVCNTR_EL0: Performance Monitors Selected Event Count Register

PMXEVTYPER_EL0: Performance Monitors Selected Event Type Register

REVIDR_EL1: Revision ID Register

RGSR_EL1: Random Allocation Tag Seed Register.

RMR_EL1: Reset Management Register (EL1)

RMR_EL2: Reset Management Register (EL2)

RMR_EL3: Reset Management Register (EL3)

RNDR: Random Number

RNDRRS: Reseeded Random Number

RVBAR_EL1: Reset Vector Base Address Register (if EL2 and EL3 not implemented)

RVBAR_EL2: Reset Vector Base Address Register (if EL3 not implemented)

RVBAR_EL3: Reset Vector Base Address Register (if EL3 implemented)

S3_

SCR_EL3: Secure Configuration Register

SCTLR_EL1: System Control Register (EL1)

SCTLR_EL2: System Control Register (EL2)

SCTLR_EL3: System Control Register (EL3)

SCXTNUM_EL0: EL0 Read/Write Software Context Number

SCXTNUM_EL1: EL1 Read/Write Software Context Number

SCXTNUM_EL2: EL2 Read/Write Software Context Number

SCXTNUM_EL3: EL3 Read/Write Software Context Number

SDER32_EL2: AArch32 Secure Debug Enable Register

SDER32_EL3: AArch32 Secure Debug Enable Register

SMCR_EL1: SME Control Register (EL1)

SMCR_EL2: SME Control Register (EL2)

SMCR_EL3: SME Control Register (EL3)

SMIDR_EL1: Streaming Mode Identification Register

SMPRIMAP_EL2: Streaming Mode Priority Mapping Register

SMPRI_EL1: Streaming Mode Priority Register

SPSel: Stack Pointer Select

SPSR_abt: Saved Program Status Register (Abort mode)

SPSR_EL1: Saved Program Status Register (EL1)

SPSR_EL2: Saved Program Status Register (EL2)

SPSR_EL3: Saved Program Status Register (EL3)

SPSR_fiq: Saved Program Status Register (FIQ mode)

SPSR_irq: Saved Program Status Register (IRQ mode)

SPSR_und: Saved Program Status Register (Undefined mode)

SP_EL0: Stack Pointer (EL0)

SP_EL1: Stack Pointer (EL1)

SP_EL2: Stack Pointer (EL2)

SP_EL3: Stack Pointer (EL3)

SSBS: Speculative Store Bypass Safe

SVCR: Streaming Vector Control Register

TCO: Tag Check Override

TCR_EL1: Translation Control Register (EL1)

TCR_EL2: Translation Control Register (EL2)

TCR_EL3: Translation Control Register (EL3)

TFSRE0_EL1: Tag Fault Status Register (EL0).

TFSR_EL1: Tag Fault Status Register (EL1)

TFSR_EL2: Tag Fault Status Register (EL2)

TFSR_EL3: Tag Fault Status Register (EL3)

TPIDR2_EL0: EL0 Read/Write Software Thread ID Register 2

TPIDRRO_EL0: EL0 Read-Only Software Thread ID Register

TPIDR_EL0: EL0 Read/Write Software Thread ID Register

TPIDR_EL1: EL1 Software Thread ID Register

TPIDR_EL2: EL2 Software Thread ID Register

TPIDR_EL3: EL3 Software Thread ID Register

TRBBASER_EL1: Trace Buffer Base Address Register

TRBIDR_EL1: Trace Buffer ID Register

TRBLIMITR_EL1: Trace Buffer Limit Address Register

TRBMAR_EL1: Trace Buffer Memory Attribute Register

TRBPTR_EL1: Trace Buffer Write Pointer Register

TRBSR_EL1: Trace Buffer Status/syndrome Register

TRBTRG_EL1: Trace Buffer Trigger Counter Register

TRCACATR

TRCACVR

TRCAUTHSTATUS: Authentication Status Register

TRCAUXCTLR: Auxiliary Control Register

TRCBBCTLR: Branch Broadcast Control Register

TRCCCCTLR: Cycle Count Control Register

TRCCIDCCTLR0: Context Identifier Comparator Control Register 0

TRCCIDCCTLR1: Context Identifier Comparator Control Register 1

TRCCIDCVR

TRCCLAIMCLR: Claim Tag Clear Register

TRCCLAIMSET: Claim Tag Set Register

TRCCNTCTLR

TRCCNTRLDVR

TRCCNTVR

TRCCONFIGR: Trace Configuration Register

TRCDEVARCH: Device Architecture Register

TRCDEVID: Device Configuration Register

TRCEVENTCTL0R: Event Control 0 Register

TRCEVENTCTL1R: Event Control 1 Register

TRCEXTINSELR

TRCIDR0: ID Register 0

TRCIDR1: ID Register 1

TRCIDR10: ID Register 10

TRCIDR11: ID Register 11

TRCIDR12: ID Register 12

TRCIDR13: ID Register 13

TRCIDR2: ID Register 2

TRCIDR3: ID Register 3

TRCIDR4: ID Register 4

TRCIDR5: ID Register 5

TRCIDR6: ID Register 6

TRCIDR7: ID Register 7

TRCIDR8: ID Register 8

TRCIDR9: ID Register 9

TRCIMSPEC0: IMP DEF Register 0

TRCIMSPEC

TRCOSLSR: Trace OS Lock Status Register

TRCPRGCTLR: Programming Control Register

TRCQCTLR: Q Element Control Register

TRCRSCTLR

TRCRSR: Resources Status Register

TRCSEQEVR

TRCSEQRSTEVR: Sequencer Reset Control Register

TRCSEQSTR: Sequencer State Register

TRCSSCCR

TRCSSCSR

TRCSSPCICR

TRCSTALLCTLR: Stall Control Register

TRCSTATR: Trace Status Register

TRCSYNCPR: Synchronization Period Register

TRCTRACEIDR: Trace ID Register

TRCTSCTLR: Timestamp Control Register

TRCVICTLR: ViewInst Main Control Register

TRCVIIECTLR: ViewInst Include/Exclude Control Register

TRCVIPCSSCTLR: ViewInst Start/Stop PE Comparator Control Register

TRCVISSCTLR: ViewInst Start/Stop Control Register

TRCVMIDCCTLR0: Virtual Context Identifier Comparator Control Register 0

TRCVMIDCCTLR1: Virtual Context Identifier Comparator Control Register 1

TRCVMIDCVR

TRFCR_EL1: Trace Filter Control Register (EL1)

TRFCR_EL2: Trace Filter Control Register (EL2)

TTBR0_EL1: Translation Table Base Register 0 (EL1)

TTBR0_EL2: Translation Table Base Register 0 (EL2)

TTBR0_EL3: Translation Table Base Register 0 (EL3)

TTBR1_EL1: Translation Table Base Register 1 (EL1)

TTBR1_EL2: Translation Table Base Register 1 (EL2)

UAO: User Access Override

VBAR_EL1: Vector Base Address Register (EL1)

VBAR_EL2: Vector Base Address Register (EL2)

VBAR_EL3: Vector Base Address Register (EL3)

VDISR_EL2: Virtual Deferred Interrupt Status Register

VMPIDR_EL2: Virtualization Multiprocessor ID Register

VNCR_EL2: Virtual Nested Control Register

VPIDR_EL2: Virtualization Processor ID Register

VSESR_EL2: Virtual SError Exception Syndrome Register

VSTCR_EL2: Virtualization Secure Translation Control Register

VSTTBR_EL2: Virtualization Secure Translation Table Base Register

VTCR_EL2: Virtualization Translation Control Register

VTTBR_EL2: Virtualization Translation Table Base Register

ZCR_EL1: SVE Control Register (EL1)

ZCR_EL2: SVE Control Register (EL2)

ZCR_EL3: SVE Control Register (EL3)

AArch32 System Registers

ACTLR: Auxiliary Control Register

ACTLR2: Auxiliary Control Register 2

ADFSR: Auxiliary Data Fault Status Register

AIDR: Auxiliary ID Register

AIFSR: Auxiliary Instruction Fault Status Register

AMAIR0: Auxiliary Memory Attribute Indirection Register 0

AMAIR1: Auxiliary Memory Attribute Indirection Register 1

AMCFGR: Activity Monitors Configuration Register

AMCGCR: Activity Monitors Counter Group Configuration Register

AMCNTENCLR0: Activity Monitors Count Enable Clear Register 0

AMCNTENCLR1: Activity Monitors Count Enable Clear Register 1

AMCNTENSET0: Activity Monitors Count Enable Set Register 0

AMCNTENSET1: Activity Monitors Count Enable Set Register 1

AMCR: Activity Monitors Control Register

AMEVCNTR0

AMEVCNTR1

AMEVTYPER0

AMEVTYPER1

AMUSERENR: Activity Monitors User Enable Register

APSR: Application Program Status Register

CCSIDR: Current Cache Size ID Register

CCSIDR2: Current Cache Size ID Register 2

CLIDR: Cache Level ID Register

CNTFRQ: Counter-timer Frequency register

CNTHCTL: Counter-timer Hyp Control register

CNTHPS_CTL: Counter-timer Secure Physical Timer Control Register (EL2)

CNTHPS_CVAL: Counter-timer Secure Physical Timer CompareValue Register (EL2)

CNTHPS_TVAL: Counter-timer Secure Physical Timer TimerValue Register (EL2)

CNTHP_CTL: Counter-timer Hyp Physical Timer Control register

CNTHP_CVAL: Counter-timer Hyp Physical CompareValue register

CNTHP_TVAL: Counter-timer Hyp Physical Timer TimerValue register

CNTHVS_CTL: Counter-timer Secure Virtual Timer Control Register (EL2)

CNTHVS_CVAL: Counter-timer Secure Virtual Timer CompareValue Register (EL2)

CNTHVS_TVAL: Counter-timer Secure Virtual Timer TimerValue Register (EL2)

CNTHV_CTL: Counter-timer Virtual Timer Control register (EL2)

CNTHV_CVAL: Counter-timer Virtual Timer CompareValue register (EL2)

CNTHV_TVAL: Counter-timer Virtual Timer TimerValue register (EL2)

CNTKCTL: Counter-timer Kernel Control register

CNTPCT: Counter-timer Physical Count register

CNTPCTSS: Counter-timer Self-Synchronized Physical Count register

CNTP_CTL: Counter-timer Physical Timer Control register

CNTP_CVAL: Counter-timer Physical Timer CompareValue register

CNTP_TVAL: Counter-timer Physical Timer TimerValue register

CNTVCT: Counter-timer Virtual Count register

CNTVCTSS: Counter-timer Self-Synchronized Virtual Count register

CNTVOFF: Counter-timer Virtual Offset register

CNTV_CTL: Counter-timer Virtual Timer Control register

CNTV_CVAL: Counter-timer Virtual Timer CompareValue register

CNTV_TVAL: Counter-timer Virtual Timer TimerValue register

CONTEXTIDR: Context ID Register

CPACR: Architectural Feature Access Control Register

CPSR: Current Program Status Register

CSSELR: Cache Size Selection Register

CTR: Cache Type Register

DACR: Domain Access Control Register

DBGAUTHSTATUS: Debug Authentication Status register

DBGBCR

DBGBVR

DBGBXVR

DBGCLAIMCLR: Debug CLAIM Tag Clear register

DBGCLAIMSET: Debug CLAIM Tag Set register

DBGDCCINT: DCC Interrupt Enable Register

DBGDEVID: Debug Device ID register 0

DBGDEVID1: Debug Device ID register 1

DBGDEVID2: Debug Device ID register 2

DBGDIDR: Debug ID Register

DBGDRAR: Debug ROM Address Register

DBGDSAR: Debug Self Address Register

DBGDSCRext: Debug Status and Control Register, External View

DBGDSCRint: Debug Status and Control Register, Internal View

DBGDTRRXext: Debug OS Lock Data Transfer Register, Receive, External View

DBGDTRRXint: Debug Data Transfer Register, Receive

DBGDTRTXext: Debug OS Lock Data Transfer Register, Transmit

DBGDTRTXint: Debug Data Transfer Register, Transmit

DBGOSDLR: Debug OS Double Lock Register

DBGOSECCR: Debug OS Lock Exception Catch Control Register

DBGOSLAR: Debug OS Lock Access Register

DBGOSLSR: Debug OS Lock Status Register

DBGPRCR: Debug Power Control Register

DBGVCR: Debug Vector Catch Register

DBGWCR

DBGWFAR: Debug Watchpoint Fault Address Register

DBGWVR

DFAR: Data Fault Address Register

DFSR: Data Fault Status Register

DISR: Deferred Interrupt Status Register

DLR: Debug Link Register

DSPSR: Debug Saved Program Status Register

ELR_hyp: Exception Link Register (Hyp mode)

ERRIDR: Error Record ID Register

ERRSELR: Error Record Select Register

ERXADDR: Selected Error Record Address Register

ERXADDR2: Selected Error Record Address Register 2

ERXCTLR: Selected Error Record Control Register

ERXCTLR2: Selected Error Record Control Register 2

ERXFR: Selected Error Record Feature Register

ERXFR2: Selected Error Record Feature Register 2

ERXMISC0: Selected Error Record Miscellaneous Register 0

ERXMISC1: Selected Error Record Miscellaneous Register 1

ERXMISC2: Selected Error Record Miscellaneous Register 2

ERXMISC3: Selected Error Record Miscellaneous Register 3

ERXMISC4: Selected Error Record Miscellaneous Register 4

ERXMISC5: Selected Error Record Miscellaneous Register 5

ERXMISC6: Selected Error Record Miscellaneous Register 6

ERXMISC7: Selected Error Record Miscellaneous Register 7

ERXSTATUS: Selected Error Record Primary Status Register

FCSEIDR: FCSE Process ID register

FPEXC: Floating-Point Exception Control register

FPSCR: Floating-Point Status and Control Register

FPSID: Floating-Point System ID register

HACR: Hyp Auxiliary Configuration Register

HACTLR: Hyp Auxiliary Control Register

HACTLR2: Hyp Auxiliary Control Register 2

HADFSR: Hyp Auxiliary Data Fault Status Register

HAIFSR: Hyp Auxiliary Instruction Fault Status Register

HAMAIR0: Hyp Auxiliary Memory Attribute Indirection Register 0

HAMAIR1: Hyp Auxiliary Memory Attribute Indirection Register 1

HCPTR: Hyp Architectural Feature Trap Register

HCR: Hyp Configuration Register

HCR2: Hyp Configuration Register 2

HDCR: Hyp Debug Control Register

HDFAR: Hyp Data Fault Address Register

HIFAR: Hyp Instruction Fault Address Register

HMAIR0: Hyp Memory Attribute Indirection Register 0

HMAIR1: Hyp Memory Attribute Indirection Register 1

HPFAR: Hyp IPA Fault Address Register

HRMR: Hyp Reset Management Register

HSCTLR: Hyp System Control Register

HSR: Hyp Syndrome Register

HSTR: Hyp System Trap Register

HTCR: Hyp Translation Control Register

HTPIDR: Hyp Software Thread ID Register

HTRFCR: Hyp Trace Filter Control Register

HTTBR: Hyp Translation Table Base Register

HVBAR: Hyp Vector Base Address Register

ICC_AP0R

ICC_AP1R

ICC_ASGI1R: Interrupt Controller Alias Software Generated Interrupt Group 1 Register

ICC_BPR0: Interrupt Controller Binary Point Register 0

ICC_BPR1: Interrupt Controller Binary Point Register 1

ICC_CTLR: Interrupt Controller Control Register

ICC_DIR: Interrupt Controller Deactivate Interrupt Register

ICC_EOIR0: Interrupt Controller End Of Interrupt Register 0

ICC_EOIR1: Interrupt Controller End Of Interrupt Register 1

ICC_HPPIR0: Interrupt Controller Highest Priority Pending Interrupt Register 0

ICC_HPPIR1: Interrupt Controller Highest Priority Pending Interrupt Register 1

ICC_HSRE: Interrupt Controller Hyp System Register Enable register

ICC_IAR0: Interrupt Controller Interrupt Acknowledge Register 0

ICC_IAR1: Interrupt Controller Interrupt Acknowledge Register 1

ICC_IGRPEN0: Interrupt Controller Interrupt Group 0 Enable register

ICC_IGRPEN1: Interrupt Controller Interrupt Group 1 Enable register

ICC_MCTLR: Interrupt Controller Monitor Control Register

ICC_MGRPEN1: Interrupt Controller Monitor Interrupt Group 1 Enable register

ICC_MSRE: Interrupt Controller Monitor System Register Enable register

ICC_PMR: Interrupt Controller Interrupt Priority Mask Register

ICC_RPR: Interrupt Controller Running Priority Register

ICC_SGI0R: Interrupt Controller Software Generated Interrupt Group 0 Register

ICC_SGI1R: Interrupt Controller Software Generated Interrupt Group 1 Register

ICC_SRE: Interrupt Controller System Register Enable register

ICH_AP0R

ICH_AP1R

ICH_EISR: Interrupt Controller End of Interrupt Status Register

ICH_ELRSR: Interrupt Controller Empty List Register Status Register

ICH_HCR: Interrupt Controller Hyp Control Register

ICH_LR

ICH_LRC

ICH_MISR: Interrupt Controller Maintenance Interrupt State Register

ICH_VMCR: Interrupt Controller Virtual Machine Control Register

ICH_VTR: Interrupt Controller VGIC Type Register

ICV_AP0R

ICV_AP1R

ICV_BPR0: Interrupt Controller Virtual Binary Point Register 0

ICV_BPR1: Interrupt Controller Virtual Binary Point Register 1

ICV_CTLR: Interrupt Controller Virtual Control Register

ICV_DIR: Interrupt Controller Deactivate Virtual Interrupt Register

ICV_EOIR0: Interrupt Controller Virtual End Of Interrupt Register 0

ICV_EOIR1: Interrupt Controller Virtual End Of Interrupt Register 1

ICV_HPPIR0: Interrupt Controller Virtual Highest Priority Pending Interrupt Register 0

ICV_HPPIR1: Interrupt Controller Virtual Highest Priority Pending Interrupt Register 1

ICV_IAR0: Interrupt Controller Virtual Interrupt Acknowledge Register 0

ICV_IAR1: Interrupt Controller Virtual Interrupt Acknowledge Register 1

ICV_IGRPEN0: Interrupt Controller Virtual Interrupt Group 0 Enable register

ICV_IGRPEN1: Interrupt Controller Virtual Interrupt Group 1 Enable register

ICV_PMR: Interrupt Controller Virtual Interrupt Priority Mask Register

ICV_RPR: Interrupt Controller Virtual Running Priority Register

ID_AFR0: Auxiliary Feature Register 0

ID_DFR0: Debug Feature Register 0

ID_DFR1: Debug Feature Register 1

ID_ISAR0: Instruction Set Attribute Register 0

ID_ISAR1: Instruction Set Attribute Register 1

ID_ISAR2: Instruction Set Attribute Register 2

ID_ISAR3: Instruction Set Attribute Register 3

ID_ISAR4: Instruction Set Attribute Register 4

ID_ISAR5: Instruction Set Attribute Register 5

ID_ISAR6: Instruction Set Attribute Register 6

ID_MMFR0: Memory Model Feature Register 0

ID_MMFR1: Memory Model Feature Register 1

ID_MMFR2: Memory Model Feature Register 2

ID_MMFR3: Memory Model Feature Register 3

ID_MMFR4: Memory Model Feature Register 4

ID_MMFR5: Memory Model Feature Register 5

ID_PFR0: Processor Feature Register 0

ID_PFR1: Processor Feature Register 1

ID_PFR2: Processor Feature Register 2

IFAR: Instruction Fault Address Register

IFSR: Instruction Fault Status Register

ISR: Interrupt Status Register

JIDR: Jazelle ID Register

JMCR: Jazelle Main Configuration Register

JOSCR: Jazelle OS Control Register

MAIR0: Memory Attribute Indirection Register 0

MAIR1: Memory Attribute Indirection Register 1

MIDR: Main ID Register

MPIDR: Multiprocessor Affinity Register

MVBAR: Monitor Vector Base Address Register

MVFR0: Media and VFP Feature Register 0

MVFR1: Media and VFP Feature Register 1

MVFR2: Media and VFP Feature Register 2

NMRR: Normal Memory Remap Register

NSACR: Non-Secure Access Control Register

PAR: Physical Address Register

PMCCFILTR: Performance Monitors Cycle Count Filter Register

PMCCNTR: Performance Monitors Cycle Count Register

PMCEID0: Performance Monitors Common Event Identification register 0

PMCEID1: Performance Monitors Common Event Identification register 1

PMCEID2: Performance Monitors Common Event Identification register 2

PMCEID3: Performance Monitors Common Event Identification register 3

PMCNTENCLR: Performance Monitors Count Enable Clear register

PMCNTENSET: Performance Monitors Count Enable Set register

PMCR: Performance Monitors Control Register

PMEVCNTR

PMEVTYPER

PMINTENCLR: Performance Monitors Interrupt Enable Clear register

PMINTENSET: Performance Monitors Interrupt Enable Set register

PMMIR: Performance Monitors Machine Identification Register

PMOVSR: Performance Monitors Overflow Flag Status Register

PMOVSSET: Performance Monitors Overflow Flag Status Set register

PMSELR: Performance Monitors Event Counter Selection Register

PMSWINC: Performance Monitors Software Increment register

PMUSERENR: Performance Monitors User Enable Register

PMXEVCNTR: Performance Monitors Selected Event Count Register

PMXEVTYPER: Performance Monitors Selected Event Type Register

PRRR: Primary Region Remap Register

REVIDR: Revision ID Register

RMR: Reset Management Register

RVBAR: Reset Vector Base Address Register

SCR: Secure Configuration Register

SCTLR: System Control Register

SDCR: Secure Debug Control Register

SDER: Secure Debug Enable Register

SPSR: Saved Program Status Register

SPSR_abt: Saved Program Status Register (Abort mode)

SPSR_fiq: Saved Program Status Register (FIQ mode)

SPSR_hyp: Saved Program Status Register (Hyp mode)

SPSR_irq: Saved Program Status Register (IRQ mode)

SPSR_mon: Saved Program Status Register (Monitor mode)

SPSR_svc: Saved Program Status Register (Supervisor mode)

SPSR_und: Saved Program Status Register (Undefined mode)

TCMTR: TCM Type Register

TLBTR: TLB Type Register

TPIDRPRW: PL1 Software Thread ID Register

TPIDRURO: PL0 Read-Only Software Thread ID Register

TPIDRURW: PL0 Read/Write Software Thread ID Register

TRFCR: Trace Filter Control Register

TTBCR: Translation Table Base Control Register

TTBCR2: Translation Table Base Control Register 2

TTBR0: Translation Table Base Register 0

TTBR1: Translation Table Base Register 1

VBAR: Vector Base Address Register

VDFSR: Virtual SError Exception Syndrome Register

VDISR: Virtual Deferred Interrupt Status Register

VMPIDR: Virtualization Multiprocessor ID Register

VPIDR: Virtualization Processor ID Register

VTCR: Virtualization Translation Control Register

VTTBR: Virtualization Translation Table Base Register