AMBA总线协议APB、AHB——学习笔记

文章目录

- 前言

- 一、总线介绍

-

- 1、基本概念

- 2、典型AMBA系统

- 二、APB3(Advanced Peripheral Bus)

-

- 1、定义

- 2、信号

- 3、版本信息

- 4、信号传输时序图

-

- 4.1 状态机

- 4.2 写操作

- 4.3 读操作

- 4.4 错误传输

- 5、PSTRB、PPROT信号

- 6、APB组成

- 三、AHB(Advanced High-performance Bus)

-

- 1、定义

- 2、信号

-

- 2.1 master端信号

- 2.2 slave端信号

- 2.3 AHB2版本的arbiter信号

- 2.4 默认值

- 3、版本信息

- 4、信号传输时序图

-

- 4.1 basic transfer

- 4.2 busy transfer

- 4.3 burst transfer

- 4.4 等待传输——hready为低修改地址和trans的情况

-

- 4.4.1 IDLE传输——改了地址和trans

- 4.4.2 BUSY传输固定长度burst——只改变了trans

- 4.4.3 BUSY传输未定义长度INCR——改变了地址和trans

- 4.4.3 ERROR响应之后——改变了地址和trans

- 四、总线对比

-

- 4.1 hready和hreadyout信号区别

- 4.2 APB2、APB3、APB4协议区别

- 4.3 AHB2、AHB-Lite、AHB5协议对比

- 五、面试问答题

-

- 1、主设备可以在hready为1的时候改变地址和控制信号吗

- 2、AHB主设备可以直接连到AHB从设备吗?

- 3、在AHB系统中可以支持多少个主设备?

- 4、主设备在扩展的传输中可以改变HADDR吗?

- 5、对于从设备而言,应该为HREADY 和HRESP 信号什么样的默认状态?

- 6、HPROT 信号默认应该是什么值?

- 7、虚拟总线主设备和默认总线主设备之间有什么区别?

- 8、AHB怎样处理锁定传输中的SPLIT 响应?

- 9、SPLIT和RETRY的适用场景

- 10、当AHB 主设备在在突发传输中间接收到从设备的RETRY 响应时,应该在HTRANS 上使用什么信号?

前言

2023.2.21

2023.3.23 学习打卡

2023.8.20 增加面试问答题

一、总线介绍

1、基本概念

AMBA:Advanced Microcontroller Bus Architecture,高级处理器总线架构,是由ARM公司制定的高性能片上(on chip)通信标准

总线位宽:总线能够一次性传送的二进制数据位数,例如8bit、16bit、32bit、64bit等。

总线工作频率:即时钟频率(时钟是系统的心脏)。

总线带宽:总线数据的传输速率(单位时间内,总线上传送的数据量。即每秒钟传送MB的最大稳态数据传输率),主要用来衡量同步通信工作效率。

波特率:单位时间内传送二进制数据的位数,主要用来衡量异步串行通信的数据传输速率,单位用bps(位/秒)表示,记作波特。

例题1:假设总线的时钟频率是100MHz,总线的传输周期为4个时钟周期,总线宽度为32位,试求总线上的数据传输率。如要提高数据传输率,可采取什么措施?

解:总线的时钟频率为100MHz,即一个时钟周期为0.01us

总线的传输周期为0.01us × 4=0.04us

由于总线的宽度为32bit=4B(字节)

故总线的数据传输率4B / (0.04us) = 100MBps = 100MB/s (p = per, ”每”)

//100*(32/8)/4=100MB/s

总线带宽的两种计算方法:

第一种:带宽 = 时钟频率 × 数据位数

第二种:带宽 = 数据位数 / 总线传输周期,总线传输周期 = n×时钟周期,时钟周期 = 1 / 时钟频率

例题2:在异步串行传输系统中,假设每秒传输120个数据帧,其字符格式规定包含1个起始位,7个数据位,1个奇校验位,1个终止位,计算波特率。

解:一帧包含1+7+1+1=10位

故波特率为10 × 120 = 1200bps = 1200波特

2、典型AMBA系统

典型的AMBA系统由一个高性能中枢总线(AHB/ASB)构成,能够支持外部存储器带宽,包括CPU,片上存储器和其他直接数据存取DMA设备。

这条总线为上述单元之间大多数的传输提供高带宽接口。在这条高性能总线上也有个桥接器以连接低带宽的APB,而在APB上连接着大多数的系统外设。

二、APB3(Advanced Peripheral Bus)

1、定义

高级外围总线:唯一的主设备是APB Bridge,然后通过APB到达其他从设备。AMBA APB优化了最小功率消耗并且降低了接口复杂度以支持外设功能。APB可以用来连接任意一种版本的系统总线。

- 低速总线、低功耗、低带宽

- 接口简单

- single-cycle bus master handover(单周期总线主机移交)

- 每次传输至少需要两个周期

- 上升沿触发

- 非流水线操作

- 适合多种外设

- 在bridge中锁存地址信号和控制信号

2、信号

3、版本信息

APB 2.0

APB 3.0:增加了PREADY、PSLVERR(传输错误信号)

APB 4.0 :增加了PPROT(protection type)、PSTRB(字节选通信号)

4、信号传输时序图

4.1 状态机

SETUP:准备状态,当一笔数据需要传递时,进入SETUP。在此状态中,HADDR[31:0]地址线会经译码电路产生唯一的使能信号PSELx。总线只会在SETUP停留一个时钟周期,而在下一个时钟正沿触发时进入ENABLE状态。这样的跳变是协议规定的。

ENABLE:使能状态,数据、地址、读写控制信号保持不变,如果没有传输跳到IDLE,有传输转回到SETUP,且跳转过程中地址、写入、选择信号有毛刺是可以接受的。

下面的transfer时序图以APB3和APB4进行介绍,就是在APB2的基础上增加了PREADY和PSLVERR信号,所以APB2就不介绍时序图了。

4.2 写操作

T0 :有限状态机进入预设的 IDLE 状态;

T1 :数据地址、读写控制信号和写入的数据会在频率正沿触发时,开始作写的数据传递准备,这个周期也就是刚才所提及SETUP状态。译码电路在此状态会根据数据地址去译码出所要写入APB Slave,此时所对应到 S 的 PSEL 信号将由 0 变 1;

T2 :有限状态机会进入 ENABLE 状态,PENABLE 信号在此状态会被设成 1;slave采样到数据地址sel信号,知道要是一次写数据操作,且自己准备好接收数据了,于是把pready信号拉高一个周期,告诉master。

T3 :master采样到slave的pready信号为高,说明slave接收了此次写数据,于是,PENABLE 信号将由 1 变 0,而 PSEL 信号在若没有其它数据的写入动作时,也将由 1 变 0。

为了减少功率的消耗,APB 的数据地址和读写控制信号在下一笔数据传递前,将不会作任何改变。(数据好像也是不会改变的)

从上面传输可以看到一次transfer至少需要两个周期。

(2)有等待周期的情况

T1:开始进入setup状态

T2:slave采样到master发过来的地址、读写控制、数据信号,假如没办法立刻接收数据,就会把ready信号拉低。

T3:pready为低,paddr、psel、penable、pwdata信号保持不变

T4:当进入enable阶段时,master采样到ready为低,于是继续进行等待,等待了两个周期。

T5:上升沿时,master采样到ready为高,于是把数据写到slave,写操作成功。

4.3 读操作

(1)无等待周期的情况

slave在传输结束前,要把数据准备好。

(2)有等待周期的情况

T0:IDLE

T1:Setup

T2:Enable

T3:检测到ready为低,继续使能。

T4:slave驱动ready信号为高,随后将RDATA驱动到数据总线

T5:master采样到ready为高,于是读取总线上的数据,读操作结束,把sel、enable信号拉低,其他为降低功耗,不发生改变。

4.4 错误传输

DUT里面应该有错误的状态,在验证的时候写一个触发错误的case,看是否功能正确。

PSLVERR:不一定都需要这个信号

PSLVERR只在APB传输的最后一个周期有效, 也就是说当PSEL,PENABLE和PREADY均为1时是有效的,在其他时间是无效的。当一些APB模块不支持PSLVERR时,比如只支持APB2协议,可以把APB Bridge的pslverr接0即可。

- 发生错误传输的时候,外设不一定要改变状态,都是可以接受的。

- 返回PSLVERR说明这次读写发生了问题。至于产生error信号如何处理协议并没有规定。

- 只在psel、penable、pready都为1的时候去采样slave的pslverr信号,看有没有错误,其它时刻不会去采样。

T2:Enable阶段时,slave无法接收master写过来的数据,于是拉低ready信号。

T3:slave发现无法写进去,告诉master出错了,于是slave驱动ready和pslverr信号同时为高

T4:master采样到它两信号同时为高,于是此次为错误transfer

5、PSTRB、PPROT信号

PPROT[2:0]:每一位对应不同的类型信息。该信号主要用来区分安全和不安全标识,也就是PPROT[1],其他两位不同的地方可以有不同的解释。

| PPROT[2:0] | Protection level |

|---|---|

| [0] | 1:privileged access, 0 :normal access |

| [1] | 1 :nonsecure access, 0 :secure access |

| [2] | 1 :instruction access, 0 : data access |

PSTRB[3:0]:写strb信号,决定哪个字节通道的写数据是有效的,可以进行稀疏数据(sparse data)的传输,每一bit位对应pwdata的一个字节,且在读数据的时候该信号必须无效。(任何时候,只允许一个数据总线有效,只可以读或只可以写)

6、APB组成

APB的组成:APB Bridge + APB Slave

APB Bridge:完成AHB 总线传输到APB 总线传输的转换工作

APB Slave:接口简单但是灵活

三、AHB(Advanced High-performance Bus)

1、定义

高级高性能总线:AHB总线的强大之处在于它可以将微控制器CPU、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线master、各种拥有AHB接口的控制器等连接起来构成一个独立的完整SOC系统,不仅如此,还可以通过AHB-APB Bridge来连接APB总线系统。

总线宽度有8、16、32、64、128等等,最常用的是32位。

- 适合于高性能、高时钟频率

- 通道操作

- 流水线操作

- 多总线主机

- burst传输

- Split transactions(分块处理)

- 单时钟沿操作

- 更宽的数据总线配置(64/128 位)

- 非三态总线实现(只传输0和1)

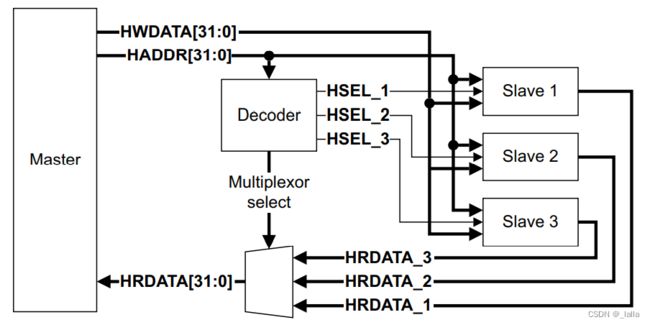

每个AHB都需要1个仲裁器和1个中央解码器。

(1)AHB主设备Master:发起一次读/写操作,某时刻只允许一个主设备使用总线,每个主设备有一组与仲裁器接口的信号REQUEST/GRANT,仲裁器采用优先级方案来决定当前请求总线的优先级最高的主设备。

每个主设备同时产生HLOCKx信号来指示主设备需要独占的总线访问。

(2)AHB从设备Slave:响应一次读/写操作,通过地址映射来选择使用那个从设备

(3)AHB仲裁器Arbiter(多主机master):允许某一个主设备控制总线,按道理需要等一个master传输结束之后,再重新进行仲裁,但是为了总线长时间被占用,可以允许其他master进行打断,这时需要重新申请仲裁才能发送完数据。

(4)AHB译码器Decoder:通过地址译码来决定选择哪一个从设备,产生片选信号

(5)多路转换器:译码器控制,转换器输入是多个slave的rdata和响应信号(传输成功、失败、等待传输三种状态)

slave无法响应被扩展的地址相位,因为slave必须在指定周期内完成采样地址;

slave可以响应被扩展的数据相位,因为hready拉低插入等待状态

2、信号

下面介绍的AHB-lite的信号

AHB-lite是单主机多从机,不支持retry和split传输

2.1 master端信号

HSELx:每个slave对应一个片选信号,当某个slave被选中的时候,会去采样HREADY,确保在开始传输之前,其他slave已经传输结束,检测到为高电平后马上开始当前传输。

HMASTLOCK:锁定Master传输,告诉其他slave,锁定期间当前序列传输无法被打断。为1表示master锁定的操作,与地址和控制信号具有相同的时序(未用到过)。传输被锁定后,下一拍建议插入IDLE。

大部分Slave不必需要HMASTLOCK,因为它们仅传输所收到的数据,但在多个Master系统中,有可能被多个Master 访问,就必须调用HMASTLOCK信号。

HADDR[31:0]:里面包含片选和地址信号,一般高位地址译码产生,低位为地址。经Decoder译码后产生片选,选择一个slave,再去把数据写/读进去该slave的相应地址。

HWRITE:读写控制信号,高电平表示写,低电平表示读

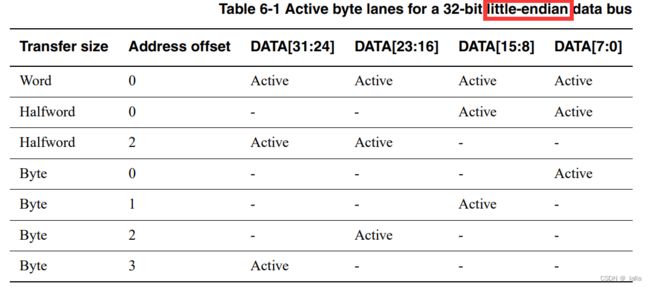

HSIZE[2:0]:传输数据的位宽,8、16、32…1024(最大)等,大小要小于数据宽度。

地址边界和传输大小必须对齐。字传输对齐字地址边界(HADDR[1:0] = 0),半字传输对齐半字地址边界(HADDR[0] = 0)

| HSIZE[2:0] | Size/bits | Description |

|---|---|---|

| 000 | 8 | Byte |

| 001 | 16 | Halfword |

| 010 | 32 | Word |

| 011 | 64 | DoubleWord |

| 100 | 128 | 4-word line |

| 101 | 256 | 8-word line |

| 110 | 512 | - |

| 111 | 1024 | - |

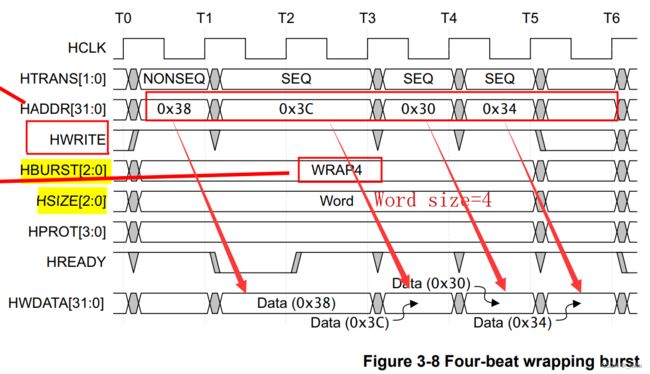

HBURST[2:0]:burst长度,单个,4,8,16(两种),undefined length(总共8种情况)。

Master不允许开始一次跨越1k地址边界的传输,单个slave的最小地址范围为1kB,不允许是为了防止master在传输时访问到其他slave,造成错误。

不允许使用BUSY来结束固定长度的burst,必须是SEQ来结束。

仅未定义长度的burst传输可以用BUSY来结束。

| HBURST[2:0] | Type | Description |

|---|---|---|

| 000 | SINGLE | single transfer |

| 001 | INCR | incrementing burst of undefined length |

| 010 | WRAP4 | 4-beat wrapping burst |

| 011 | INCR4 | 4-beat incrementing burst |

| 100 | WRAP8 | 8-beat wrapping burst |

| 101 | INCR4 | 8-beat incrementing burst |

| 110 | WRAP16 | 16-beat wrapping burst |

| 111 | INCR16 | 16-beat incrementing burst |

HTRANS[1:0]:传输状态IDLE, BUSY, NONSEQUENTIAL, SEQUENTIAL。

| HTRANS[1:0] | Type | Description |

|---|---|---|

| 00 | IDLE | 空闲状态 |

| 01 | BUSY | master无法传输时发送该类型 |

| 10 | NONSEQ | single/busrt transfer的第一个 |

| 11 | SEQ | burst transfer中的一个传输 |

HPROT[3:0]:保护控制信号,对于带有存储器管理单元的总线主机来说这些信号也表示当前访问是带高速缓存的( cache)还是带缓冲的(buffer)。

由于一些Master无法生成正确的保护信号,因此建议master设置该信号为0011,slave则不使用该信号。

| HPROT[3:0] | Protection level |

|---|---|

| [0] | 0: Opcode fetch,1: Data access |

| [1] | 0:User access,1: Privileged access |

| [2] | 0: Non-bufferable,1: Bufferable |

| [3] | 0: Non-cacheable,1: Cacheable |

HSTRB[3:0]:字节选通信号,有效字节通道取决于系统的端结构(小端系统和大端系统),但是 AHB 并不指定要求的端结构。因此,总线上所有主机和从机的端结构相同这点很重要。一般AHB用的是小端。

2.2 slave端信号

HRDATA[31:0]:在此次传输结束之前,slave把数据驱动到总线上

HREADYOUT:高电平表示传输在总线上结束,可以拉低来对信号进行扩展

HRESP:slave应答当前传输状态,低电平表示传输正常,高电平表示传输错误

HRESP[1:0]:是AHB2的信号,有四个状态OKAY, ERROR, RETRY, SPLIT。后三者都是双周期响应,需要双周期响应是因为总线通道的本质特征。在从机开始发出 ERROR、SPLIT或者RETRY中任何一个响应时接下来传输的地址已经广播到总线上了。

双周期响应允许主机有足够的时间来取消该地址并且在开始下一次传输之前驱动HTRANS[1:0]为IDLE。

SPLIT和RETRY响应给从机提供了在无法立刻给传输提供数据时释放总线的机制。SPLIT传输有可以完全释放总线给其他主机使用的优点(可以给优先级更低的主机),但是RETRY的情况就只允许较高优先级的主机使用总线。

| HRESP[1:0] | Type | Description |

|---|---|---|

| 00 | OKAY | HREADY为高表示传输完成 |

| 01 | ERROR | 传输发生错误 |

| 10 | RETRY | 重试表示传输还没完成,总线主机应该重新传输直至完成 |

| 11 | SPLIT | 传输还没完成总线主机在下一次被授予总线访问时重新传输 |

当传输产生时如果从机认为传输的执行将占据大量的时钟周期那么从机能够决定发出一个SPLIT响应。该信号提示仲裁器尝试这次传输的主机不应该被授予访问总线,直到从机表示它准备好了完成传输时。因此仲裁器负责监视响应信号并且在内部屏蔽已经是SPLIT传输主机的任何请求。

2.3 AHB2版本的arbiter信号

HMASTER[3:0]:用于指示当前是哪个Master发起了传输,每个Master有一个唯一的HMASTER ID,最大值为8

HNONSEC:说明本次是安全还是非安全的传输

2.4 默认值

如果SEQ或者NONSEQ的传输地址不存在,默认情况下会返回ERROR

如果BUSY或者IDLE的传输地址不存在,默认情况下会返回OKAY

3、版本信息

AHB

AHB+lite(简化设计)

AHB5+lite(丰富接口)

4、信号传输时序图

4.1 basic transfer

Address phase:master驱动地址和控制信号到总线上,只允许有一个周期

Data phase:slave采样地址和控制信号,开始驱动HREADY信号做出响应

如果是读,则在ready拉高后把数据驱动到总线上

如果是写,则master在上升沿的时候就把wdata驱动到总线上了,可以有多个周期

A和C的传输没有延时,B的传输延时了一个周期

B的data phase的延长使得下一个transfer的address phase延长

AHB支持流水线pipeline的动作,在slave收上一笔数据的同时,master可将下一笔数据的地址送出。

4.2 busy transfer

Q:BUSY可以发生在burst之后吗?

BUSY传输发生在INCR之后,不能发生在固定长度burst之后

主机由于不能立刻发送burst的第二个transfer,所以发送一个BUSY使得下一次传输延时开始,第二个SEQ发送没有延时,第三个SEQ,从机无法立刻响应,所以插入hready延时,最后一个SEQ没有延时。

4.3 burst transfer

(1)写数据 WRAP4

(2)读数据 INCR4

T1:slave采样到地址和控制信号,但是无法驱动数据,于是拉低

T2:master采样到ready为低,于是保持地址和控制信号不变,slave这个周期拉高了ready,并在拉高后不久把数据驱动到了总线上

T3:master采样到ready为高,继续发送地址。slave的ready有效,继续驱动数据到总线上

4.4 等待传输——hready为低修改地址和trans的情况

推荐Slave最多插入16个等待状态,防止某个访问把总线锁死。

Slaves使用HREADY来插入等待状态,以获得更多的时间提供或采样数据。在等待传输期间,Master被限制改变传输类型和地址。

改变TRANS:

- IDLE

- BUSY传输固定长度burst

- BUSY传输未定义长度burst(INCR)

改变地址:

- IDLE

- ERROR响应之后

4.4.1 IDLE传输——改了地址和trans

在IDLE状态时,是可以改变地址的,但是当开始发送第一个NONSEQ的时候,地址需要保持不变

这里ready拉低是可能slave暂时无法驱动数据,因此延时一段时间;而由于是单个数据发送,所以下一个状态就是idle。且在ready拉低的这个时间内,master是可以继续向slave申请rdata,只是slave必须先响应完上一个请求,再来响应此次请求。且在这个时间内,地址是不能发送改变的。

这样做性能较高,但是实际取设计验证的driver是有点困难的。

4.4.2 BUSY传输固定长度burst——只改变了trans

burst传输时,在ready期间,允许从BUSY改变为SEQ(SINGLE是不行的)

(BUSY传输时的地址和数据与下一拍相同)

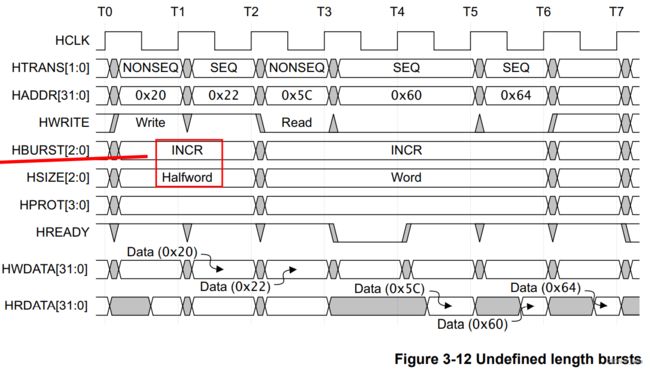

4.4.3 BUSY传输未定义长度INCR——改变了地址和trans

前面说过,仅未定义长度的burst传输可以用BUSY来结束

当hready为低时,允许busy跳转到任意状态,下图是跳转到NONSEQ,表明当前传输结束,开始新的传输。

4.4.3 ERROR响应之后——改变了地址和trans

前面说过ERROR是双周期响应,在响应之后会在下一次传输开始之前插入IDLE状态。

那么在T4时刻,hready为低,但是地址和传输状态都发生了改变

四、总线对比

完整的AHB/ASB用作:

- 总线主机;

- 片上存储模块;

- 片外存储器接口;

- 带FIFO接口的高带宽外设;

- DMA从机外设。

简单的APB外设接口建议用作:

- 简单的寄存器映射从机设备;

- 时钟不能够全局布通的超低功耗接口;分组窄总线外设应避免挂接到系统总线上

4.1 hready和hreadyout信号区别

hreadyout:slave的输出信号,是slave对master数据传输的响应,如果为高,表示slave准备好传输,如果为低,表示slave还没有准备好,会延长数据周期。

hready:该信号是所有slave的hreadyout相与得到的,是slave的输入信号。

场景:一个主设备对应多个从设备,AHB的流水线操作,可能上一个slave的数据还没有传输完全,下一个slave就要开始传输,可能发生协议错误或者数据丢失。

等到所有的slave传输完成,hready信号为高,则开始此次传输。

下图中S3阶段要去采样data1还是data2就成了问题

只有加入一个hready信号,使得当hready为低时,所有slave的传输都被延时,等到slave1传输结束后,开始写入data1,同时采样下一个传输的地址和控制信号。

4.2 APB2、APB3、APB4协议区别

APB3中增加了PREADY、PSLVERR信号

APB4中增加了PSTRB、PPROT信号

除了新增加信号以外,APB3提供了低功耗的接口,降低了接口的复杂性

4.3 AHB2、AHB-Lite、AHB5协议对比

相同点:

- burst传输

- 单边沿操作

- 非三态

- 宽数据总线32,64等

区别:

| AHB2 | AHB-Lite | AHB5 |

|---|---|---|

| 多主机,多从机 | 单主机,多从机 | 单主机,多从机 |

| 有仲裁机制 | 无仲裁机制 | 无仲裁机制 |

| 支持SPLIT和RETRY响应 | 不支持SPLIT和RETRY响应 | 不支持SPLIT和RETRY响应 |

| 需要默认主机和从机 | 需要默认主机,不用默认从机 | |

| 扩展存储器类型PPROT[6:0] | ||

| 独占传输 | ||

| 原子访问 |

默认从机:在系统设计中如果有包含一个存储器映射并未完全填满(存储空间)的情况时,应该设置一个额外的默认从机,以在访问任何不存在的地址空间时提供响应。如果一个非连续或者连续传输试图访问一个不存在的地址空间时,这个默认从机应该提供一个 ERROR 响应。空闲或者忙传输访问不存在的空间(默认从机)应该给出一个零等待状态的 OKAY 响应。这个默认从机的功能将以作为中央地址译码器的一部分来实现。

五、面试问答题

1、主设备可以在hready为1的时候改变地址和控制信号吗

可以的。以下两者情况可以。

- 如果地址和控制信号表示的是一个

IDLE传输,那么主设备可以在HREADY 为低的时候将传输改为一个真正的传输(NONSEQ)。 - 如果主设备当前正表示一个真正的传输(NONSEQ或者SEQ),那么主设备不能在传输等待中取消这次传输,除非主设备接收到SPLIT。RETRY或者

ERROR响应。

2、AHB主设备可以直接连到AHB从设备吗?

任何不支持SPLIT响应的从设备都可以直接连到AHB主设备上。

如果一个AHB 主设备直接连到AHB 从设备,那么必须确保从设备在复位的时候维持HREADY信号为高,并且从设备选择信号HSEL 永远维持为高。

3、在AHB系统中可以支持多少个主设备?

AHB 规范中提供了最多16 个主设备

4、主设备在扩展的传输中可以改变HADDR吗?

如果主设备表示它想进行NOSEQ,SEQ 或者BUSY 传输,那么它就不允许在扩展的传输中(当HREADY 为低时)改变地址总线上的值,除非它接收到了ERROR,RETRY 或者SPLIT 响应。

如果主设备表示它想进行一个IDLE 传输,那么它可以改变地址信号。

5、对于从设备而言,应该为HREADY 和HRESP 信号什么样的默认状态?

HREADY:高电平

HRESP:OKAY

6、HPROT 信号默认应该是什么值?

建议值:4’b001

7、虚拟总线主设备和默认总线主设备之间有什么区别?

默认总线主设备:系统中没有主设备在申请总线的时候,总线被分配给的那个主设备。通常情况下,最有可能申请总线的主设备就是默认总线主设备。

虚拟主设备:只进行IDLE 传输的主设备。系统需要虚拟主设备是以便仲裁器能够保证能够将总线分配给一个不进行任何实际传输的主设备。

8、AHB怎样处理锁定传输中的SPLIT 响应?

仲裁器就会夺回被SPLIT 的主设备的总线使用权并该主设备将不会再参与仲裁,直到从设备表示传输可以完成。

9、SPLIT和RETRY的适用场景

SPLIT:可能同时被多个不同的主设备访问的从设备

RETRY:在只被一个主设备访问的外设中

10、当AHB 主设备在在突发传输中间接收到从设备的RETRY 响应时,应该在HTRANS 上使用什么信号?

设置为NONSEQ