【PCIE体系结构十七】PCIE电源管理之PCI-PM

个人主页:highman110

作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《PCI.EXPRESS系统体系结构标准教材 Mindshare》

目录

设备PM状态

1.D0状态

2.D1和D2状态

3.D3状态

D状态迁移

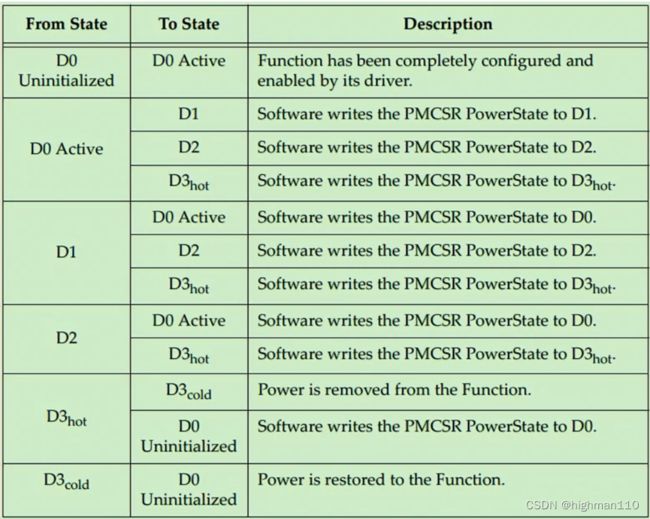

设备唤醒

PCIe总线与PCI总线使用的PCI-PM管理机制兼容。在PCIe设备的扩展配置空间中定义了Power Management Capabilities结构,该结构中含有一系列寄存器,系统软件通过修改PMCSR寄存器的Power State字段,可以使PCIe设备进入不同的节能状态D-State,如D0、D1、D2和D3状态。其中DO是正常工作状态,功耗最高,而D1、D2和D3为低功耗状态。其中D1的休眠等级最低,功耗相对较高,而D3的休眠等级最高,功耗相对较低。D-State的状态转换关系如下图:

设备PM状态

1.D0状态

PCIe设备必须支持D0状态,该状态由D0uninitializated和D0active两个子状态组成。当PCIe设备处于D0uninitializated状态时,该PCIe设备并没有被系统软件使能,此时该PCIe设备仅能接收配置读写请求TLP,不能主动发出其他TLP。此时该PCIe设备配置寄存器的Command寄存器为复位值0x00。此时虽然PCIe设备已经被加电,但是并不能正常使用。当PCIe设备处于D0active状态时,PCIe设备处于正常工作模式,并没有任何节电措施。但是PCIe设备仍然可以使用ASPM机制,将链路状态迁移到L0s或者L1状态,以降低功耗。值得注意的是,ASPM机制与PCI PM机制是独立的。当PCIe设备进行复位后,该设备将首先进入D0uninitializated状态。系统软件通过修改PMC-SR寄存器的Power State字段,也可以使设备从D3hot状态迁移到该状态。值得注意的是D3cold状态迁移到该状态的过程与复位操作等效。当系统软件改写Command寄存器的状态位使能PCIe 设备后,该设备从D0uninitializated迁移到D0active状态。

2.D1和D2状态

D1和D2状态分别为PCle设备的轻度和重度休眠状态。这两个状态为PCIe设备的可选状态,PCIe设备处于D1状态时的功耗高于D2状态。PCle设备处于这两个状态时,除了PME消息之外,不能主动发送其他TLP;除了接收配置请求TLP外,不能接收其他TLP。当PCIe设备处于这两种状态时,可以向RC发送PME消息,通知系统软件该PCIe设备进入休眠状态。当PCIe设备进入D1或者D2状态时,PCIe链路将进入L1状态。PCIe设备可以从D1和D2状态直接返回到D0active状态。

3.D3状态

PCIe设备必须支持D3状态,D3状态由D3hot和D3cold两个子状态组成。PCIe设备处于D3hot状态与处于D1/D2状态时的功能类似,只是PCIe设备只能从D3hot状态返回D0uninitializated状态,而不能返回D0active状态。对于PCIe设备,从D3hot状态返回D0uninitializated状态的过程相当于热复位。

当PCle设备的Vcc电源被移除时,PCIe设备无论处于何种状态,都将进入D3cold状态。值得注意的是一个PCIe设备使用两种电源Vcc。和Vaux,Vcc电源被移除并不意味着PCIe设备被完全下电。

有些PCIe设备在处于D3cold状态时仍然可以发出PME消息,此时这个PCIe设备负责发发送PME消息的功能模块必须使用Vaux而不是Vcc进行供电。

D状态迁移

PCIe设备可以进行D-State的状态迁移。大多数D-State的状态迁移都是系统软件通过修改PMCSR寄存器的Power State字段实现的,但是仍然有些状态迁移采用了其他方式,比如:

1、使能Command寄存器的命令位,可以使设备从D0uninitializated状态迁移到D0active状态。

2、PCIe设备的Vcc被移除时,D3hot状态将迁移到D3cold状态。

3、当PCIe被唤醒,Vcc重新上电之后,PCIe设备将从D3cold状态迁移到D0uninitializated状态。

具体的状态迁移关系如下图:

当PCIe设备进行D-State状态迁移时,PCIe链路的状态也可能随之变化。PCIe设备的D-State 状态与PCIe 链路状态的对应关系如下表:

如下是系统软件修改PMCSR寄存器的Power State字段,将PCIe设备从D0迁移到D1状态的过程举例:

如下是系统软件修改PMCSR寄存器的Power State字段,将PCIe设备从D0迁移到D1状态的过程举例:

1、上游设备向下游设备发送配置写请求TLP,改变下游设备PMCSR寄存器的Power State字段,从而使下游设备从D0状态迁移到D1状态。

2、下游设备收到这个配置写请求TLP后,将改变PMCSR寄存器的Power State字段,并向上游设备发送配置写完成TLP。这个配置写完成TLP首先需要经过数据链路层,并从对端获得足够的发送Credit(这个是流控中的概念,后面再学习)后,将这个配置写完成TLP通过数据链路层发送到对端。

3、下游设备的事务层收到数据链路层的确认后,得知配置写完成TLP已经被上游设备正确接收后(即ACK/NAK协议,下游设备收到了上游设备发过来的ACK DLLP),将挂起下游设备的事务层。并向上游设备连续发送PM_Enter_Ll DLLP(数据链路层的电源管理DLLP报文),同时等待来自上游设备的PM_Request_Ack报文。

4、上游设备收到下游设备的PM_Enter_L1 DLLP后,首先禁止发送新的TLP,并等待之前发送的Non-Post TLP得到确认后,挂起上游设备的事务层,并向下游设备连续发送PM_Request_Ack DLLP。

5、下游设备在没有收到上游设备的PM_Request_Ack DLLP之前,虽然事务层已经被挂起,但是数据链路层和物理层仍然可以正常工作,此时数据链路层可以正确接收来自上游端口的DLLP,并发送ACK/NAK和流量控制相关的一些DLLP。

6、当下游设备收到PM_Request_Ack DLLP后,将停止发送PM_Enter_L1 DLLP,挂起数据链路层,然后将物理层置为Electrical Idle状态。

7、上游设备发现其接收链路处于Electrical Idle状态时,将停止发送PM_Request_Ack DLLP,并挂起数据链路层,然后将物理层置为Electrical Idle状态。此时PCIe链路将进入L1状态。

当PCIe链路处于L1状态时,如果系统软件需要改变下游PCIe设备PMCSR寄存器的Power State字段,PCle链路需要首先从L1状态迁移到正常工作状态L0,下游设备才能接收这个配置写请求TLP。

PCIe设备其他D-State状态的迁移过程与此大同小异,大家自行查阅PCIe总线规范,这里不再赘述。

设备唤醒

在前面的D状态迁移表里我们可以看到,D3cold的进出涉及到Vcc电源的移除和重新上电,其他D状态的迁移都可以通过设备发出唤醒请求,然后PM软件写PMCSR寄存器来操作。写寄存器迁移状态好理解,软件操作即可,假设是Vcc掉电了,进入了D3cold状态,这个时候显然不能直接写寄存器了,那PCIE设备要是有唤醒请求了,它要怎么通知主机来给它重新上电、重新进行链路训练并迁移D状态呢?

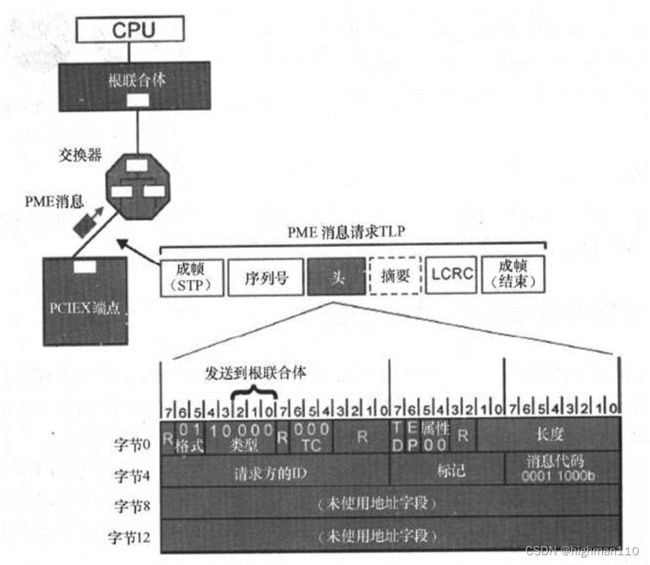

PCIExpress设备不使用PCI所定义的PME#边带信号,而是使用带内PME消息来通知PM软件有关将设备返回到满电状态(D0)的请求。在所有低功耗状态内,对生成PME消息能力的支持是可选的。设备会报告其所支持的PM状态,并且从这些状态内可以发送PME消息。需要注意的是,仅在链路电源状态转换到L0时才可传递PME消息(PME消息实际上是message TLP报文)。

如果链路处于非L0状态,则需要通过其他的方式先来唤醒链路。PCIe Spec定义了两种方式:

1、Beacon,一种低速的带内信标信号,在前面提到过,该信号只需要AUX电源供电即可;

2、WAKE#,一种边带信号(低电平有效),该信号同样只需要AUX电源供电即可。

无论使用哪种方法,必须通知PM软件,使其可以重新施加主电源并重新启动参考时钟。之后就会生成基本复位,强制设备进入D0未初始化状态。一旦链路转换到L0状态,设备就可以发送PME消息。

可以发送PME消息之后,将按如下流程进行唤醒的后续操作:

1、当前PCIe设备将PME消息发送至其上一级端口(Upstream Port);

2、该PME消息通过模糊寻址的方式,通过Switch(如果有的话),最后达到Root;

3、Root接收到了PME消息后,将其内容转发给PM控制器(Power Management Controller);

4、该控制器通知PM软件,产生一个中断告知系统。软件利用PME消息中的Requester ID来发起配置空间读写操作,并使得对应的PCIe设备返回至D0状态(或者其他状态)。在这个过程中,PCIe驱动可能需要暂时备份该设备的PCIe配置空间的寄存器值;

5、软件恢复该PCIe设备的相关信息(配置空间寄存器等)。

有几点需要注意的是:

1、PME消息只能采用模糊寻址(Implicitly)方式;

2、PME消息的TC和VC只能是0,即不支持QoS;

3、PME消息是一种Message,因此其是Posted的,即不需要Completion与之对应;

4、PME消息不支持Relaxed Ordering,且总是强制当前器件与Root之间的链路上的所有PCIe设备中的所有其他的事务层包(TLP)在PME消息之前发送。

PME消息报文结构如下:

PCIE的电源管理部分就介绍到这里。