HDLBits-Verilog学习记录 | Verilog Language-Modules(2)

文章目录

- 25.Adder 1 | Module add

- 26.Adder 2 | Module fadd

- 27.Carry-select adder

- 28.Adder-subtractor

25.Adder 1 | Module add

practice:

You are given a module add16 that performs a 16-bit addition. Instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result, after receiving the carry-out from the first adder. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored), but the internal modules need to in order to function correctly. (In other words, the add16 module performs 16-bit a + b + cin, while your module performs 32-bit a + b).

您将获得一个执行 16 位加法的模块 add16。实例化其中两个以创建 32 位加法器。一个 add16 模块计算加法结果的低 16 位,而第二个 add16 模块在收到来自第一个加法器的结转后计算结果的高 16 位。您的 32 位加法器不需要处理进入(假设为 0)或传出(忽略),但内部模块需要处理才能正常运行。(换句话说,add16 模块执行 16 位 a + b + cin,而模块执行 32 位 a + b)。

Connect the modules together as shown in the diagram below. The provided module add16 has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

module top_module(

input [31:0] a,

input [31:0] b,

output [31:0] sum

);

wire cout_1;

add16 ins_add1 ( .a(a[15:0]), .b(b[15:0]), .cin(1'b0), .sum(sum[15:0]), .cout(cout_1) );

add16 ins_add2 ( .a(a[31:16]), .b(b[31:16]), .cin(cout_1), .sum(sum[31:16]), .cout() );

endmodule

注:(独立完成部分60%)这道题由于对题目的理解有误,实际上还是个配对问题,但我想复杂了,以为需要计算什么的,结果一直编译不通过。这里应该还是基础课程没有跟上,导致题目理解不清楚。

第二行的.cout()不写也是success!的

26.Adder 2 | Module fadd

practice:

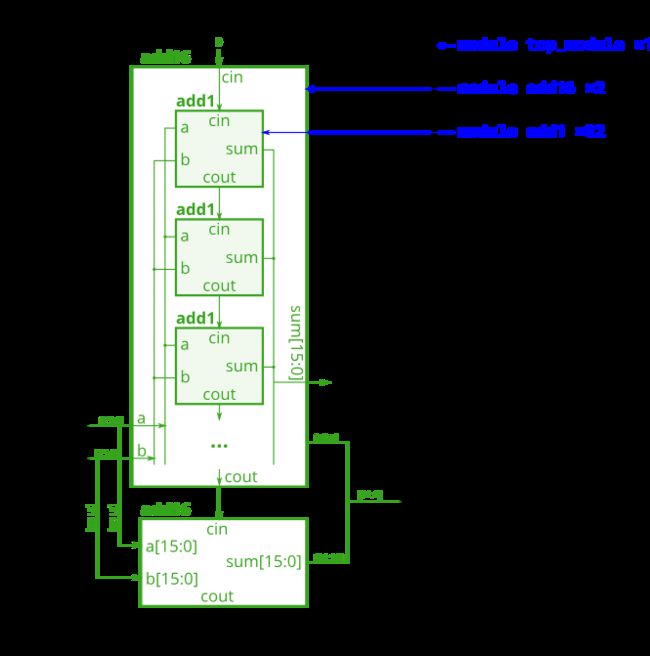

In this exercise, you will create a circuit with two levels of hierarchy. Your top_module will instantiate two copies of add16 (provided), each of which will instantiate 16 copies of add1 (which you must write). Thus, you must write two modules: top_module and add1.

在本练习中,您将创建一个具有两个层次结构级别的线路。您的top_module将实例化 add16 的两个副本(提供),每个副本将实例化 add1 的 16 个副本(您必须编写)。因此,您必须编写两个模块:top_module 和 add1。

Like module_add, you are given a module add16 that performs a 16-bit addition. You must instantiate two of them to create a 32-bit adder. One add16 module computes the lower 16 bits of the addition result, while the second add16 module computes the upper 16 bits of the result. Your 32-bit adder does not need to handle carry-in (assume 0) or carry-out (ignored).

与module_add一样,您将获得一个执行 16 位加法的模块 add16。必须实例化其中两个才能创建 32 位加法器。一个 add16 模块计算加法结果的低 16 位,而第二个 add16 模块计算结果的高 16 位。您的 32 位加法器不需要处理进入(假设为 0)或进转(忽略)。

Connect the add16 modules together as shown in the diagram below. The provided module add16 has the following declaration:

module add16 ( input[15:0] a, input[15:0] b, input cin, output[15:0] sum, output cout );

Within each add16, 16 full adders (module add1, not provided) are instantiated to actually perform the addition. You must write the full adder module that has the following declaration:

在每个 add16 中,实例化 16 个完整的加法器(模块 add1,未提供)以实际执行加法。您必须编写具有以下声明的完整加法器模块:

module add1 ( input a, input b, input cin, output sum, output cout );

Recall that a full adder computes the sum and carry-out of a+b+cin.

回想一下,一个完整的加法器计算 a+b+cin 的总和和结转。

In summary, there are three modules in this design:

- top_module — Your top-level module that contains two of…

- add16, provided — A 16-bit adder module that is composed of 16 of…

- add1 — A 1-bit full adder module.

If your submission is missing a module add1, you will get an error message that says Error (12006): Node instance “user_fadd[0].a1” instantiates undefined entity “add1”.

如果提交缺少模块 add1,您将收到一条错误消息,指出错误 (12006):节点实例“user_fadd[0].a1”实例化未定义的实体“add1”。

Full adder equations:

sum = a ^ b ^ cin

cout = a&b | a&cin | b&cin

在这里插入代码片