【详细】芯片设计全流程(包括每个流程需要用到的工具以及需要参与的工作人员)

IC设计流程图全览

一颗芯片的诞生经历了设计、制造和测试(分别对应集成电路产业链的设计业、制造业和封测业),而每一步都包含了复杂的步骤和流程,如图0-1所示。

现在,我们重点介绍芯片设计的全流程以及每个流程需要用到的设计工具和需要参与的工作人员。

一、IC设计分类

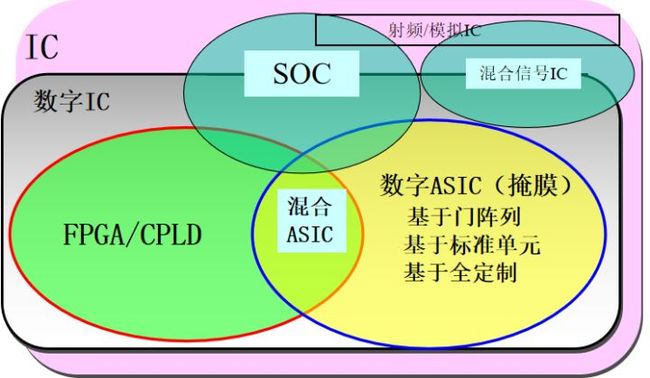

首先对IC设计的分类做个介绍,如图1-1所示。

如图1-1所示,IC设计可以粗分为数字IC设计和射频/模拟IC设计;数字IC设计又可分为ASIC设计和FPGA/CPLD设计;此外还有一部分IC设计采用数模混合设计,如:SOC设计和数模混合信号IC设计。

关于数字IC中的ASIC与FPGA/CPLD的区别:

- ASIC(Application Specific Integrated Circuit,专用集成电路):需制作掩模,设计时间长,硬件不能升级;芯片面积小,性能可以得到较好的优化;适合芯片需求量大的场合:片量用于平摊昂贵的光罩掩模制版费,降低单片生产成本。

- FPGA/CPLD(Field Programmable Gate Array,现场可编程门阵列 / Complex Programmable Logic Device,复杂可编程逻辑器件):不需要后端设计/制作掩模,可编程;开发门槛较低,设计时间较短,可方便和快速地升级优化硬件;芯片面积大,性能不够优化 ;适合芯片需求量小的场合:不用支付昂贵的光罩掩模制版费。作为数字ASIC设计流程中的必要步骤:ASIC设计中前端设计的FPGA原型验证(HDL功能验证)。

模拟/射频IC:处理模拟信号,规模远不如数字IC,放大器( RF放大器、中放、运放、功放);比较器;振荡器;混频器;模拟PLL;稳压稳流源等

数模混合信号IC: ADC、DAC;某些Driver;电源管理;等等

SOC:System on Chip(系统集成电路,片上系统)

二、IC设计中需要考虑的因素

1、满足功能和性能的要求(性能:速度、功耗)

2、降低芯片成本(包括:设计、制造、测试)

- 设计:良好的设计流程,就能降低芯片的设计成本。

- 制造:需要优化设计来减少芯片面积,增加每个晶圆上的管芯数,在设计中采用DFM方法来提高芯片制造成品率。

- 测试:在设计中采用可测试性设计(DFT)方法,降低每个芯片的测试时间等。

- 单芯片成本计算方式:CT = CD/N + CP/(y*n) + 封装测试成本

- 第一项表示分摊到每个芯片上的设计费用:CD是设计及掩模制版费(也叫NRE费用), N是总产量;

- 第二项表示每个芯片的制造费用:CP是每个晶圆的制造费用,n是每个晶圆上的管芯数,y是晶圆成品率;

(3)延长芯片的使用寿命

(4)缩短芯片面市时间(Time-to-Market)

三、数字IC设计流程及EDA工具和人员分工

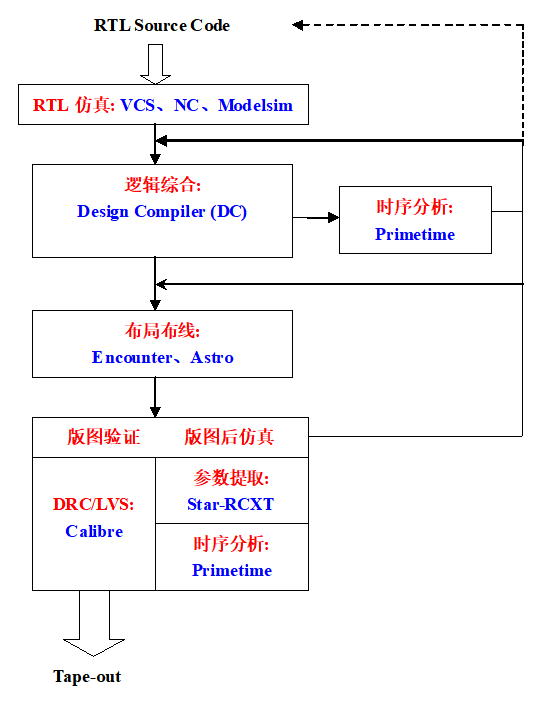

数字IC设计流程:三个阶段(前端设计+功能验证+后端实现),如图3-1所示。

- RTL前端+功能验证(最终得到的是RTL source code)

- GDSII后端:逻辑综合+后仿真(最终得到的是GDSII文件)

1、第一阶段:前端设计(RTL设计、逻辑设计)

用硬件描述语言HDL(Verilog、VHDL)来描述;描述硬件电路,抽象地表示电路的结构和行为(怎样组成,完成什么功能);

HDL描述的两种方式:

结构描述:若干部件用信号线互连形成一个实体;

行为描述:反映信号的变化、组合和传播行为,特点是信号的延迟和并行性;

HDL的作用:

具有与具体硬件电路无关和与EDA工具平台无关的特性,简化了设计;

支持从系统级到门和器件级的电路描述,并具有在不同设计层次上的仿真/验证机制;

可作为综合工具的输入,支持电路描述由高层向低层的转换;

数字ASIC设计中采用的典型EDA工具

2、第二阶段:功能验证(前仿真)

检验RTL级的HDL设计是否实现了Spec.需要的功能等;

- 仿真:先对设计进行一系列的激励(输入),然后有选择的观察响应(输出)

- 激励与控制:设置输入端口,输入激励向量;

- 响应和分析:及时监控输出响应信号变化,判断是否正确、合法;

- 常用的仿真EDA工具:VCS (Synopsys), Modelsim(Mentor), NC(Cadence)

3、后端实现(逻辑综合+时序分析+布局布线+版图验证,后仿真)

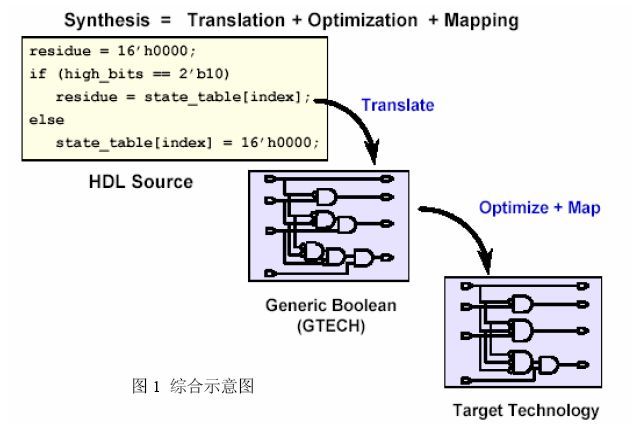

(1)逻辑综合:

将描述电路的RTL级HDL转换到门级电路网表netlist的过程;根据该电路性能的要求(限制),在一个由制造商提供的包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个门级逻辑网络结构的最佳实现方案,形成门级电路网表netlist;

综合EDA工具主要包括三个阶段:转换(Translation)、优化(Optimization)与映射(Mapping)

转换阶段:将RTL用门级逻辑来实现,构成初始的未优化电路。

优化与映射:对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上

常用的EDA工具:Design Compiler(Synopsys)

(2)时序分析

时序分析一般采用静态时序分析STA(Static Timing Analysis),以验证门级逻辑网络结构netlist的时序是否正确

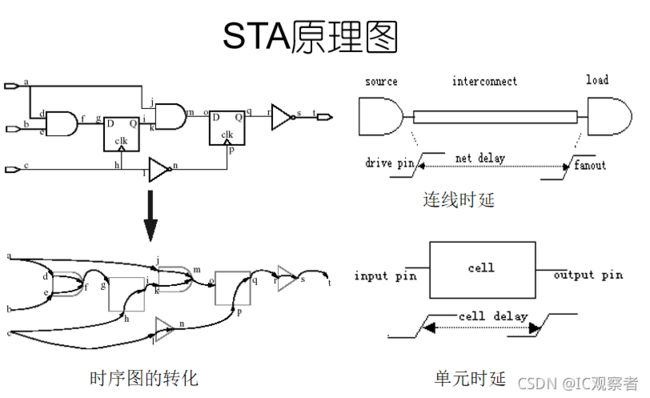

图3-5 STA原理图

图3-5 STA原理图

STA工具的基本思想: 在netlist中找到关键路径

- 关键路径是netlist中信号传播时延的最长路径,决定了芯片的最高工作频率;

STA工具可以分为三个基本步骤:

- 第一是将netlist看成一个拓扑图 ;

- 第二是时延计算(连线时延 net delay、单元时延 cell delay);

- 第三是找到关键路径并计算时延,进行判断;

常用的时序验证EDA工具:PrimeTime(Synopsys) ;

(3)布局布线

将门级电路网表(netlist)实现成版图(layout)

常用的EDA工具:Encounter(Cadence)、Astro (Synopsys)

(4)版图验证

版图验证包括DRC和LVS;

DRC(Design Rule Check,设计规则检查):保证版图的可制造性,保证版图满足芯片制造厂的版图设计规则(Design Rule);

LVS(Layout Versus Schematic,电路规则检查 ):证明版图与门级电路网表netlist的一致性;

常用的EDA工具:Mentor的Calibre,Synopsys的Hercules;

(4)后仿真

后仿真是保证版图是否满足时序的要求,在后仿真之前首先要进行参数提取,提取版图的连线时延信息(RC Extract),后仿真STA等;

常用的参数提取EDA工具:Synopsys的StarRCXT

常用的后仿真STA EDA工具:Synopsys的PrimeTime

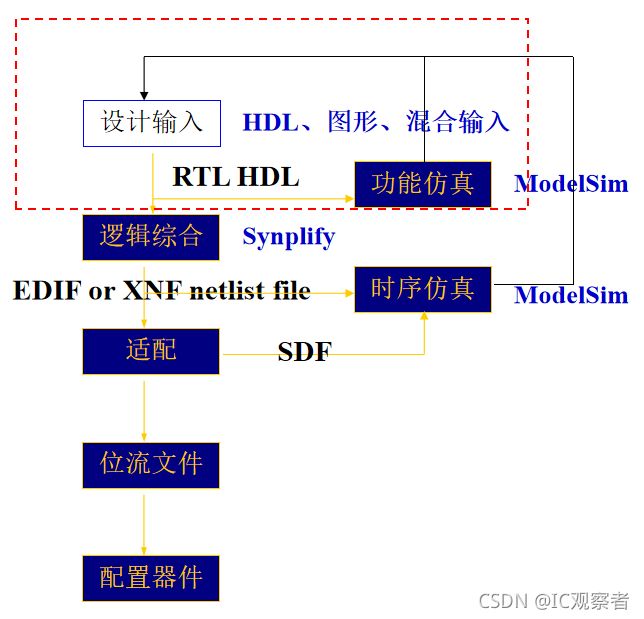

四、FPGA/CPLD设计流程及EDA工具

主要流程有三步:仿真、综合与适配

(1)功能仿真

HDL设计是否实现Spec.功能要求;

采用的EDA工具:Modelsim(Mentor);

(2)逻辑综合

HDL转化为FPGA门级网表;

采用的EDA工具:Synplify(Synplicity)、Precision(Mentor);

(3)时序仿真

不同于前面提到的静态时序仿真STA,是动态时序仿真;

采用的工具:Modelsim;

(4)适配

也称结构综合或FPGA布局布线,是将由综合产生的网表文件配置于指定的目标器件(FPGA/CPLD)中,产生最终的下载文件,如JEDEC、Jam格式的文件。

(5)FPGA/CPLD 器件及其开发工具

FPGA/CPLD 器件提供商:Altera和Xilinx;

FPGA/CPLD 开发的EDA工具一般由器件生产厂家提供,但器件厂家只开发集成开发环境IDE和与器件密切相关的适配工具,功能仿真和综合工具实际是由第三方EDA软件开发商公司提供;

Altera -Quartus II (前身为Maxplus II )

Xilinx -ISE

五、模拟IC设计流程及EDA工具

(1)电路图编辑

常用的工具:Cadence Virtuoso – Schamatic Composer

(2)电路仿真(电路模拟):俗称 SPICE 仿真

常用的工具: Synopsys HSPICE,Cadence Spectre

(3)版图编辑

常用的工具: Cadence Virtuoso – Layout Editor(LE)

(4)版图验证与后仿真

DRC/ LVS: DRC保证版图满足芯片制造厂的设计规则 / LVS证明版图与网表的一致性;

常用的DRC/LVS EDA工具:Mentor Calibre、 Synopsys Hercules;

参数提取:提取版图的连线时延信息(RC Extract);常用的参数提取EDA工具:Synopsys StarRCXT;

版图后仿真:SPICE;

参考文献

1、IC设计流程,从 Spec.到芯片_(数字IC、模拟IC、FPGA设计的流程及EDA工具) - 知乎 (zhihu.com)