DPU特征结构系列(二)一种DPU参考设计

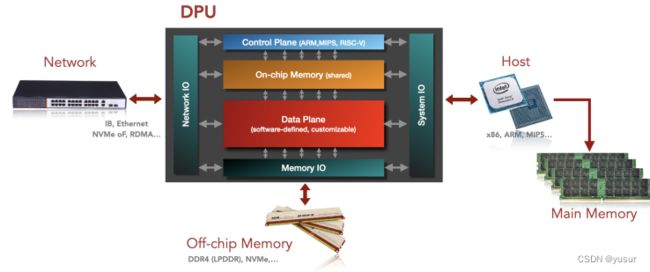

为了满足“数据为中心”的设计理念,本节给出一个通用的DPU参考设计。目前DPU架构的演化比较快,DPU既可以呈现为一个被动设备作为CPU的协处理器,也可以作为一个主动设备,承接Hypervisor的一些功能。尤其是容器技术、虚拟化技术的广泛采用,DPU的角色已经不仅仅是一个协处理器,而是呈现出更多的HOST的特征,比如运行Hypervisor,做跨节点的资源整合,为裸金属和虚拟机提供虚拟网络,数据安全,热迁移等支撑。宏观来看,DPU架构至少可以分为以下几个核心组成部分:

图 DPU架构参考设计

一、控制平面

负责管理、配置,通常由通用处理器核来实现。控制平台负责DPU设备运行管理,以及计算任务和计算资源的配置。运行管理通常包含设备的安全管理和实时监控两个主要功能。在安全管理方面支持支持如信任根、安全启动、安全固件升级以及基于身份验证的容器和应用的生命周期管理等。在设备实时监控方面,对DPU各子系统、数据平面中各处理核动态监测,实时观察设备是否可用、设备中流量是否正常,周期性生成报表,记录设备访问日志核配置修改日志。

计算任务和计算资源配置方面,根据计算任务实施配置数据平面中处理单元间的通路,以及各处理单元参数。根据资源利用情况实时进行任务调度以及在计算单元的映射和部署。同时DPU上层同时会支持多个虚拟机,控制平面在任务部署时还要进行虚拟设备的管理,考虑虚拟机间数据和资源隔离,记录运行状态协助虚拟机热迁移。最后,当DPU集成第三方计算平台,如GPU、FPGA等,还需要参与部分卸载任务调度。

由于控制平面任务多样,灵活性要求较高,算力要求较低,通常由通用处理器核来实现,比如ARM、MIPS等核心。为便于用户统一管理和配置DPU设备,提供较好的可编程性,通常会运行标准Linux应用程序。并且控制平面与数据平面数据交互驱动程序需要进行深度优化,来提升控制平面与数据平面有效地交互,任务调度效率。

二、IO子系统

主要分为三个大类:

(1)系统IO,负责DPU和其他处理平台(如X86、ARM处理器、GPU、FPGA等)或高速外部设备(如SSD)的集成。系统IO通常传输数据量较大对带宽有着极高的要求,因此多基于PCIe来实现。系统IO接口分为两大类:EP(Endpoint)类和RC(Root Complex)类。

EP类接口负责将DPU作为从设备与X86、ARM等处理平台相连接。为了充分利用DPU上的内部资源,此类接口要支持强大的硬件设备虚拟化功能,比如SR-IOV和VirtIO。并且可以灵活地支持多种类型的设备,如NIC、Storage、Compute设备等。

RC类接口负责将DPU作为主设备与加速平台(如GPU、FPGA)或外设(SSD)相连接。通过此种方式将部分数据处理卸载到第三方加速平台GPU、FPGA中处理,通常数据量较大,需要支持较强的DMA方案。

(2)网络IO,负责DPU与高速网络相连接,主要是以太网或者FC为主。为了能应对急剧增加的网络带宽,DPU中通常辅以专门的网络协议处理核来加速网络包的处理。包括L2/L3/L4层的ARP/IP/TCP/UDP网络协议处理、RDMA、数据包交换协议、基本网络虚拟化协议等,可以实现100G以上的网络包线速处理。

(3)主存IO,负责缓存网络IO和系统IO输入输出数据,以及数据平面中间数据结果。也可作为共享内存,实现不同处理核之间的数据通信。目前主存IO主要包含DDR和HBM接口类型,两类接口,DDR可以提供比较大的存储容量,可以提供512GB以上的存储容量;HBM可以提供比较大的存储带宽,可以提供500GB/s以上的带宽。两种存储接口相结合可以满足不同存储容量和带宽的需求,但是需要精细的数据管理,这块也是DPU设计中比较有挑战的。

三、数据平面

主要负责高速数据通路的功能单元的集成,通常集成多个处理核。数据平面的功能主要分为五类:

1)高速数据包处理,主要对接收到的网络数据包进行如OvS(开放式虚拟交换机)解析、匹配和处理,以及RDMA远程数据传输加速等操作,和之前的网络处理器NP功能类似,但是在性能上有更高的要求,处理带宽线速要达到100G、200G甚至400G。同时,在进行有状态数据处理时也有着更高的要求,如TCP协议,要求硬件记录各连接信息,并能实现多连接间无缝切换。

2)虚拟化协议加速,支持SR-IOV、VirtIO 和PV(Para-Virtualization)等虚拟化。支持网络虚拟化VxLAN、Geneve Overlay卸载和VTEP等协议卸载。

3)安全加密,在线IPSec和TLS加密加速,以及多种标准加解密算法和国密算法。并且对于安全算法的处理性能有较高的要求,要达到网络线速,从而不影响其它正在运行的加速操作。

4)流量压缩,对网络数据包,或者要存储的数据,进行实时地数据压缩/解压缩处理,压缩过程中还要完成地址的转换和重映射等操作。或者在线完成数据流变换处理,如面向多媒体流、CDN(内容分发网络)和4K/8K IP视频的 “Packet Pacing” 流量整形加速等。

5)其他算法加速。除了上述网络、安全协议外还要支持NVMe等存储协议,业务相关的处理卸载也呈增长趋势,如大数据分析SQL加速。

四、DPU设计的关键

数据平面是整个DPU设计的关键,也是DPU设计中最有挑战的模块。主要面临四个挑战:

1)数据中心的工作负载复杂多样,数据平面支持的处理核种类要足够多,不仅包括网络、存储、安全和虚拟化等基础设施服务,另外业务相关的处理也在加速向DPU平台卸载。

2)高并发性数据处理,数据中心承载的业务多且复杂,多虚拟机多种类业务并发要求数据平面集成足够数量的核心,规模要达到几百个核心规模。随着数据中心数据量的不断增加,对处理性能提出越来越多的挑战,DPU数据平面在处理核规模上要具有非常强的可扩展性。

3)复杂的片上互联系统,随着DPU数据平面处理核数量的增加,再加之高并发处理线程运行,同时还要兼顾好数据平面数据处理的灵活,这就要求处理核之间的数据交互既要灵活又要兼顾高带宽。处理核之间的数据互联,以及核间的数据一致性成为另一设计难题。

4)高效简易的编程方式,数据中心业务的复杂多变决定了DPU数据平台可编程性的硬性需求。一方面要兼顾计算效率,必须直观表达出并发处理任务,充分利用计算资源。另一方面要兼顾DPU的易用性,尽量采用高级语言进行编程,易于设计、开发和维护。

总之,DPU数据平面需要一种大规模敏捷异构的计算架构。这一部分的实现也处在“百家争鸣”的阶段,各家的实现方式差别较大,有基于通用处理器核的方式,有基于可编程门阵列FPGA的方式,也有基于异构众核的方式,还有待探索。