学习笔记: PCIe 4.0 协议(一)-- 概述

一、什么是PCIe

定义:PCI-Express(peripheral component interconnect express)是一种高速串行计算机扩展总线标准。

传输方式:全双工,TX和RX都采用串行差分信号进行数据传输。

Lane:一条Lane是一对TX差分线加上一对RX差分线,可以有2的n次方条Lane,最多支持32条Lane。

带宽:最高时钟频率是16GHz,则一条Lane的带宽计算 16G * (128/130) / 8 = 1.969GB/s。

发送端将原始数据包封装成协议规定的格式,再转化成串行数据流发出,接收端将串行数据流收集后,按照协议规定逆向解析出原始的数据包

PCIe使用的串行传输方式取代了PCI的并行传输方式,因为并行总线在时钟频率和布线方面会有很多限制,在很多领域高速串行有着取代传统并行的趋势。

二、PCIe结构拓扑

Root Complex: 简称RC,作为PCIe树的根,一方面是连接CPU、Memory子系统,另一方面可以连接多个PCIe端口。

Switch:可以把一个PCIe端口转换成多个PCIe端口。

Endpoint:PCIe终端设备成为Endpoint,它可以挂在RC上,也可以挂在Switch上。

三、PCIe封/拆包流程

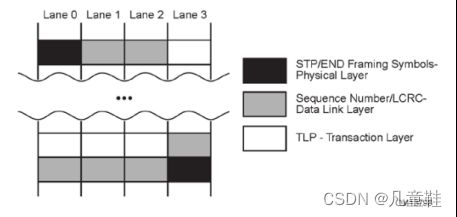

一个原始的数据包(Data)通过如上图三层逻辑(Transaction、Data Link、Physical)的处理变成了一个可以发送的包,通过TX发送给对端,反之,在RX接收的包也可以通过如上图三层逻辑解出原始的数据包(Data)。

- 事务层(Transaction):给Data增加了Header和ECRC。

- 链路层(Data Link):在事务层的基础上增加了Sequence Number和LCRC。

- 物理层(Physical):在链路层的基础上增加了Framing和Framing。

四、各层逻辑功能

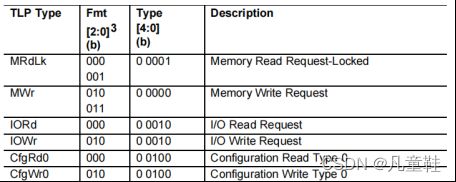

PCIe上的通信是基于Transaction的,根据地址空间不同可以把Transaction分为4类:Memory、I/O、Configuration、Message。

对于发送端所有被标记位保留的域段都必须填0,对于接收端要忽略所有保留域段的值。

4.1 事务层

4.1.1 Prefixes

Prefixes是Header的扩展,和Header有着相同的域段,Prefixes可以省去,也可以有一个或者多个。

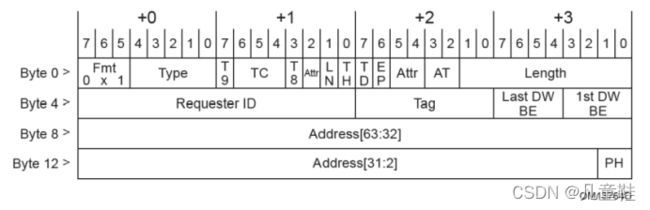

4.1.2 Header--属性

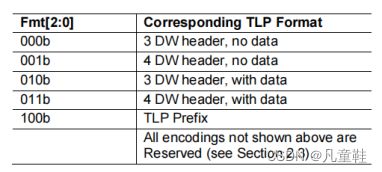

Fmt: Header的格式。

Type:当前Transaction的类型。

TC:传输服务的分类,可以实现差异化的传输服务。

LN:轻量级通知使能。

EP把指定位置Cacheline中的内容拷贝一份到本地,如果有设备更新了Cacheline中的这块内容,就会通知EP你关注的这条Cacheline已被更新,请停止使用你本地的备份。(这种做法主要是为了降低访问延时及带宽占用)

TH:指示Header中是否存在TPH域段。

TD:指示TLP中是否含有Digest。

EP:指示TLP内容是否已经损坏。

Attr[2] & Attr[5:4]:

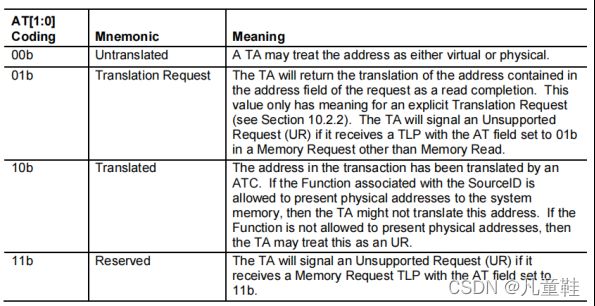

AT:地址类型。

Length:数据的长度是多少DW。

Transaction ID: 由Requester ID和Tag组成Transaction ID,它是一个全局ID。

字节使能: 如果TH有效,THP域段生效(Last DW和1st DW),4位表示传输的第1个或最后一个DW的哪几位有效。(疑问?)

4.1.3 Header--地址

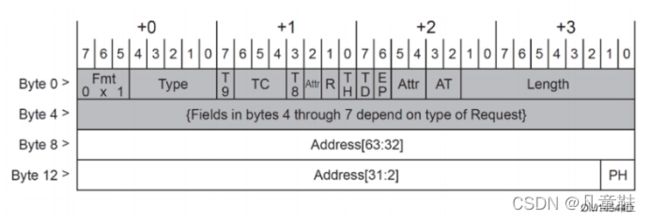

Transaction的路由规则有三种方式:基于地址、基于ID、隐式路由。

1)基于地址:

如果Fmt指示的是4DW,则有64位地址,否则32位地址。

2)基于ID:

通过Bus Number、Device Number、Function Number三个组合起来,来告诉Transaction要发往的目的地。

2)隐式路由:

如果是Message Request,它并不包含Header中并不包含具体的地址或者ID来指定Transaction发往的目的地,所以叫做隐式路由。

4.1.4 Payload

要传输的数据。

4.1.5 Digest

如果Header中的TD有效,会有一个DW的ECRC。

4.2 链路层

主要是为了确保TLP传输的可靠性,在TLP头部增加了序列号,在TLP尾部增加了校验。

Sequence Number:序列号,递增产生,达到最大值后翻转成0。

LCRC:Link层的CRC。

4.3 物理层

4.3.1 Logical Sub-Block

主要实现发送逻辑和接收逻辑。

发送逻辑:

- 根据速率选在8b/10b或128b/130b编码。

- 将要发送的数据根据lane的数量转换成对应的串行数据。

- 增加帧头帧尾,如下图(lane*4的场景)。

- 数据加扰。

接收逻辑:

与发送逻辑过程相反。

4.3.2 Electrical Sub-Block

主要实现差分信号的收发。