软考高级之系统架构师之计算机硬件基础与嵌入式系统

今日:2023年09月07日,离软考高级仅剩57天。

计算机硬件基础

计算机系统中的存储部件通常组织成层次结构,越接近CPU的存储部件访问速度越快。存储速度从快到慢分别是:寄存器组、Cache、内存、Flash。

计算机执行程序时,在一个指令周期的过程中,为了能够从内存中读指令操作码,首先是将程序计数器(PC)的内容送到地址总线上。

一般来说,嵌入式系统通常采用接口中的移位寄存器来实现数据的串/并和并/串转换操作。

CPU的工作频率(主频)包括两个部分:外频与倍频,两者的乘积就是主频。外频,即外部频率,指的是系统总线频率。倍频,倍频系数,倍频系数是指CPU主频与外频之间的相对比例关系。最初CPU主频和系统总线速度是一样的,但CPU的速度越来越快,倍频技术也就相应产生。它的作用是使系统总线工作在相对较低的频率上,而CPU速度可以通过倍频来提升。

CPU访问内存通常是同步方式,CPU与I/O接口交换信息通常是同步方式,CPU与PCI总线交换信息通常是同步方式,I/O接口与打印机交换信息则通常采用基于缓存池的异步方式。

控制器控制整个CPU的工作,包括程序控制、时序控制,其组成包括:

指令寄存器IR:暂存即将执行的指令

程序计数器PC:存放下一条指令执行地址

地址寄存器AR:保存当前CPU所访问的内存地址

指令译码器ID:分析指令操作码

IR

IR:指令寄存器,Instruction Register ,用于暂存当前正在执行的指令。指令寄存器的时钟信号是clk,在clk的上升沿触发。指令寄存器将数据总线送来的指令存入16位的寄存器中,但并不是每次数据总线上的数据都需要寄存,因为数据总线上有时传输指令,有时传输数据。由CPU状态控制器的 Ir_ena信号控制数据是否需要寄存。复位时,指令寄存器被清零。

PC

PC:程序计数器,Program Counter, 是一个中央处理器中的寄存器,用于指示计算机在其程序序列中的位置。用于存放下一条指令所在单元的地址的地方。当执行一条指令时,首先需要根据PC中存放的指令地址,将指令由内存取到指令寄存器中,即,取指令。与此同时,PC中的地址或自动加1或由转移指针给出下一条指令的地址。此后经过分析指令,执行指令。完成第一条指令的执行,而后根据PC取出第二条指令的地址,如此循环,执行每一条指令。

SR

SR:状态寄存器,Status Register,又名条件码寄存器,它是计算机系统的核心部件——运算器的一部分,状态寄存器用来存放两类信息:

- 一类是体现当前指令执行结果的各种状态信息(条件码),如有无进位(CF位)、有无溢出(OV位)、结果正负(SF位)、结果是否为零(ZF位)、奇偶标志位(P位)等;

- 另一类是存放控制信息(PSW,程序状态字寄存器),如允许中断(IF位)、跟踪标志(TF位)等。有些机器中将PSW称为标志寄存器FR(Flag Register)。

GR

GR:通用寄存器,可用于传送和暂存数据,也可参与算术逻辑运算,并保存运算结果。除此之外,它们还各自具有一些特殊功能。汇编语言程序员必须熟悉每个寄存器的一般用途和特殊用途,只有这样,才能在程序中做到正确、合理地使用它们。

总线

总线是一组能为多个部件分时共享的信息传送线,用来连接多个部件并为之提供信息交换通路。所谓共享,指连接到总线上的所有部件都可通过它传递信息;分时性指某一时刻只允许一个部件将数据发送到总线上。因此,共享是通过分时实现的。

串行总线

特点:

- 串行总线有半双工、全双工之分,全双工是一条线发一条线收

- 串行总线适宜长距离传输数据

- 串行总线按位(bit)发送和接收。尽管比按字节(byte)的并行通信慢,但是串口可以在使用一根线发送数据的同时用另一根线接收数据。它很简单并且能够实现远距离通信。比如IEEE488定义并行通行状态时,规定设备线总长不得超过20米,并且任意两个设备间的长度不得超过2米;而对于串口而言,长度可达1200米

- 串口通信最重要的参数是波特率、数据位、停止位和奇偶校验。对于两个进行通行的端口,这些参数必须匹配

- 串行总线的数据发送和接收可以使用多种方式,以中断方式与DMA较为常见。

PCI

PCI是一种局部总线标准,它是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。

JTAG

JTAG是一个调试接口,用来供开发人员调试CPU的工作状态。JTAG软件通过该接口控制CPU来调试CPU以及读写Flash。

VM

虚拟存储器,Virtual Memory,在具有层次结构存储器的计算机系统中,自动实现部分装入和部分替换功能,能从逻辑上为用户提供一个比物理贮存容量大得多,可寻址的主存储器。虚拟存储区的容量与物理主存大小无关,而受限于计算机的地址结构和可用磁盘容量。其页面的置换依据相应的页面置换算法进行,当页面失效时,需要进行数据交换,此时涉及到逻辑地址(虚地址)到辅存物理地址的变换。

CISC & RISC

CISC (Complex Instruction Set Computer,复杂指令集计算机)的基本思想是进一步增强原有指令的功能,用更为复杂的新指令取代原先由软件子程序完成的功能,实现软件功能的硬件化,导致机器的指令系统越来越庞大而复杂。CISC计算机一般所含的指令数目至少300条以上,有的甚至超过500条。

缺点如下:

- 微程序技术是CISC的重要支柱,每条复杂指令都要通过执行一段解释性微程序才能完成,这就需要多个CPU周期,降低机器的处理速度;

- 指令系统过分庞大,从而使高级语言编译程序选择目标指令的范围很大,并使编译程序本身冗长而复杂,从而难以优化编译使之生成真正髙效的目标代码;

- CISC强调完善的中断控制,势必导致动作繁多,设计复杂,研制周期长;

- CISC给芯片设计带来很多困难,使芯片种类增多,出错几率增大,成本提高而成品率降低。

RISC (Reduced Instruction Set Computer,精简指令集计算机)的基本思想是通过减少指令总数和简化指令功能,降低硬件设计的复杂度,使指令能单周期执行,并通过优化编译,提高指令的执行速度,采用硬线控制逻辑,优化编译程序。

RISC的关键技术有:

- 重叠寄存器窗口(overlapping register windows)技术, 首先应用在伯克利的RISC项目中;

- 优化编译技术,RISC使用大量的寄存器,如何 合理分配寄存器、提高寄存器的使用效率,减少访存次数等,都应通过编译技术的优化来实现;

- 超流水及超标量技术,这是RISC为了进一步提高流水线速度而采用的新技术;

- 硬线逻辑与微程序相结合在微程序技术中

DSP

编程DSP芯片是一种具有特殊结构的微处理器,为了达到快速进行数字信号处理的目的,DSP芯片一般都采用特殊的软硬件结构:

1) 哈佛结构

DSP采用哈佛结构,将存储器空间划分成两个,分别存储程序和数据。它们有两组总线连接到处理器核,允许同时对它们进行访问,每个存储器独立编址,独立访问。这种安排将处理器的数据吞吐率加倍,更重要的是同时为处理器核提供数据与指令。在这种布局下,DSP得以实现单周期的MAC指令。在哈佛结构中,由于程序和数据存储器在两个分开的空间中,因此取指和执行能完全重叠运行。

2) 流水线

与哈佛结构相关,DSP芯片广泛采用2-6级流水线以减少指令执行时间,从而增强处理器的处理能力。这可使指令执行能完全重叠,每个指令周期内,不同的指令都处于激活状态。

3) 独立的硬件乘法器

在实现多媒体功能及数字信号处理的系统中,算法的实现和数字滤波都是计算密集型的应用。在这些场合,乘法运算是数字处理的重要组部分,是各种算法实现的基本元素之一。乘法的执行速度越快,DSP处理器的性能越高。相比与一般的处理器需要30-40个指令周期,DSP芯片的特征就是有一个专用的硬件乘法器,乘法可以在一个周期内完成。

4) 特殊的DSP指令

采用特殊的指令,专为数字信号处理中的一些常用算法优化。这些特殊指令为一些典型的数字处理提供加速,可以大幅提高处理器的执行效率。使一些高速系统的实时数据处理成为可能。

5) 独立的DMA总线和控制器

有一组或多组独立的DMA总线,与CPU的程序、数据总线并行工作。在不影响CPU工作的条件下,DMA的速度已经达到800MB/S以上。这在需要大数据量进行交换的场合可以减小CPU的开销,提高数据的吞吐率。提高系统的并行执行能力。

6) 多处理器接口

使多个处理器可以很方便的并行或串行工作以提高处理速度。

7) JTAG,Joint Test Action Group,标准测试接口(IEEE 1149标准接口),便于对DSP作片上的在线仿真和多DSP条件下的调试。

8) 快速的指令周期

哈佛结构,流水线操作,专用的硬件乘法器,特殊的DSP指令再加上集成电路的优化设计,可使DSP芯片的指令周期在10ns以下。快速的指令周期可以使DSP芯片能够实时实现许多DSP应用。

MMU

Memory Management Unit,即存储器管理单元,是用来管理虚拟内存系统的器件。MMU通常是CPU的一部分,本身有少量存储空间存放从虚拟地址到物理地址的匹配表。此表称作TLB(转换旁置缓冲区)。所有数据请求都送往MMU,由MMU决定数据是在RAM内还是在大容量存储器设备内。如果数据不在存储空间内,MMU将产生页面错误中断。 MMU的两个主要功能是将虚地址转换成物理地址,控制存储器存取允许。MMU关掉时,虚地址直接输出到物理地址总线。Cortex-M3处理器采用ARMv7-M架构,它包括所有的16位Thumb指令集和基本的32位Thumb-2指令集架构。Cortex-M3支持线程模式和处理模式。在复位时处理器进入线程模式,异常返冋时也会进入该模式,特权和用户(非特权)模式代码能够在线程模式下运行。出现异常模式时处理器进入处理模式,在处理模式下,所有代码都是特权访问的。μC/OS-II可以运行在Cortex-M3处理器上。

MPU

嵌入式微处理器(MPU)是嵌入式系统硬件层的核心,大多工作在为特定用户群专用设计的系统中,它将通用CPU中许多由板卡完成的任务集成在芯片内部,从而有利于嵌入式系统在设计时趋于小型化,同时还具有很高的效率和可靠性。嵌入式微控制器(Embedded Microcontroller Unit,EMCU)的典型代表是单片机,也称嵌入式微控制器。它体积小,结构紧凑,作为一个部件安装在所控制的装置中,主要执行信号控制的功能。

数字信号处理器(digital signal processor)由大规模或超大规模集成电路芯片组成,是用来完成某种信号处理任务的处理器。它是为适应高速实时信号处理任务的需要而逐渐发展起来的。随着集成电路技术和数字信号处理算法的发展,数字信号处理器的实现方法也在不断变化,处理能力不断提高。

片上系统(System-on-a-chip)指的是在单个芯片上集成一个完整的系统,一般包括CPU、存储器,以及外围电路等。SOC是与其他技术并行发展的,如绝缘硅(SOI),它可以提供增强的时钟频率,从而降低微芯片的功耗。

RAID

另起一篇,参考计算机基础之RAID技术。

DMA

Direct Memory Access,DMA方式是一种不经过CPU而直接在外设与内存间进行的数据交换控制方式。在DMA模式下,CPU只须向DMA控制器下达指令,让DMA控制器来处理数据的传送,数据传送完之后再把信息反馈给CPU即可。

指标

吞吐率

指令流水线的吞吐率定义为:吞吐率TP=指令数 / 执行时间。

嵌入式系统

嵌入式系统是以应用为中心,以计算机技术为基础,可以适应不同应用对功能、可靠性、成本、体积和功耗等方面的要求,集可配置可裁剪的软硬件于一体的专用计算机系统。

组成部分:

- 嵌入式硬件平台

- 相关支撑硬件

- 嵌入式操作系统

- 支撑软件

- 应用软件

嵌入式系统中采用中断方式实现输入输出的主要原因是能对突发事件做出快速响应。在中断时,CPU断点信息一般保存到栈中。

硬件抽象层是位于操作系统内核与硬件电路之间的接口层,其目的在于将硬件抽象化。它隐藏特定平台的硬件接口细节,为操作系统提供虚拟硬件平台,使其具有硬件无关性,可在多种平台上进行移植。

嵌入式操作系统

嵌入式操作系统是应用于嵌入式系统,实现软硬件资源的分配,任务调度,控制、协调并发活动等的操作系统软件。它除了具有一般操作系统最基本的功能如多任务调度、同步机制等之外,通常还会具备以下适用于嵌入式系统的特性:

- 面向应用,可以进行检查和移植,以支持开放性和可伸缩性的体系结构;

- 强实时性,以适应各种控制设备及系统;

- 硬件适用性,对于不同硬件平台提供有效的支持并实现统一的设备驱动接高可靠性,运行时无须用户过多干预,并处理各类事件和故障;

- 编码体积小,通常会固化在嵌入式系统有限的存储单元中。

软件设计层面的功耗控制主要可以从以下方面展开:

- 软硬件协同设计,即软件的设计要与硬件的匹配,考虑硬件因素

- 编译优化,采用低功耗优化的编译技术

- 从算法角度优化减少系统持续运行时间

- 用中断代替查询

- 电源有效管理

在嵌入式系统开发中,由于嵌入式设备不具备足够的处理器能力和存储空间,程序开发一般用PC (宿主机)来完成,然后将可执行文件下载到嵌入式系统(目标机)中运行。 当宿主机与目标机的机器指令不同时,就需要交叉工具链(指编译、汇编、链接等一整套工具),如交叉编译器,在宿主机上生成目标机的可执行代码。

初始化

嵌入式系统初始化过程可以分为3个主要环节,按照自底向上、从硬件到软件的次序依次为:片级初始化、板级初始化和系统级初始化

- 片级初始化:完成嵌入式微处理器的初始化,包括设置嵌入式微处理器的核心寄存器和控制寄存器、嵌入式微处理器核心工作模式和嵌入式微处理器的局部总线模式等。片级初始化把嵌入式微处理器从上电时的默认状态逐步设置成系统所要求的工作状态。这是一个纯硬件的初始化过程。

- 板级初始化:完成嵌入式微处理器以外的其他硬件设备的初始化。另外,还需设置某些软件的数据结构和参数,为随后的系统级初始化和应用程序的运行建立硬件和软件环境。这是一个同时包含软硬件两部分在内的初始化过程。

- 系统初始化:该初始化过程以软件初始化为主,主要进行操作系统的初始化。BSP将对嵌入式微处理器的控制权转交给嵌入式操作系统,由操作系统完成余下的初始化操作,包含加载和初始化与硬件无关的设备驱动程序,建立系统内存区,加载并初始化其他系统软件模块,如网络系统、文件系统等。最后,操作系统创建应用程序环境,并将控制权交给应用程序的入口。

嵌入式开发

嵌入式软件开发

嵌入式硬件开发

RTOS

Real-Time Operating System,

任务是RTOS中最重要的操作对象,每个任务在RTOS的调度下由CPU分时执行。任务的调度目前主要有时间分片式、轮流查询式和优先抢占式三种,不同的RTOS可能支持其中一种或几种,其中优先抢占式对实时性的支持最好。

在非实时系统中,调度的主要目的是缩短系统平均响应时间,提高系统资源的利用率,或优化某一项指标;而实时系统中调度的目的则是要尽可能地保证每个任务满足他们的时间约束,及时对外部请求做出响应。

调度

调度:给定一组实时任务和系统资源,确定每个任务何时何地执行的整个过程。

-

抢占式调度:通常是优先级驱动的调度,如 uCOS。优点是实时性好 、反应快,调度算法相对简单,可以保证高优先级任务的时间约束;缺点是上下文切换多。

-

非抢占式调度:通常是按时间片分配的调度,不允许任务在执行期间被中断,任务一旦占用处理器就必须执行完毕或自愿放弃,如WinCE。优点是上下文切换少;缺点是处理器有效资源利用率低,可调度性不好。

-

静态表驱动策略:系统在运行前根据各任务的时间约束及关联关系,采用某种搜索策略生成一张运行时刻表,指明各任务的起始运行时刻及运行时间。

-

优先级驱动策略:按照任务优先级的高低确定任务的执行顺序。

实时任务分类:周期任务、偶发任务、非周期任务。

实时系统的通用结构模型:数据采集任务实现传感器数据的采集,数据处理任务处理采集的数据,并将加工后的数据送到执行机构管理任务控制机构执行。

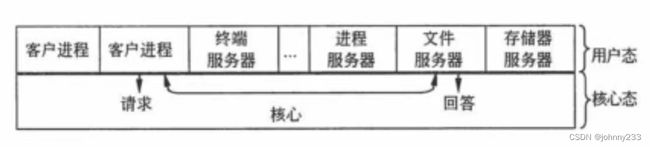

微内核体系

其基本思想是把操作系统中与硬件直接相关的部分抽取出来作为一个公共层,称之为硬件抽象层(HAL)。这个硬件抽象层其实就是种虚拟机,它向所有基于该层的其他层通过API接口提供一系列标准服务。在微内核中只保留处理机调度、存储管理和消息通讯等少数几个组成部分,将传统操作系统内核中的 一些组成部分放到内核之外来实现。如传统操作系统中的文件管理系统、进程管理、设备管理、虚拟内存和网络等内核功能都放在内核外作为一个独立的子系统来实现。因此, 操作系统的大部分代码只要在一种统一的硬件体系结构上进行设计即可。

主要特点:

- 内核非常小,许多操作系统服务不属于内核,而是运行在内核之上的,这样, 当髙层模块更新时内核无须重新编译。

- 有一个硬件抽象层,内核能方便地移植到其他的硬件体系结构中。因为当需要移植到新的软件或硬件环境中时,只需对与硬件相关的部分稍加修改即可把微内核嵌入到新的硬件环境中,在多数情况下并不需要移植外部服务器或客户应用。

- 灵活性和扩展性。如果要实现另一个视图,可以增加一个外部服务器。若要想扩展功能,可以增加和扩展内部服务器。

设计

嵌入式系统的核心技术

- 处理器技术

- 通用处理器

通用性强,上市时间快,成本低。对于某些应用可能性能较差。 - 单用途处理器

对某些应用程序性能更好,但是灵活性差。设计成本高,数量大时可降低成本。 - 专用处理器

体积更小,成本更低

- IC技术

- 全定制 VLSI

在全定制IC技术中,需要根据特定的嵌入式系统的数字实现来优化各层设计人员从晶体管的版图尺寸、位置、连线开始设计,已达到芯片面积利用率高、速度快、功耗低的最优化性能。利用掩膜在制造厂生产实际芯片,全定制的IC设计也通常称为大规模集成电路设计(VLSI),具有很高的成本,很长的制造时间,适用于大量或者对性能要求很严格的应用。 - 半定制 ASIC

半定制ASIC是一种约束型设计方法,包括门阵列设计法和标准单元设计法。通过在芯片上制作一些具有通用性的单元元件和元件组的半成品硬件,设计者仅需要考虑电路的逻辑功能和各功能模块之间的合理连接即可。这种设计方法灵活方便,性价比高,缩短设计周期,提高成品率。 - 可编程 ASIC

可编程期间中所有的各层都已存在,设计完成后,在实验室里即可烧制出设计的芯片,不需要IC厂家的参与,开发周期显著缩短。可编程ASIC具有较低的成本,功耗大,速度慢。

- 设计/验证技术

嵌入式系统设计技术主要包括硬件设计和软件设计技术:

硬件设计技术包含:

- 芯片级设计技术

- 电路板级设计技术

嵌入式系统的设计模型

- 状态机模型

- 数据流模型

- 并发进程模型

- 面向对象模型

嵌入式数据库

嵌入式数据库实际上和内存数据库比较相似,与应用程序运行在同一个进程。内存数据库参考内存数据库Apache Derby、H2。

特性:嵌入式、移动性、伸缩性、实时性。