服务器的CPLD的上下电控制时序及源代码实现

服务器的CPLD的上下电控制时序及源代码实现:

在此讲解一下服务器的CPLD的上下电控制时序及代码的实现,请大家点赞!实际项目应用!

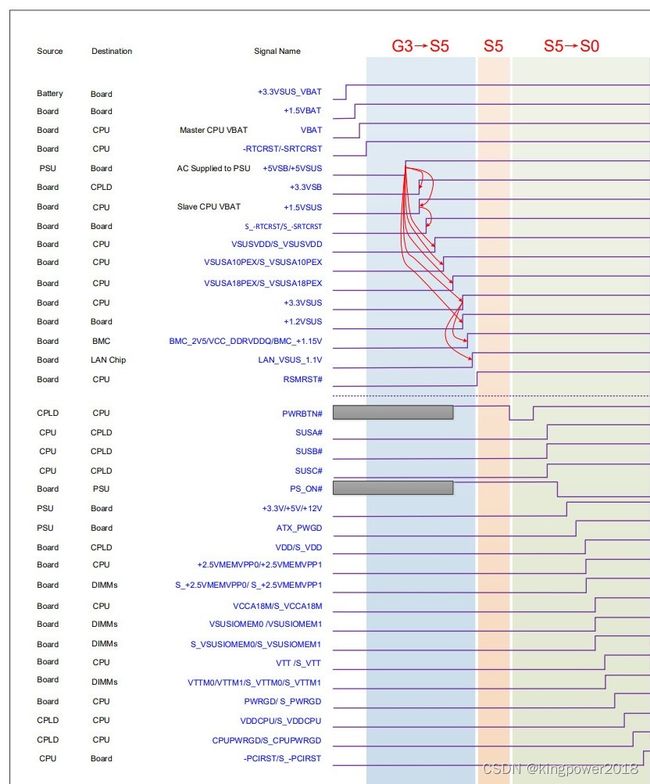

上电时序图:

下电时序图:

源代码实现:

提示:下面是上面上电下电时序的逻辑代码实现,请参考:

/********************************************************

服务器上下电管理模块

********************************************************/

module poweron_poweroff_manager(

input clk,

input present_n, //1 在位信号

input s_present_n, //1* 在位信号

//input p5Vsus_PGood, //6 +5Vsus_PGood

input cpld_rsmrst_n, //7 3.3VSBVRM

output reg front_bp_Pwr_Enabled, // repeat 28

output reg ocp_aux_Pwr_Enabled, // repeat 19

input VsusVdd_PGood, //9

input s_VsusVdd_PGood, //9

//output reg VsusVdd_Enabled, //8 [disabled]

input Vsusa18pex_PGood, //13 Vsus18V_ON--cpld VsusA18PEX_PGood

input s_Vsusa18pex_PGood, //13 S_DUT_PRESENT & S_VsusA18PEX_PGood

//output reg Vsus18v_on, //12 S_Vsus18V_Enabled,Vsus18V_ON--cpu1 [disabled]

//output reg Vsus10v_on, //10 [disabled]

input s_Vsusa10pex_PGood, //11 S_DUT_PRESENT & Vsus10V_ON

input Vsusa10pex_PGood, //11 VsusA10PEX_PGood

//output reg Vsus33v_on, //14 Vsus33v_on [disabled]

input p33Vsus_PGood, //15 p33Vsus_PGood

input bmc_p1p15v_PGood, //18 bmc_p1p15v_PGood

input lan_Vsus_1p1v_PGood, //19 lan_Vsus_1p1v

//output reg rsmrst_n, //20 output rsmrst_n [disabled]

output reg rsmrst_d, //21 output rsmrst_d

input bmc_PwrButn_out_n, //23 bmc_PwrButn_out_n

output reg dPwr_Butn, //24 dPwr_Butn

output reg s_dPwr_Butn, //24 s_dPwr_Butn

input dsusc, //25 dsusc

output atx_Op, //26 atx_Op

input psu_Pwr_ok, //27 psu_Pwr_ok

input psu_prsnt_n, //3 psu_prsnt_n

input front_bp_PwrGood, // 29

input ocp_nic_Pwr_good, // 20

output reg ocp_main_Pwr_Enabled, // 28

output reg Vdd_Op, //28 Vdd_Op

output reg s_Vdd_Op, //28 Vdd_Op

output reg p2p5vmem_Op, //28 p2p5vmem_Op

input Vdd_PGood, //29 Vdd_PGood input 改成output reg for test

input s_Vdd_PGood, //29 s_Vdd_PGood

input p2p5vmemvpp01_PGood, //29 p2p5vmemvpp01_PGood

input s_p2p5vmemvpp01_PGood, //29 s_p2p5vmemvpp01_PGood

output reg Vsusiomem_Op, //30 Vsusiomem_Op

output reg s_Vsusiomem_Op, //30 s_Vsusiomem_Op

output reg vcca18m_Op, //30 vcca18m_Op

output reg s_vcca18m_Op, //30 s_vcca18m_Op

input Vsusiomem01_PGood, //31 Vsusiomem_PGood

input s_Vsusiomem01_PGood, //31 s_Vsusiomem_PGood

input vcca18m_PGood, //31 vcca18m_PGood

input s_vcca18m_PGood, //31 s_vcca18m_PGood

output reg vtt_Op, //32 vtt_Op

input vttm_PGood, //32

input vtt_PGood, //33 vtt_PGood

input s_vtt_PGood, //33 s_vtt_PGood

output reg pwrGood, //34 pwrGood

output reg s_PwrGood, //34 s_PwrGood

output reg vddcpu_Op, //35 vddcpu_Op

output reg s_vddcpu_Op, //35 s_vddcpu_Op

input avr_ready, //38 avr_ready

input s_avr_ready, //38 s_avr_ready

output reg cpupwrGood, //39 cpupwrGood

output reg s_cpupwrGood //39 s_cpupwrGood

);

reg front_bp_Pwr_Enabled = 1'b0;

reg ocp_aux_Pwr_Enabled = 1'b0;

//--------------------------------------------------------------

reg rsmrst_d = 1'b1; //默认RSMRST_D赋值为1,高电平

//--------------------------------------------------------------

reg dPwr_Butn = 1'b1; //-Pwr_Butn=1 初始化状态1

reg s_dPwr_Butn = 1'b1; //S_-Pwr_Butn=1 初始化状态1

//--------------------------------------------------------------

reg atx_Op = 1'b0;

reg ocp_main_Pwr_Enabled = 1'b0;

reg Vdd_Op = 1'b0;

reg s_Vdd_Op = 1'b0;

reg p2p5vmem_Op = 1'b0;

reg Vsusiomem_Op = 1'b0;

reg s_Vsusiomem_Op = 1'b0;

reg vcca18m_Op = 1'b0;

reg s_vcca18m_Op = 1'b0;

reg vtt_Op = 1'b0;

reg pwrGood = 1'b0;

reg s_PwrGood = 1'b0;

reg vddcpu_Op = 1'b0;

reg s_vddcpu_Op = 1'b0;

reg cpupwrGood = 1'b0;

reg s_cpupwrGood = 1'b0;

//--------------------------------------------------------------

reg f_pw_on = 1'b0; //开机上电完成标志

reg f_pw_off = 1'b0; //关机下电完成标志

reg [5:0] curr_state =0; //当前状态机

reg [5:0] n_state =0; //状态机

reg bmc_PwrButn_status = 1'b0; //按键状态

reg bmc_PwrButn_chgflag = 1'b0; //按键改变标志

reg f_keychange = 1'b0; //键变化标志

reg f_Bs_reboot = 1'b0; //BIOS重启标志

reg f_dsuslowtimer = 1'b0; //dsusc低计时标志

//--------------------------------------------------------------

reg f_poweron_2s = 1'b0; //开机延时2秒标志

reg ocp_nic_Pwr_good_r0 = 1'b0; //存 ocp_nic_Pwr_good 状态

reg dsusc_r0 = 1'b0; //存 dsusc 状态

reg psu_Pwr_ok_r0 = 1'b0; //存 psu_Pwr_ok 状态

reg front_bp_PwrGood_r0 = 1'b0; //存 front_bp_PwrGood状态

reg Vdd_PGood_r0 = 1'b0; //存 Vdd_PGood状态

reg s_Vdd_PGood_r0 = 1'b0; //存 s_Vdd_PGood状态

reg p2p5vmemvpp01_PGood_r0 = 1'b0; //存 p2p5vmemvpp01_PGood状态

reg s_p2p5vmemvpp01_PGood_r0 = 1'b0; //存 s_p2p5vmemvpp01_PGood状态

reg Vsusiomem01_PGood_r0 = 1'b0; //存 Vsusiomem_PGood状态

reg s_Vsusiomem01_PGood_r0 = 1'b0; //存 s_Vsusiomem_PGood状态

reg vcca18m_PGood_r0 = 1'b0; //存 vcca18m_PGood状态

reg s_vcca18m_PGood_r0 = 1'b0; //存 s_vcca18m_PGood状态

reg vttm_PGood_r0 = 1'b0; //存 vttm_PGood状态

reg vtt_PGood_r0 = 1'b0; //存 vtt_PGood状态

reg s_vtt_PGood_r0 = 1'b0; //存 s_vtt_PGood状态

reg avr_ready_r0 = 1'b0; //存 avr_ready状态

reg s_avr_ready_r0 = 1'b0; //存 s_avr_ready状态

//--------------------------------------------------------------

reg bmc_rstButn_keydown_flag = 1'b0; //BMC 按键按下标志

reg bmc_rstButn_feedback_delay_flag = 1'b0; //BMC 按键按下CPLD反馈脉冲延时标志

reg p33Vsus_PGood_f = 1'b0; //记录p33Vsus_PGood状态

//-----------------------------------------------------------------------------------------------------------

//即时跟踪更新当前的状态机

always @(posedge clk or negedge cpld_rsmrst_n )begin

if(!cpld_rsmrst_n)begin

curr_state <= 0;

end

else begin

curr_state <= n_state;

end

end

//-----------------------------------------------------------------------------------------------------------

//-----------------------------------------------------------------------------------------------------------

// 计时2S,开机复位2秒所有电源稳定了才进行操作

reg [26:0] count0; //计时5s

always@(posedge clk or negedge cpld_rsmrst_n)begin

if(!cpld_rsmrst_n)begin

count0 <= 0;

f_poweron_2s <= 1'b0;

end

else if(f_pw_off == 1'b1 && curr_state > 0 && f_poweron_2s == 1'b1) begin

count0 <= 0;

f_poweron_2s <= 1'b0;//关机2秒状态清0(关机后需要将开机复位2秒标志清0)

end

else if(f_pw_off == 1'b1 && curr_state == 0) begin

if(count0 == 27'd9999999)begin //关机重新开机计时0.2S

f_poweron_2s <= 1'b1;

count0 <= 0;

end

else count0 <= count0+1;

end

else if(cpld_rsmrst_n == 1'b1 && curr_state == 0 && f_pw_on == 1'b0 && f_pw_off == 1'b0) begin

if(count0 == 27'd99999999)begin //上电开机计时2S

f_poweron_2s <= 1'b1;

count0 <= 0;

end

else count0 <= count0+1;

end

else begin

count0 <= 0;

f_poweron_2s <= 1'b0;

end

end

//-----------------------------------------------------------------------------------------------------------

//-----------------------------------------------------------------------------------------------------------

//Power on & Power off //change

//上电 & 下电处理过程

//-----------------------------------------------------------------------------------------------------------

always @(posedge clk or negedge cpld_rsmrst_n )begin

if(!cpld_rsmrst_n)begin

n_state <= 0; //状态机清0

bmc_rstButn_feedback_delay_flag <= 1'b0; //清起延时标志0

f_pw_on <= 1'b0; //clear f_pw_on=0

p33Vsus_PGood_f <= 1'b0; //p33Vsus_PGood_f=0

rsmrst_d <= 1'b1; //默认RSMRST_D赋值为1,高电平

end

else begin

//rsmrst_d <= 1'b0; //将RSMRST_D 拉低(测试)

if(flag11_5ms == 1'b1 && curr_state < 27)begin //延时2S ==> 改为5ms

rsmrst_d <= 1'b0; //将RSMRST_D 拉低

ocp_aux_Pwr_Enabled <= 1'b1; //开启ocp_aux_Pwr_Enabled

end

if(cpld_rsmrst_n == 1'b1) begin

if(bmc_PwrButn_status != bmc_PwrButn_out_n) begin

bmc_PwrButn_status <= bmc_PwrButn_out_n;

bmc_PwrButn_chgflag <= 1'b1; //bmc_PwrButn_chgflag=1

f_keychange <= 1'b1; //keychange=1

end

if(f_dsuslowtimer == 1'b1 && flag50_4s == 1'b1 && curr_state == 0) begin

f_dsuslowtimer <= 1'b0;

f_Bs_reboot <= 1'b1; //reboot=1

end

end

if(cpld_rsmrst_n == 1'b1 && curr_state < 27 && f_pw_on == 1'b0) begin

//在cpld_rsmrst_n为1时,还没有开机状态下跟随bmcButn的状态变化

if (bmc_PwrButn_chgflag == 1'b1)begin

bmc_PwrButn_chgflag <= 1'b0; //bmc_PwrButn_chgflag=0

if (bmc_PwrButn_out_n == 1'b1)begin

dPwr_Butn <= 1'b1; //-Pwr_Butn=1

s_dPwr_Butn <= 1'b1; //S_-Pwr_Butn=1

end

else begin

dPwr_Butn <= 1'b0; //-Pwr_Butn=0

s_dPwr_Butn <= 1'b0; //S_-Pwr_Butn=0

end

end

end

if(cpld_rsmrst_n == 1'b1 && curr_state == 40 && f_pw_on == 1'b1) begin

//在cpld_rsmrst_n为1时,还没有开机状态下跟随bmcButn的状态变化[长按关机]

if (bmc_PwrButn_chgflag == 1'b1)begin

bmc_PwrButn_chgflag <= 1'b0; //bmc_PwrButn_chgflag=0

if(bmc_PwrButn_out_n == 1'b1)begin

dPwr_Butn <= 1'b1; //-Pwr_Butn=1

s_dPwr_Butn <= 1'b1; //S_-Pwr_Butn=1

end

else begin

dPwr_Butn <= 1'b0; //-Pwr_Butn=0

s_dPwr_Butn <= 1'b0; //S_-Pwr_Butn=0

end

end

end

case(curr_state)

0:begin //开机延时2秒使电源稳定再进入处理

if (f_poweron_2s == 1'b1 && f_keychange == 1'b1 && (bmc_PwrButn_out_n == 1'b0 || (f_Bs_reboot == 1'b1 && dsusc == 1'b1))) begin

f_pw_off <= 1'b0; //f_pw_off=0清关机状态0

f_keychange <= 1'b0; //keychange=0清0

f_Bs_reboot <= 1'b0; //reboot=0

f_dsuslowtimer <= 1'b0;

n_state <= 18; //18Step

end

end

18:begin

if (cpld_rsmrst_n == 1'b1)begin

n_state <= 19; //19Step

end

end

19:begin

if (cpld_rsmrst_n == 1'b1)begin

n_state <= 20; //20Step

end

end

20:begin //读取1个输入状态

ocp_nic_Pwr_good_r0 <= ocp_nic_Pwr_good; //存 ocp_nic_Pwr_good 状态

//n_state <= 21; //21Step

n_state <= 25; //25Step 直接跳到=25

end

21:begin

n_state <= 22; //22Step 暂无逻辑,直接跳过

end

22:begin

n_state <= 23; //23Step 暂无逻辑,直接跳过

end

23:begin

//if(bmc_rstButn_keydown_flag == 1'b1)begin

// n_state <= 24; //24Step

//end

//由于 bmc_rstButn_keydown_flag信号由BMC输出没有,上述逻辑暂改为 直接跳过

n_state <= 24; //24Step 暂无逻辑,直接跳过

end

24:begin

//if(bmc_rstButn_keydown_flag == 1'b1)begin

// dPwr_Butn <= 1'b0; //-Pwr_Butn=0

// s_dPwr_Butn <= 1'b0; //S_-Pwr_Butn=0

// bmc_rstButn_feedback_delay_flag <= 1'b1; //置起延时标志1

//end

//if(flag24_20ms == 1'b1)begin //延时20mS

// dPwr_Butn <= 1'b1; //-Pwr_Butn=1

// s_dPwr_Butn <= 1'b1; //S_-Pwr_Butn=1

// n_state <= 25; //25Step

//end

//由于 bmc_rstButn_keydown_flag信号由BMC输出没有,上述逻辑暂改为 直接清0后跳过

//dPwr_Butn <= 1'b0; //-Pwr_Butn=0

//s_dPwr_Butn <= 1'b0; //S_-Pwr_Butn=0

n_state <= 25; //25Step 暂无逻辑,直接跳过

end

25:begin //读取1个输入状态

dsusc_r0 <= dsusc; //存 dsusc 状态

n_state <= 26; //26Step 检测-SUSC 合并到26Step

end

26:begin //If -SUSC=1&& DUT_PRESENT_N=0, ATX_ON+=1

if(dsusc == 1'b1 && present_n == 1'b0)begin

//由于 present_n信号暂时没有,上述逻辑暂改变了

//if(dsusc == 1'b1)begin

atx_Op <= 1'b1; //开启 ATX_ON+=1

n_state <= 27; //27Step

end

end

27:begin //读取1个输入状态

f_keychange <= 1'b0; //keychange=0清0

//---------------------------------恢复Butn状态

dPwr_Butn <= 1'b1; //-Pwr_Butn=1

s_dPwr_Butn <= 1'b1; //S_-Pwr_Butn=1

//---------------------------------

psu_Pwr_ok_r0 <= psu_Pwr_ok; //存 PSU_Pwr_OK 状态

if(flag27_20ms == 1'b1)begin //延时20mS

n_state <= 28; //28Step

end

end

28:begin

if(psu_Pwr_ok == 1'b1)begin

front_bp_Pwr_Enabled <= 1'b1; //开启 FRONT_BP_Pwr_Enabled=1

ocp_main_Pwr_Enabled <= 1'b1; //OCP_MAIN_Pwr_Enabled=1

if(flag28_5ms == 1'b1)begin

Vdd_Op <= 1'b1; //set Vdd_ON+=1

p2p5vmem_Op <= 1'b1; //set +2.5VMEM_ON+=1

end

if(flag282_5ms == 1'b1 && s_present_n == 1'b0)begin //第二CPU在位

s_Vdd_Op <= 1'b1; //set S_Vdd_ON+=1

end

if(flag28_5ms == 1'b1 && (flag282_5ms == 1'b1 || s_present_n == 1'b1))begin

//上面2个信号全部置起来了再进行下一步

n_state <= 29; //29Step

end

end

end

29:begin //读取5个输入状态

front_bp_PwrGood_r0 <= front_bp_PwrGood; //存 front_bp_PwrGood状态

Vdd_PGood_r0 <= Vdd_PGood; //存 Vdd_PGood状态

s_Vdd_PGood_r0 <= s_Vdd_PGood; //存 s_Vdd_PGood状态

p2p5vmemvpp01_PGood_r0 <= p2p5vmemvpp01_PGood; //存 p2p5vmemvpp01_PGood状态

s_p2p5vmemvpp01_PGood_r0 <= s_p2p5vmemvpp01_PGood;//存 s_p2p5vmemvpp01_PGood状态

if(flag29_20ms == 1'b1)begin //延时20mS

n_state <= 30; //30Step

end

end

30:begin

//If +2.5VMEMVPP01_PGood=1, VsusIOMEM_ON+=1

//If S_+2.5VMEMVPP01_PGood=1, S_VsusIOMEM_ON+=1

//If Vdd_PGood=1, VCCA18M_ON+=1

//If S_Vdd_PGood=1, S_VCCA18M_ON+=1

if(p2p5vmemvpp01_PGood == 1'b1) begin

Vsusiomem_Op <= 1'b1; //set VsusIOMEM_ON+=1

end

if(s_p2p5vmemvpp01_PGood == 1'b1 && s_present_n == 1'b0) begin //第二CPU在位

s_Vsusiomem_Op <= 1'b1; //set S_VsusIOMEM_ON+=1

end

if(Vdd_PGood == 1'b1) begin

vcca18m_Op <= 1'b1; //set VCCA18M_ON+=1

end

if(s_Vdd_PGood == 1'b1 && s_present_n == 1'b0) begin //第二CPU在位

s_vcca18m_Op <= 1'b1; //set S_VCCA18M_ON+=1

end

if(p2p5vmemvpp01_PGood == 1'b1 && Vdd_PGood == 1'b1 && ((s_p2p5vmemvpp01_PGood == 1'b1 && s_Vdd_PGood == 1'b1) || s_present_n == 1'b1)) begin

//上面4个信号全部置起来了再进行下一步

n_state <= 31; //31Step

end

end

31:begin //读取4个输入状态

Vsusiomem01_PGood_r0 <= Vsusiomem01_PGood; //存 Vsusiomem_PGood状态

s_Vsusiomem01_PGood_r0 <= s_Vsusiomem01_PGood; //存 s_Vsusiomem_PGood状态

vcca18m_PGood_r0 <= vcca18m_PGood; //存 vcca18m_PGood状态

s_vcca18m_PGood_r0 <= s_vcca18m_PGood; //存 s_vcca18m_PGood状态

if(flag31_20ms == 1'b1)begin //延时20mS

n_state <= 32; //32Step

end

end

32:begin

//If VCCA18M_PGood=1, VTT_ON+=1

vttm_PGood_r0 <= vttm_PGood; //存 vttm_PGood状态

if(vcca18m_PGood == 1'b1) begin

vtt_Op <= 1'b1; //set VTT_ON+=1

n_state <= 33; //33Step

end

end

33:begin //读取两个输入状态

vtt_PGood_r0 <= vtt_PGood; //存 vtt_PGood状态

s_vtt_PGood_r0 <= s_vtt_PGood; //存 s_vtt_PGood状态

if(flag33_20ms == 1'b1)begin //延时20mS

n_state <= 34; //34Step

end

end

34:begin

//If VTTM_PGood=1 & S_VTT_PGood=1, S_PwrGood=1

//If VTTM_PGood=1 & VTT_PGood=1, PWRGood=1

//if(vttm_PGood == 1'b1 && vtt_PGood == 1'b1) begin

if(vtt_PGood == 1'b1) begin

pwrGood <= 1'b1; //set PWRGood=1

end

//if(vttm_PGood == 1'b1 && s_vtt_PGood == 1'b1 && s_present_n == 1'b0) begin //第二CPU在位

if(s_vtt_PGood == 1'b1 && s_present_n == 1'b0) begin //第二CPU在位

s_PwrGood <= 1'b1; //set S_PwrGood=1

end

//if(vttm_PGood == 1'b1 && vtt_PGood == 1'b1 && (s_vtt_PGood == 1'b1 || s_present_n == 1'b1)) begin

if(vtt_PGood == 1'b1 && (s_vtt_PGood == 1'b1 || s_present_n == 1'b1)) begin

//上面3个信号全部置起来了再进行下一步

n_state <= 35; //35Step

end

end

35:begin

//If PWRGood=1, VDDCPU_ON+=1

//If S_PwrGood=1, S_VDDCPU_ON+=1

//if(pwrGood == 1'b1) begin

// vddcpu_Op <= 1'b1; //set PVDDCPU_ON+=1

//end

//if(s_PwrGood == 1'b1) begin

// s_vddcpu_Op <= 1'b1; //set S_VDDCPU_ON+=1

//end

//由于 PWRGood为输出信号,上述逻辑改为10ms延时后直接置vddcpu_Op 和 s_vddcpu_Op

if(flag35_10ms == 1'b1) begin

vddcpu_Op <= 1'b1; //set PVDDCPU_ON+=1

if(s_present_n == 1'b0) begin //第二CPU在位

s_vddcpu_Op <= 1'b1; //set S_VDDCPU_ON+=1

end

n_state <= 36; //36Step

end

end

36:begin

n_state <= 37; //37Step 暂无逻辑,直接跳过

end

37:begin

n_state <= 38; //38Step 暂无逻辑,直接跳过

end

38:begin //读取两个输入状态

avr_ready_r0 <= avr_ready; //存 avr_ready状态

s_avr_ready_r0 <= s_avr_ready; //存 s_avr_ready状态

if(flag38_20ms == 1'b1)begin //延时20mS

n_state <= 39; //39Step

end

end

39:begin

//If AVR_ready=1, CPUPWRGood=1

//If S_AVR_ready=1, S_CPUPWRGood=1

if(avr_ready == 1'b1) begin

cpupwrGood <= 1'b1; //set CPUPWRGood=1

end

if(s_avr_ready == 1'b1 && s_present_n == 1'b0) begin //第二CPU在位

s_cpupwrGood <= 1'b1; //set S_CPUPWRGood=1

end

if(avr_ready == 1'b1 && (s_avr_ready == 1'b1 || s_present_n == 1'b1)) begin

//上面2个信号全部置起来了再进行下一步

f_pw_on <= 1'b1; //set f_pw_on=1

n_state <= 40; //40Step

end

end

40:begin

if(f_pw_on == 1'b1 && dsusc == 1'b0) begin

//f_pw_on <= 1'b0; //set f_pw_on=0

n_state <= 41; //41Step

// 进行下电处理

end

end

//-----------------------------------------------------------------------------------------------

//进行下电处理

41:begin //关cpupwrGood

//---------------------------------恢复Butn状态

dPwr_Butn <= 1'b1; //-Pwr_Butn=1

s_dPwr_Butn <= 1'b1; //S_-Pwr_Butn=1

//---------------------------------

if(f_pw_on == 1'b1) begin

s_cpupwrGood <= 1'b0;

cpupwrGood <= 1'b0;

if(flag41_20ms == 1'b1)begin //延时20mS

n_state <= 42; //42Step

end

end

end

42:begin //关vddcpu_Op

if(f_pw_on == 1'b1) begin

s_vddcpu_Op <= 1'b0;

vddcpu_Op <= 1'b0;

if(flag42_20ms == 1'b1)begin //延时20mS

n_state <= 43; //43Step

end

end

end

43:begin //关pwrGood

if(f_pw_on == 1'b1) begin

s_PwrGood <= 1'b0;

pwrGood <= 1'b0;

if(flag43_20ms == 1'b1)begin //延时20mS

n_state <= 44; //44Step

end

end

end

44:begin //关vtt_Op

if(f_pw_on == 1'b1) begin

vtt_Op <= 1'b0;

if(flag44_20ms == 1'b1)begin //延时20mS

n_state <= 45; //45Step

end

end

end

45:begin //关Vsusiomem_Op

if(f_pw_on == 1'b1) begin

s_Vsusiomem_Op <= 1'b0;

Vsusiomem_Op <= 1'b0;

if(flag45_20ms == 1'b1)begin //延时20mS

n_state <= 46; //46Step

end

end

end

46:begin //关vcca18m_Op

if(f_pw_on == 1'b1) begin

s_vcca18m_Op <= 1'b0;

vcca18m_Op <= 1'b0;

if(flag46_20ms == 1'b1)begin //延时20mS

n_state <= 47; //47Step

end

end

end

47:begin //关p2p5vmem_Op

if(f_pw_on == 1'b1) begin

p2p5vmem_Op <= 1'b0;

if(flag47_20ms == 1'b1)begin //延时20mS

n_state <= 48; //48Step

end

end

end

48:begin //关Vdd_Op

if(f_pw_on == 1'b1) begin

s_Vdd_Op <= 1'b0;

Vdd_Op <= 1'b0;

if(flag48_20ms == 1'b1)begin //延时20mS

n_state <= 49; //49Step

end

end

end

49:begin //关atx_Op

if(f_pw_on == 1'b1) begin

atx_Op <= 1'b0;

if(flag49_20ms == 1'b1)begin //延时20mS

front_bp_Pwr_Enabled <= 1'b0; //回到复位状态

ocp_aux_Pwr_Enabled <= 1'b0; //回到复位状态

ocp_main_Pwr_Enabled <= 1'b0; //回到复位状态

f_pw_on <= 1'b0; //清开机状态0

f_pw_off <= 1'b1;//置关机状态1

if(bmc_PwrButn_out_n == 1'b1)begin

f_keychange <= 1'b1;

f_dsuslowtimer <= 1'b1; //置dsuslow计时标志

end

else begin

f_keychange <= 1'b0; //keychange=0清0

end

n_state <= 0; //0Step 回到复位状态

end

end

end

//-----------------------------------------------------------------------------------------------

default: n_state <= n_state;

endcase

end

end

//-----------------------------------------------------------------------------------------------------------

endmodule