FPGA 原理、结构、开发流程简述

简介

本文主要介绍了博主在阅读天野英晴主编的《FPGA 原理和结构》一书时的读书笔记,方便更好的了解和入门 FPGA。本博客图片均来自于参考文献 [1]。

FPGA 特性和粒度

FPGA 是一种可编程的逻辑器件,用来实现任意逻辑电路的集成电路。FPGA 有如下几种要素:

- 逻辑要素:乘积项,查找表,数据选择器等。

- 输入/输出要素:连接 FPGA I/O 引脚和内部布线要素。

- 布线要素:各种块之间的连接部分,形成通路。

- 其他要素:逻辑块,开关块,连接块,I/O 块,他们都由配置存储单元控制,还有一些硬核电路比如乘法器,块存储器 (BRAM) 等。

FPGA 的结构也可以从不同的粒度进行讨论:

- 晶体管:组成电路的基本单元。

- 逻辑门:实现逻辑功能的基本元素。

- 查找表 (LUT):FPGA的基本单元,是真值表的实现,相当于对存入 SRAM 的数据进行多路选择。

输入

输入  输出 (也就是有

输出 (也就是有  种输入组合) 的查找表会使用

种输入组合) 的查找表会使用  位存储单元 (称为配置内存),可以实现

位存储单元 (称为配置内存),可以实现  种逻辑功能。

种逻辑功能。 - 逻辑块 (CLB 或 LAB):是一种比查找表更抽象的层级,包含很多个查找表,触发器 (Filp-Flop),选择弃等,用来方便在 FPGA 后续的布局布线。

FPGA 的可编程特性让 FPGA 可以通过可编程的开关来控制电路结构,这种可编程的开关可以使用多种技术实现:

- (电) 可编程可擦除只读存储器 (也包含闪存):尺寸小,非易失,soft-error 容错性高,但重写时需要高电压,无法使用 CMOS 工艺,重写次数有限制。

- 反熔丝:接通电阻和负载电容小,非易失,但无法重写,为了可编程性每根线都需要晶体管。

- 静态存储器 (SRAM):CMOS 工艺,重写次数无限制,但安全性较低,对 soft-error 敏感。

目前,由于 SRAM 可以使用先进的 CMOS 工艺的优点,SRAM 是 FPGA 的主流类型。

FPGA 结构

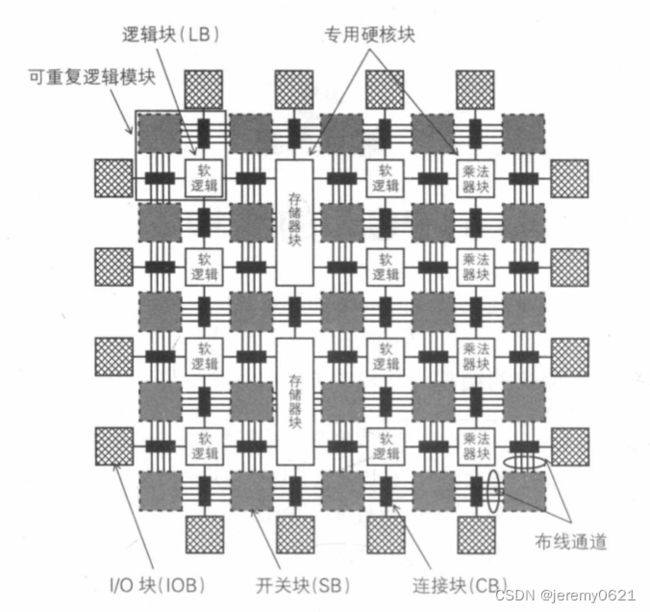

岛形 FPGA 结构如下:

大部分逻辑块都包含查找表,触发器和数据选择器 (既有组合电路也有时序电路的功能),查找表的输入决定了逻辑块的复杂程度,从而有了对电路面积和延迟的权衡。增大查找表的输入会降低逻辑深度,加快电路速度,但有可能产生资源浪费,反之会改善电路的面积效率,但会降低电路的速度。实验证明 5,6 输入的查找表在 FPGA 使用面积和电路延迟上权衡较好,现在的商用 FPGA 都倾向于采用 6-LUT。FPGA 也会有一些专用的的电路连接在 LUT 后,比如加法计算的进位链。

布线时是通过对连接块和开关块的控制来激活或者断开线与线之间的连接,开关快和连接块都是需要配置存储器 (一般是SRAM) 来对其的开关进行控制。

FPGA 还会有一些用于计算的单元,比如 DSP 这种专用的硬核块,但如果过多的专用计算硬核块没有被利用也会导致浪费。因此,高性能,高编程自由度,高使用效率之间存在权衡关系。

早期 FPGA 上的存储资源并不多,随着技术和数据存储需求的增长,FPGA 架构开始集成高效的片上存储器 (外部存储器会有带宽系统瓶颈),现在的 FPGA 片上存储器 (嵌入式存储器) 有: (1) BRAM,(2) LUT (LUT 本质是连接 SRAM 的多路选择器,可以用来实现逻辑功能,也可以用来存储),(3) 存储器 IP 等。

JTAG 是一种用来调试 FPGA 的接口标准,其中应用了边界扫描测试标准,边界扫描是通过外部访问移位寄存器,在输入引脚决定测试值,在输出引脚观测输出值的机制。接口简单,信号需要的少。JTAG 还可以用来写入 FPGA 的配置数据。为了观察 FPGA 的内部信号,还可以把需要观测的信号写入嵌入式存储器,然后通过 JTAG 读到上位机。

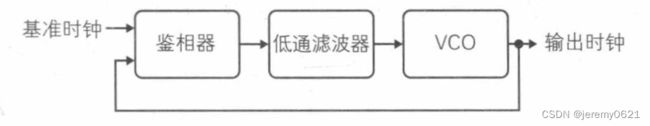

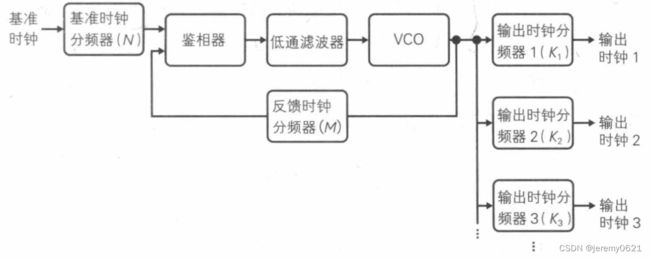

PLL 和 DLL 是用来控制 FPGA 中的时钟的,FPGA 开发时可能需要生成跟外部没有相位差的时钟,或是需要不同频率,不同相位的时钟,其中

- PLL 基于 VCO,根据所加电压调整频率的振荡器,鉴相器用来判断时钟相位的差别,低通滤波器过滤掉高频信号: 其中还可以通过分频器来实现大于或者小于基准时钟的功能: 其中:

,PLL 还有输出锁定功能,用来避免调整过程时钟不稳定的阶段。

,PLL 还有输出锁定功能,用来避免调整过程时钟不稳定的阶段。 - DLL 通过可变延迟线来实现时钟信号的不同延迟,DLL 稳定性好,不容易引起相位误差,但 PLL 时钟合成自由度高,现已 PLL 的 FPGA 架构为主流。

FPGA 开发流程

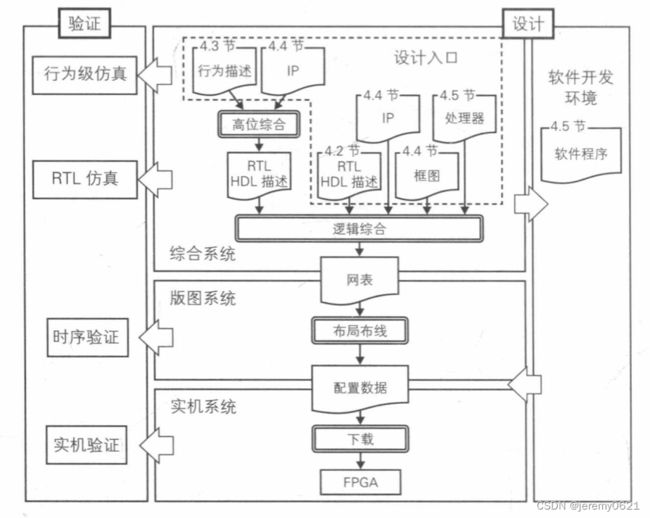

按设计和验证分类的 FPGA 设计流程:

基于 HDL 的设计流程是:

- 逻辑综合:从 HDL (RTL 描述) 到逻辑电路 (门级网表) 的过程。

- 技术映射与逻辑打包:技术映射是指从门级网表映射到查找表级,逻辑打包是把查找表级的网表打包成更高层级的逻辑块 (CLB) 级别,方便后续布局布线。

- 仿真:RTL 仿真,网表仿真,考虑布局布线结果的仿真。

- 布局布线:布局是指对片上逻辑元素的使用进行选择,布线是指对这些逻辑元素进行合理地连接。

- 配置 FPGA (生成比特流):完成布局布线后,FPGA 上的资源配置情况会存储下来。将配置文件写入器件需要编程器,其中可以通过 (1) JTAG 方式 (断电或重置后配置信息会丢失) (2) 编程用非易失存储器 (板载 ROM) (3) SD 卡 或 USB 写入 (通过微处理器向 FPGA 写入配置数据)。

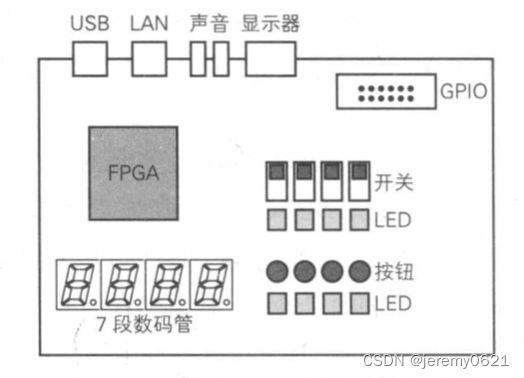

板卡是一种 FPGA 和多种输入输出设备结合的开发板,用户电路也可以主动写观测模块用于调试开发模块的功能:

HLS 的设计是从 C 语言代码生成 RTL 描述的过程 (也被称之为行为综合),其中 HLS 有几种不同的输入输出描述方式:

- 参数和返回值 (或指针) 作为接口。

- 参数 (既有 input 也有 output) 作为接口。

- read 和 write 函数实现接口的并行处理 (无参数)。

行为综合还可以设置生成接口的类型方式:

关于 HLS 设计的更多细节,可以参考博主的 Vivado HLS UG871 学习笔记系列的博客。

基于 IP 的设计可以使用提前用 RTL 描述好的通用的格式 (称为 IP 核) ,与其他模块互相连接即可。

FPGA 上的处理器分为硬核处理器和软核处理器。硬核处理器以硬核的形式集成在 FPGA 中。比如 SoC,这种处理器是标准的嵌入式处理器 (Xilinx ZYNQ 系列中称为 PS);软核处理器使用可编程逻辑实现的具有处理器功能的模块,自由度较高。

软件开发环境 (SDK):基于处理器的系统也需要进行软件开发,SDK 包含开发用的编译器,调试器等,软件开发环境需要知道硬件的一些组成和架构信息,让用户通过操作系统或是直接对内存进行管理。

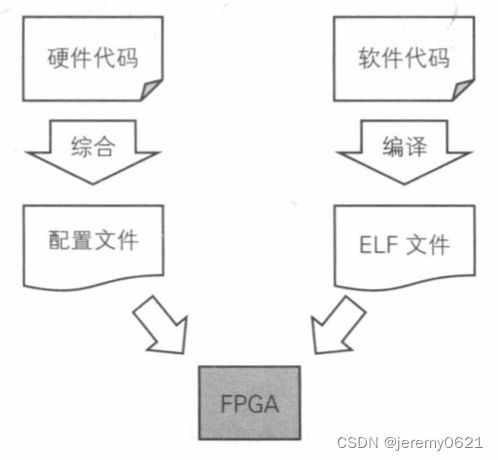

关于软硬件整合之后执行的示意图如下:

其中主要有以下几种方式:

- SDK 上整合和执行,将配置文件和 ELF 文件在 SDK 上整合,上传到 FPGA 的主存储器 (处理器) 上运行,可以用 SDK 观测软件运行的状态。

- SDK 上整合,非易失内存执行,把整合好的文件放在 FPGA 的板载 ROM,SD 卡,USB 等,在 FPGA 上电复位后从这些存储器中加载软件和硬件的数据。

- 硬件开发环境中整合和执行,存放在 FPGA 的 BRAM 中,可以在硬件开发环境中整合,导入 ELF 文件并设置处理器内存地址信息。这也适用于没有处理器的 FPGA 设计。

参考文献

[1] FPGA 原理和结构 / (日) 天野英晴主编;赵谦译,北京人民邮电出版社,2019.3 (2022.9 重印)。