高速DSP系统设计参考指南(一)高速DSP设计面临的挑战

(一)高速DSP设计面临的挑战

- 1. 概述

- 2. 一般挑战

- 3. DSP音频系统的挑战

- 4. 视频系统的挑战

- 5. DSP通信系统面临的挑战

资料参考来自TI官网和网络。

1. 概述

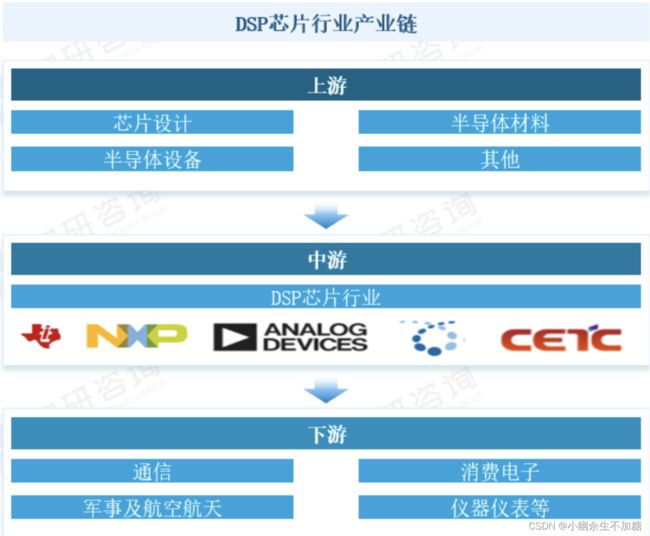

DSP芯片,也称数字信号处理器,是一种具有特殊结构的微处理器。DSP芯片的内部采用程序和数据分开的哈佛结构,具有专门的硬件乘法器,广泛采用流水线操作,提供特殊的DSP指令,可以用来快速地实现各种数字信号处理算法。DSP芯片型号多种多样,分类也有很多种方法。按基础特性分为静态DSR芯片和一致性DSP芯片;按用途分为通用DSP芯片和专用DSP芯片;按DSP芯片处理的数据格式分为定点DSP芯片和浮点DSP芯片。

当今的数字信号处理器(DSP)通常以 1GHz 的内部时钟速率运行,而向外部设备发送信号和从外部设备接收信号的速率高于 200MHz。这些快速开关信号会产生大量噪声和辐射,从而降低系统性能并产生电磁干扰(EMI)问题,使其难以通过联邦通信委员会(FCC)认证所需的测试。良好的高速系统设计需要在动态负载条件下具有低开关噪声的稳定电源、高速信号走线之间的最小串扰、高频和低频去耦技术,以及具有最小传输线效应的良好信号完整性。

2. 一般挑战

随着DSP 性能水平和时钟频率持续快速提高,管理噪声和辐射变得越来越重要。在千兆赫世界中,承载信号的线路就像传输线一样,会产生信号反射,从而导致失真。此外,由于数据被压缩到越来越小的时间周期中,所产生的更短的信号脉冲更容易受到干扰。在处理音频和视频系统时,这种风险尤其大,因为噪声会导致细微的性能下降,而这通常不会对离散数据产生任何影响。

当今DSP 系统不断提升的功率和性能也给实现电磁兼容性(EMC)带来了挑战。在高频下,PCB 上的走线就像单极或环形天线,产生的辐射往往难以满足FCC 类标准和B级要求。为应对高性能设计的散热挑战而可能需要的放热器和通风装置会进一步加剧EMC 问题。集成无线功能的趋势造成了进一步的困难,因为有意将辐射器设计到系统中。

这些趋势使得人们有必要重新思考传统的DSP 设计流程。在传统方法中,工程师关注设计的功能和性能方面。只有在原型测试发现问题时,才会在设计过程的后期阶段考虑噪声和辐射。但如今,噪声问题变得越来越普遍,超过 70%的新设计首次EMC 测试就失败了。因此,从设计过程的一开始就着手解决这些问题变行至关重要。从开发周期的一开始就投入少量时间使用低噪音和低辐射的设计方法,将通过最大限度地减少后期重新设计成本和产品发货日期的延迟来产生高回报。

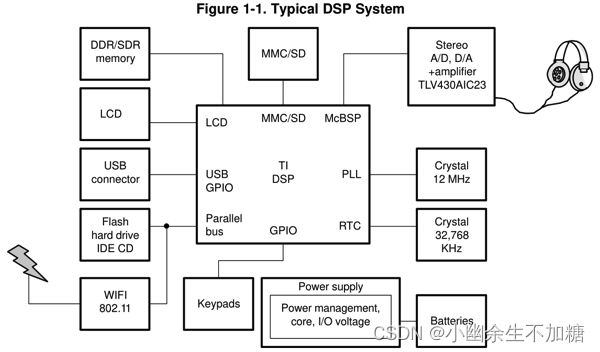

典型的DSP 系统,如图所示 包括许多外部设备,例如音频编解码器、视频、LCD 显示器、无线通信(蓝牙和 IEEE 802.11)、以太网控制器、USB、电源、振荡器、存储器、内存和其他支持电路。这些部件中的每一个都可能是噪声发生器,或者受到相邻部件产生的干扰的影响。因此,为了最大限度地降低器件和系统相关噪声,确保系统设计成功,必须采用良好的高速设计实践。

噪声源和噪声受害者之间的耦合导致电噪声。Figure 1-2 显示了典型的噪声路径。噪声源通常是快速开关信号,噪声受害者是承载信号的元件,其性能受噪声影响。耦合通过相邻信号和电路的寄生电容和互感发生。当信号走线成为有效天线时,就会发生电磁耦合,辐射并对相邻电路产生干扰。

电子系统中产生噪声的机制有很多。时钟电路通常具有最高的切换速率,因此是主要的噪声源。端接不当的信号线可能会产生反射和信号失真。趋肤效应和邻近效应引起的接地层电阳会导致显要的接地噪声。半导体本身也会产生噪声:

**热噪声:**也称为约翰逊噪声,热噪声存在于所有电阻中,由电子的随机热运动引起。音频和视频设计中的热噪声可以通过保持尽可能低的电阻来改善信噪比。

散粒噪声:散粒噪声是由二极管和晶体管中随机穿过栅极的电荷引起的。这种噪声与流经二极管或晶体管的 DC 电流成反比,因此较高的 DC 工作电流会提高信噪比。当DSP 系统在信号路径上包括许多模拟分立器件(例如分立视频和音频放大器)时,散粒噪声可能成为一个重要因素。

闪烁噪声:也称为1/f噪声,闪烁噪声存在于所有有源器件中。它是由陷阱引起的,其中电荷势垒被随机捕获和释放,引起随机的电流波动。闪烁噪声是半导体工艺技术的一个因素,因此 DSP 系统设计不能从源头上降低它,而必须注重减轻它的影响。

突发噪声和雪崩噪声:突发噪声,也称为爆米花噪声,是由离子污染引起的。雪崩噪声存在于以反向击穿模式工作的齐纳二极管等器件中。这两种类型的噪声都与半导体工艺技术有关,而不是系统设计技术。

由于标准对辐射的电磁能量有所规定,DSP 系统设计人员还必须考虑向环境辐射噪声的可能性。辐射的主要来源是走线传播的数字信号、电流回路面积、不充分的电源滤波或去稿、传输线路效应以及缺少回路和接地层。还需要注意的是,在千兆赫速度下,散热器和外壳共振会放大辐射。

DSP 系统中的噪声无法消除,但可以将其降至最低,以确保它不会干扰系统中的其它电路。降低噪声的三种方法是从源头抑制噪声,使相邻电路对噪声不敏感,以及消除褐合通道。可以应用高速设计实践来最大限度地降低器件和系统相关噪声,并提高系统设计成功的可能性。本文档将通过提供从设计过程的最开始到故障排除的指南米解决所有这三个方面的问题,从而将噪声和辐射降低到可接受的水平。本文所示的噪声敏感技口示例主要针对音频、视频和电源,因为这些系统的性能会受到周围DSP 电路以及这些电路与DSP 接口方式的极大影响。

3. DSP音频系统的挑战

音频系统是高速 DSP 设计面临的最大挑战之一,因为相对较小的噪声水平往往会对最终产品的性能产生显著影响。

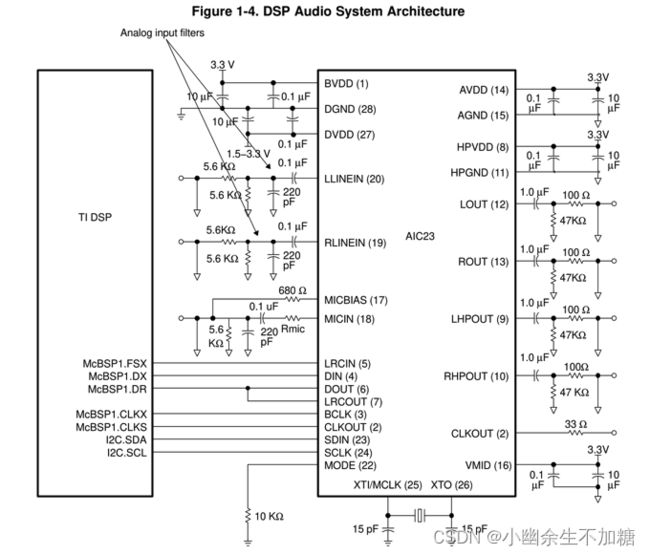

在音频采集和回放中,音频性能取决于所用音频编解码器的质量、电源噪声、音频电路板布局以及相邻电路之间的串扰量。此外,采样时钟的稳定性必须非常好,以防止回放和采集期间出现不必要的声音,如爆裂声和咔哒声。Figure 1-3 显示了DSP 音频设计的典型信号链。大多数Texas InstrumentsIncorporated DSP 都包括一个多通道缓冲串行端口(cBSP ),用于与外部音频编解码器接口。

尽管这是德州仪器公司的专用接口,但它可配置为与行业标准 I2S 音频编解码器一起工作,如所示Figure 1-4中显示的所有模块Figure 1-3 从ADC 到Amp级对噪声非常敏感,因此耦合到任何模块的任何干扰都会传播并产生不需要的可听声音。

常见的音频设计问题包括:

耦合到麦克风输入的噪声;

音频输入、线路输入和麦克风输入没有抗混叠滤波器;

增益级和幅度失配导致的过度失真;

音频时钟、位时钟和主时钟抖动过大;

缺乏良好的去耦和噪声隔离技术;

不使用具有高电源抑制的线性调节器来隔离音频编解码器中的噪声;

用于 ADC 和DAC转换器的基准电压没有良好的去耦电容;

耦合到音频电路的开关电源噪声;

高阻抗音频走线靠近高噪声开关电路,并且在印刷电路板(PCB)布局中没有提供最短的电流返回路径,以最大限度地减少 DSP 和编解码器之间的电流返回环路。

总之,要获得良好的音频性能,需要正确设计编解码器的输入级、DSP 接口和输出放大器。DSP 音频架构示例如所示Figure 1-4其中I2S 接口是驱动位时钟(McBSP1)的主机。CLK)和顿同步信号。

4. 视频系统的挑战

视频处理是另一种重要的DSP 应用,对噪声和辐射高度敏感。视频系统设计的主要挑战之一是如何消除视须伪像,如色彩失真、60Hz 啥喷声、音频拍等。这些问题通常与不适当的视频板设计有关。例如,电源鸣声可能会传播到视频DAC 输出,音频回放可能会导致电源瞬变,音频部分可能会耦合到视频部分的高阻抗走线。以下是一些常见的视频噪音问题:

信号完整性、HSYNC、VSYNC和像素时钟上的过度过冲和欠冲由不正确的信号端接引起。

过度的编码器、解码器和像素时钟抖动会导致检测颜色信息的问题。例如,彩色屏幕只显示黑白图像。

缺少视频终端电阻会导致视频图像失真。视频解码器的输入端和视频编码器的输出端应使用一个 75欧姆的终端电阻。

音频播放可能会导致视频屏幕闪烁。这可以通过增加视频和音频电路的隔离来纠正。最佳方法是使用高电源抑制比(PSRR)线性调节器来隔离音频编解码器和视频编码器/解码器电源。此外,手动布线关键走线远离任何开关信号,以减少串扰和干扰。

没有高速信号返回路径的隔离模拟地。重要的是要记住,对于 10 MHz 以下的低速信号,电流以最低电阻返回,通常是最短的路径。另一方面,高速电流返回电感最小的路径,通常位于信号下方。

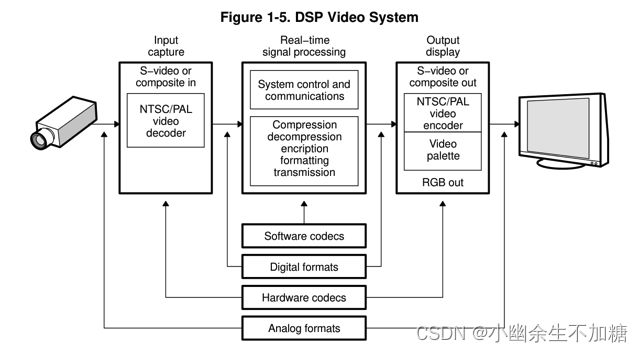

Figure 1-5 显示了一个典型的DSP 视频系统,其中模拟视频信号被捕获、处理,然后显示。该视频信号路径的质量决定了显示器的视频性能,尤其是在输入视频解码器级和输出视频编码器级。由于系统设计和布局非常关键,因此有必要应用本文讨论的高速设计规则来降低开关噪声、串扰和电源瞬变的负面影响,从而减少或消除视频伪像。正如在任何电子系统中一样,不可能完全消除噪声,但应用良好的设计技术有助于降低对性能产生负面影响的风险。

5. DSP通信系统面临的挑战

与视频和音频系统一样,通信是另一种对噪声和辐射商度敏感的重要DSP应用。这里的众多挑战之一是创建具有多个功能强大、高度集成的DSP 的系统,以提供高性能、极低的误码率和干扰。在这些系统中,干扰不仅会产生 EII 问题,还会干扰共他通信信道,并导致错误的信道检测。这些问题可以通过应用适当的电路板设计技术、屏蔽、F 和混合模拟/数字信号隔离来最小化。在某些情况下,可能需要一个扩频时钟发生器来进一步降低干扰并改善信噪比。虽然扩频时钟可以降低峰值辐射,但该时钟的谐波会在更宽的带宽上扩散,这会导致通道间干扰,因此工程师在使用这种时钟发生器电路时必须小心。

通信系统的一个例子如所示Figure 1-6 其中蓝牙和IEEE802.11 都在同一主板上实现,并且驻留在相同的2.4GHz RF 频谱上。这里最困难的任务是如何防止两个系统相互干扰,这已成为业界研究的热点之一。