----------------------------------------------------------------------------------------------------------------------------

开发板 :NanoPC-T4开发板eMMC :16GBLPDDR3 :4GB

显示屏 :15.6英寸HDMI接口显示屏u-boot :2023.04linux :6.3

----------------------------------------------------------------------------------------------------------------------------

一、USB基础知识回顾

在linux驱动移植-usb驱动基础我们对USB总线进行了简单的介绍,其中包括:

USB协议版本介绍:USB1.0、USB1.1、USB2.0、USB3.0、USB3.1、USB3.2、USB4.0;USB接口:伴随着USB版本迭代,USB产生了多种连接器类型规范,比如Type-A、Type-B、Mini-A、Mini-B、Micro-A、Micro-B、Type-C等。

1.1 USB协议版本

从USB协议诞生至今,出现了多个USB协议版本,如USB1.0、USB1.1、USB2.0、USB3.0、USB3.1、USB3.2。最新的是USB4.0协议,可直连CPU的PCIe总线,最大速度可达40Gbps,使用Type-C接口,兼容DP视频协议、PD快充协议等,最高支持100W供电。

| USB协议版本 | 速率称号 | 最大速率 | 电源 | 类型 | 推出时间 |

|---|---|---|---|---|---|

| USB1.0 | 低速(Low-Speed) | 1.5Mbps | 5V/500mA | 半双工 | 1996年1月 |

| USB1.1 | 全速(Full-Speed) | 12Mbps | 5V/500mA | 半双工 | 1998年9月 |

| USB2.0 | 高速(High-Speed) | 480Mbps | 5V/500mA | 半双工 | 2000年4月 |

| USB3.0(USB3.2 Gen1) | 超高速(SuperSpeed USB) | 5Gbps | 5V/900mA | 全双工(两对数据线和一根屏蔽地线,以及2.0的四根线) | 2008年月11月 |

| USB3.1(USB3.2 Gen2) | SuperSpeed USB 10Gbps | 10Gbps | 20V/5A | 全双工(两对数据线和一根屏蔽地线) | 2013年月7月 |

| USB3.2(USB3.2 Gen2×2) | SuperSpeed USB 20Gps | 20Gbps | 20V/5A | dual-lane(2线,每条lane都是一对差分线) | 2017年月9月 |

| USB4.0(Gen3×2) | ---- | 40Gbps | 100瓦 | single-lane或dual-lane,兼容Thunderbolt3 | 2019年月8月 |

为了支持更高的传输速度,正常而言,越高版本的USB协议,定义的传输信号线会越多。

USB3.0包括USB2.0的引脚,USB3.1和3.0引脚相同;

-

USB2.0:一共有4根引脚,一对差分线D+/D-,还有地线GND、电源线VBUS; -

USB3.0:一共有9根引脚,为了兼容USB2.0除了拥有USB2.0的一对差分线D+/D-、以及地线GND、电源线VBUS外,还会拥有两对差分线(SSTX+和SSTX-及SSRX+和SSRX-)和一根屏蔽地线;

USB3.0和USB2.0使用不同的差分线传输数据,两者互不干扰,可同时工作。USB3.0线缆中保留了USB2.0的数据传输通道,实现了对USB2.0的兼容,另外加了5根线来进行全双工的高速传输。

USB是主从模式的总线,主机称为Host,丛机称为Device(设备)。从机与从机之间、主机与主机之间(不包括USB4.0),不能互联。每次通信都是由主机发起,从机不能主动发起通信,只能被动的应答主机的请求。

为了增加灵活性,又出现了USB OTG(On The Go),USB OTG支持主从切换,同一个设备,在不同场合下,可以在主机和从机之间切换。

USB2.0 OTG线中增加了一根USB ID线,当USB ID线上拉时,处于从机模式,当USB ID线接地时,处于主机模式。更多相关内容参考:《Rockchip RK3399 - USB OTG和extcon驱动 》。

1.2 USB框图

这里我们需要补充一些USB相关的硬件知识,因为RK3399驱动编写中会涉及到。

USB芯片内部实现的功能就是接受软件的控制,进而从内存搬运数据并按照USB协议进行数据打包,并串转换后输出到芯片外部。或者从芯片外部接收差分数据信号,串并转换后进行数据打包并写到内存中。

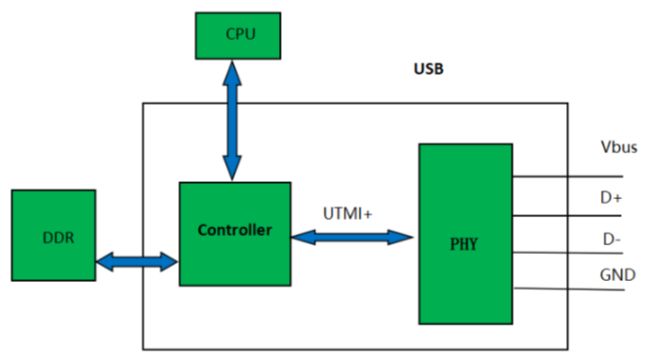

USB芯片一般分为Controller和PHY,以Controller和 PHY 都被封装到SoC为例,如图:

图中绘制的是USB 2.0芯片,其中:

VBUS:电压线,主机利用VBUS给USB设备提供工作电压;D+: 正向传送数据 数据线;D-: 反向传送数据 数据线;GND:地线;

一般来说如果芯片的USB PHY封装在芯片内,基本采用UTMI+的接口。不封装到芯片内的一般采用ULPI接口,这样可以降低pin的数量。

1.2.1 Controller

控制器部分(Controller):主要实现USB协议和控制,内部逻辑主要由MAC层、CSR层、FIFO层,还有其他低功耗管理之类层次;

MAC实现按USB协议进行数据包打包和解包,并把数据按照UTMI/ULPI总线格式发送给PHY;CSR层进行寄存器控制,软件对USB芯片的控制就是通过CSR寄存器,这部分和CPU进行交互访问,主要作为Slave通过AXI或者AHB进行交互;FIFO控制层主要是和DDR进行数据交互,控制USB从DDR搬运数据的通道,主要作为Master通过AXI/AHB进行交互;

按照设备端关联的USB控制器是工作在主模式还是从模式,将:

- 工作在主模式的

USB控制器,称为USB主机控制器 (UHC:USB Host Controller); - 工作在从模式的

USB控制器,称为USB设备控制器 (UDC:USB Device Controller); - 支持主从模式切换的

USB控制器称为USB OTG控制器,同一个设备,在不同场合下,可以在主机和从机之间切换;正常模式下每个OTG控制器都可以工作在主机或从机模式下。

USB主机控制器类型:

OHCI:支持USB 1.1;UHCI:支持USB1.0/1.1,与OHCI不兼容;EHCI:支持USB2.0;xHCI:支持USB3.0;

1.2.2 PHY

USB PHY负责最底层的信号转换,作用类似于网口的PHY。主要实现并转串的功能,把控制器通过 UTMI或ULPI总线传递过来的并行数据转换为串行数据,再通过差分数据线输出到USB接口。

二、RK3399 USB介绍

2.1 USB控制器

RK3399支持4个独立的USB控制器,不同控制器相互独立:

- 两个

USB2.0 HOST(EHCI&OHCI); - 两个

USB3.0/2.0 OTG(DWC3/xHCI);在官方开发手册中这个有时候也被叫做Type C USB3.0,官方为什么这么称呼呢?我个人认为是因为这个控制器连接的USB3.0 Type-C PHY,可以用来实现USB3.0 Type-C接口;

其中:

EHCI/OHCI: 表示该USB控制器集成了EHCI控制器和OHCI控制器;DWC3/xHCI:表示该USB控制器集成了DWC3控制器和xHCI控制器;

2.1.1 USB2.0 HOST

支持高速 (480Mbps),全速 (12Mbps) 和低速 (1.5Mbps),USB2.0 Host控制器的框图如下图所示;

内部有EHCI和OHCI Host Controller:

OHCI支持USB1.0和USB1.1;EHCI支持USB2.0;

Port Routing Control: 用于选择用EHCI还是OHCI。

USB2.0Host控制器连接到USB2.0 PHY。

EHCI和OHCI Rockchip采用linux内核Generic驱动,一般开发时只需要对设备树作相应配置,即可正常工作。

为了同时支持USB1.0、USB1.1和USB2.0,就需要同时用到EHCI和OHCI,因此需要在设备树中把这两个USB控制器都打开,如:

&usb_host0_ehci {

status = "okay";

};

&usb_host0_ohci {

status = "okay";

}

&usb_host1_ehci {

status = "okay";

};

&usb_host1_ohci {

status = "okay";

};这样配置之后,RK3399的两个USB2.0 HOST控制器就使能了,并且同时支持EHCI和OHCI。

2.1.2 USB2.0 OTG

RK3399没有独立的USB2.0 OTG控制器,但有独立的USB3.0 OTG控制器,并且可以向下兼容USB2.0 OTG的完整功能。

USB2.0 OTG 控制器具有以下特性:

- 支持

Host模式和Device模式; - 支持

OTG ID检测,并通过ID电平自动切换Host模式和Device模式; - 不支持

ADP/SRP/HNP协议; Host模式支持高速、全速和低速,Device模式只支持高速和全速模式;Host模式支持9个通道;Device模式支持9个端点(不包括端点0),其中,4个IN端点,3个OUT端点,2 个IN/OUT双

向端点;- 支持

1024x35 bits内部FIFO; - 支持内部

DMA,并且支持scatter/gather功能; - 支持动态配置每个端点的

FIFO大小; Device模式支持BCD(Battery Charging Detect);- 支持

UART Bypass模式;

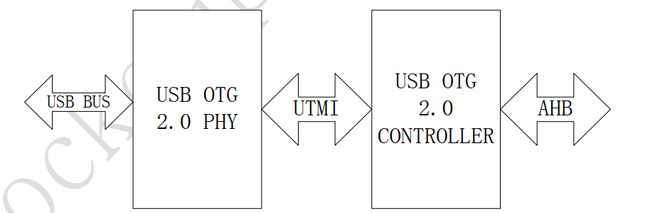

USB2.0 OTG 控制器的框图如下图所示;

2.1.3 USB3.0 OTG

RK3399 USB3.0 OTG使用Synopsys方案,即xHCI扩展的DWC3控制器,Host功能在xHCI框架下实现,而Device功能由DWC3扩展部分实现。

DWC3具有以下特性:

- 支持

Control/Bulk(including stream)/Interrupt/Isochronous传输方式; USB3.0支持同时执行IN和OUT传输,带宽达到8Gbps;- 支持描述符缓存 (

Descriptor Caching) 和数据预取 (Data Pre-fetching); Device模式支持的IN端点数量和OUT端点数量请参考芯片手册;- 支持硬件自动处理

ERDY和burst; - 支持端点批量流传输 (

bulk stream); - 支持

USB3.0 DRD(Dual-Role Device) 特性; - 支持根据

OTG ID状态切换Device和Host模式; - 对于支持

Type-C的芯片,支持UFP/DFP角色交换; - 不支持

SRP(session request protocol),HNP(hostnegotiation protocol)和RSP(Role Swap Protocol);

USB3.0 xHCI Host特性:

- 最多可以连接

64个外设; - 支持一个中断器;

- 支持一个

USB2.0端口和一个USB 3.0端口; - 支持

USB 3.0/USB 2.0并发传输,带宽达到8Gbps; - 支持标准和开源的

xHCI驱动; - 部分芯片支持

xHCI Debug Capability;

USB3.0 OTG 控制器的框图如下图所示;

USB3.0 OTG具有USB3.0 OTG(USB Peripheral和USB Host)功能,且向下兼容USB2.0 OTG功能,大传输速率为5Gbps。

由于USB3.0 HOST控制器为xHCI,集成于DWC3 OTG IP中,所以不用单独为其配置设备树,只需要配置DWC3,并且设置DWC3的dr_mode属性为dr_mode = otg或者dr_mode = host,即可以使能xHCI控制器。

2.2 USB PHY

RK3399支持4个独立的USB PHY:

- 2个

USB2.0 PHY:在设备树中分别叫做u2phy0和u2phy1; - 2个

USB3.0 Type-C PHY:在设备树中分别叫做tcphy0和tcphy0;

2.2.1 USB2.0 PHY

USB2.0 PHY支持1个port和2个port两种设计,如下图是支持2个port的框图;

Host Port:通过UTMI+ 连接到USB2.0 Host控制器;

OTG Port:通过UTMI+连接USB3.0/2.0 OTG控制器的USB2.0逻辑模块;

以RK3399为例,每个USB 2.0 PHY都有两个port端口;

u2phy0:包含u2phy0_host和u2phy0_otg;u2phy1:包含u2phy1_host和u2phy1_otg;

2.2.2 USB3.0 Type-C PHY

USB3.0 Type-C PHY具有以下特性

- 支持

USB 3.0(Super-Speed only); - 支持

DisplayPort 1.3(RBR,HBR and HBR2 data rates only); - 支持

DisplayPort AUX通道; - 支持

USB Type-C and DisplayPort Alt Mode; - 支持

DisplayPort Alt Mode on TypeC A, B, C, D, E and F管脚分配; - 支持正面和反面两个方向;

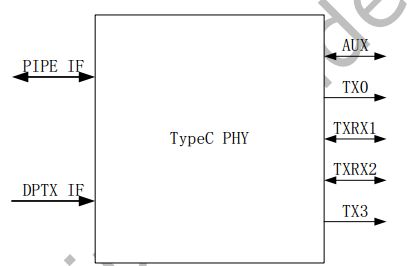

USB3.0 Type-C PHY框图如下图所示:

USB3.0 Type-C PHY由USB3.0 SuperSpeed PHY和DisplayPort Transmit PHY组成。其中:

PIPE_IF接上面提到的USB3.0 OTG;DPTX_IF接DP;

以RK3399为例;

tcphy0:包含tcphy0_dp和tcphy0_usb3;tcphy1:包含u2phy1_host和u2phy1_otg;

USB3.0 Type-C PHY可以根据实际的应用需求,将物理接口简化设计为USB3.0/2.0 Type-A,USB 3.0/2.0 Micro-B 、USB 3.0/2.0 Type-C等多种接口类型,内核USB驱动已经兼容这几种不同类型的USB接口,只需要根据实际的硬件设计修改对应的板级设备树配置,就可以使能相应的USB接口。

2.3 USB控制器和PHY关系

RK3399 USB控制器和USB PHY的连接示意图如下:

上图中DP是Display Port控制器,DP与USB3.0./2.0 OTG共用USB3.0 Type-C PHY。一个完整的Type-C功能,是由USB3.0 SuperSpeed PHY和USB2.0 OTG PHY两部分组成的,这两部分PHY在芯片内部的硬件模块是独立的,供电也是独立的。

三、硬件原理图

这里我使用的开发板型号是NanoPC-T4,开发板如下图所示;

USB资源如下:

- 2个独立的原生

USB2.0 Host Type-A接口;对应开发板上的USBH2、USBH3; - 1个原生

USB3.0 Host Type-A接口;对应开发板上的CON5; - 1个

USB3.0 Type-C, 支持USB3.0 Type-C和DisplayPort 1.2 Alt Mode on USB Type-C;对应开发板上的TYPE-C/DP;

3.1 USB2.0 Host Type-A

Nanpi-T4 开发板USB2.0 PHY芯片引脚如下图所示:

3.1.1 电源接线

上图中供电依次为VCCA0V9_S3、VCCA1V8_S3、VCC3V3_S3;

(1) 电源VCCA0V9_S3由RT9041B-10GE提供的,这是一款稳压器IC,其输入端为VCC3V3_S5;

RT9041B-10GE由VCC1V8_S3使能,VCC1V8_S3作为使能引脚EN的输入端;

VCC1V8_S3是由PMIC_SLEEP_H(连接RK3399的GPIO1_A5/AP_PWROFF,这个应该是处理的睡眠引脚,处理器睡眠时,输出高电平)引脚控制的;

PMIC_SLEEP_H为低电平,Q35 N MOS管导通、VCC1V8_S3输出为1.8V;PMIC_SLEEP_H为高电平,Q35 MOS管截止、VCC1V8_S3输出为0V;

输入端VCC3V3_S5是由VCC12V0_SYS经过NB680GD降压开关模块转换器输出得到固定3.3V电压,有关电路这里就不截图了。

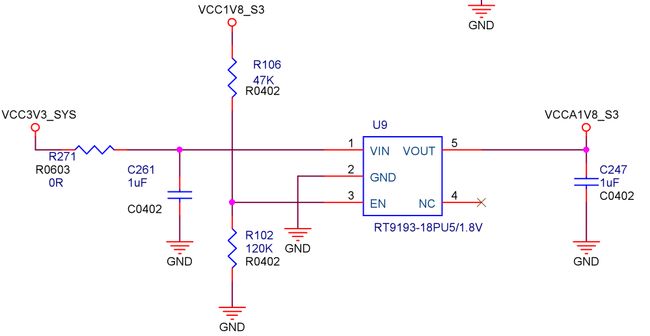

(2) 电源VCCA1V8_S3由RT9193-18PU5/1.8V提供的,这是一款稳压器IC,其输入端为VCC3V3_SYS;

RT9193-18PU5/1.8V同样由VCC1V8_S3使能。

输入端VCC3V3_SYS同样是由VCC12V0_SYS经过NB680GD降压开关模块转换器输出得到固定3.3V电压。

(3) 电源VCC3V3_S3由RK808提供的,连接RK808电源管理芯片第7号输出引脚VSWOUT1;

3.1.2 Type-A接口接线

HOST0_DM、HOST0_DP连接到USBH2,USBH2为USB2.0 Host Type-A接口;

| RK3399 | USB2.0 PHY0 | USB2.0 Host Type A | |

|---|---|---|---|

| HOST0_DP | HOST0_DP | D+ | |

| HOST0_DM | HOST0_DM | D- |

HOST1_DM、HOST1_DP连接到USBH3,USBH3为USB2.0 Host Type-A接口;

| RK3399 | USB PHY1 | USB2.0 Host Type A | |

|---|---|---|---|

| HOST1_DP | HOST1_DP | D+ | |

| HOST1_DM | HOST1_DM | D- |

如下图所示;

电源VCC5V0_HOST0由RT9724GQW提供的,RT9724GQW是一款USB电源供应IC,集成了过电流保护电路、短路折返电路、热关断电路和欠压锁定电路,其输入端为VCC5V0_SYS。

RT9724GQW由VCC5V0_SYS使能,VCC5V0_SYS作为使能引脚EN的输入端,因此RT9724GQW默认就是使能的。

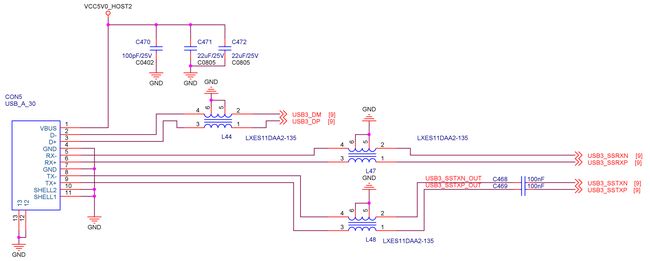

3.2 USB3.0 Host Type-A

我们使用的开发板Nanpi-T4,其中一个USB3.0 Type-C PHY物理接口被设计为USB3.0 Host Type-A,如下图所示:

3.2.1 Type-A接口接线

其中USB3_DM、USB3_DP、USB3_SSRXN、USB3_SSRXP、USB3_SSTXN、USB3_SSTXP连接到CON5,CON5为USB3.0 Host Type-A接口;

| RK3399 | USB3.0 Type-C PHY1 | USB2.0 PHY1 | USB3.0 Host Type A | |

|---|---|---|---|---|

| TYPEC1_TX1P | USB3_SSTXP | TX+ | ||

| TYPEC1_TX1M | USB3_SSTXN | TX- | ||

| TYPEC1_RX1P | USB3_SSRXP | RX+ | ||

| TYPEC1_RX1M | USB3_SSRXN | RX- | ||

| TYPEC1_DM | USB3_DM | D- | ||

| TYPEC1_DP | USB3_DP | D+ |

如下图所示:

电源VCC5V0_HOST2由RT9724GQW提供的,RT9724GQW是一款USB电源供应IC,集成了过电流保护电路、短路折返电路、热关断电路和欠压锁定电路,其输入端为VCC5V0_SYS。

RT9724GQW由VCC5V0_SYS使能,VCC5V0_SYS作为使能引脚EN的输入端,因此RT9724GQW默认就是使能的。

输入端VCC5V0_SYS是由VCC12V0_SYS经过NB679GD降压开关模块转换器输出得到固定5.0V电压。

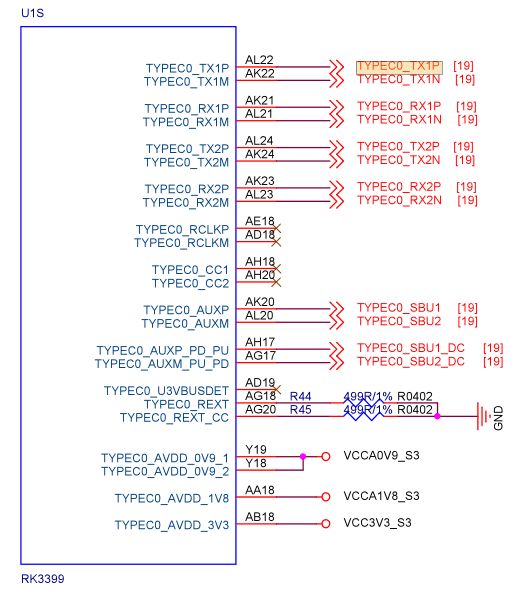

3.3 USB3.0 Type-C

我们使用的开发板Nanpi-T4,另一个USB3.0 Type-C PHY物理接口被设计为USB3.0 Type-C,如下图所示:

3.3.1 Type-C接口接线

其中TYPEC0_TX1P、TYPEC0_TX1N、TYPEC0_RX1P、TYPEC0_RX1N、TYPEC0_TX2P、TYPEC0_TX2N、TYPEC0_RX2P、TYPEC0_RX2N、TYPEC0_SBU1、TYPEC0_SBU2、TYPEC0_SBU1_DC、TYPEC0_SBU2_DC连接到TYPE-C,TYPE-C为USB3.0Type-C接口;

| RK3399 | USB3.0 Type-C PHY0 | USB2.0 PHY0 | USB3.0 Type-C | |

|---|---|---|---|---|

| TYPEC0_TX1P | TYPEC0_TX1P | SSTX1_P | ||

| TYPEC0_TX1M | TYPEC0_TX1N | SSTX1_N | ||

| TYPEC0_RX1P | TYPEC0_RX1P | SSRX1_P | ||

| TYPEC0_RX1M | TYPEC0_RX1N | SSRX1_N | ||

| TYPEC0_TX2P | TYPEC0_TX2P | SSTX2_P | ||

| TYPEC0_TX2M | TYPEC0_TX2N | SSTX2_N | ||

| TYPEC0_RX2P | TYPEC0_RX2P | SSRX2_P | ||

| TYPEC0_RX2M | TYPEC0_RX2N | SSRX2_N | ||

| TYPEC0_AUXP | TYPEC0_SBU1 | SBU1 | ||

| TYPEC0_AUXM | TYPEC0_SBU2 | SBU2 | ||

| TYPEC0_AUXP_PD_PU | TYPEC0_SBU1_DC | SBU1 | ||

| TYPEC0_AUXM_PU_PD | TYPEC0_SBU2_DC | SBU2 | ||

| TYPEC0_DP | TYPEC0_DP | DP1 | ||

| TYPEC0_DM | TYPEC0_DM | DM1 | ||

| TYPEC0_DP | TYPEC0_DP | DP2 | ||

| TYPEC0_DM | TYPEC0_DM | DM2 | ||

| TYPEC_CC1 | ||||

| TYPEC_CC2 |

如下图所示:

电源VBUS_TYPEC由RT9724GQW提供的,其输入端为VCC5V0_SYS。由GPIO4_D2引脚使能;

3.3.2 fusb302

fusb302是可编程的USB Type-C控制器,支持识别各种USB设备和对应的工作状态,且支持最高100W的PD协议。

其具有一下主要特征:

- 具备自主

DRP切换的双重角色功能; - 根据已连接的设备选择作为

Host(主机)或Device(设备)进行连接; - 通过软件配置为

Host(主机)、Device(设备)或双重角色; - 支持

USB功率传递(PD)2.0:

其引脚如下:

| 引脚 | 类型 | 功能 |

|---|---|---|

| CC1/CC2 | I/O | Type-C连接器的配置通道(CC)引脚。最初用于确定插入事件发生以及插入的方向。连接后的功能取决于检测到的操作模式。 作为主机运行时: 1)设置可被连接设备感知的VBUS的允许充电电流 2)用于与使用USB BMC Power Delivery的设备进行通信 3)用于检测已发生的拔出事件 作为设备运行时: 4)指示来自连接的主机的允许下沉电流。用于与使用USB BMC Power Delivery的设备进行通信主要用来 PD协议通信或其他: |

| VBUS | Input | 当作为面向上行端口(设备)运行时,该引脚可用于设备插入和拔出的检测。 |

| VCONN | Power Switch | 要将调节输入电源切换到正确的CC引脚作为VCONN以为USB3.1完整功能电缆和其他配件供电。 |

| INIT | Open-Drain Output | 中断输出,当有事件发生时,用于通知处理器读取I2C寄存器数据。如:插入/拔出typeC,INIT_N都会拉低一下。 |

| SCL | Input | I2C时钟 |

| SDA | Open-Drain I/O | I2C数据引脚 |

INT连接的是RK3399的GPIO1_A2引脚,I2C通信使用的是I2C4。

由于这篇文章不是fusb302的专栏,所以就不细说了,具体参考《PD快充 - fusb302驱动调试笔记》。

参考文章

[1] PD快充 - fusb302驱动调试笔记

[2] RK3399 Android7.1 USB模块中的控制器和PHY

[3] RK3399ANDROID7.1 USB TYPE-A的配置

[4] 超详细USB Type-C引脚信号及PCB布局布线介绍

[5] Rockchip_Developer_Guide_USB_CN.pdf

[6] Rockchip_RK3399_Developer_Guide_USB_DTS_CN.pdf

[7] RK平台如何配置USB功能

[8] 正点原子视频

[9] Linux: USB Gadget驱动简介