FPGA时序约束与分析

目录

1 时序约束概述

1.1 什么是时序约束

1.2 为什么要做时序约束

1.3 时序约束的基本路径

1.4 时序约束的基本流程

1.5 时序约束的主要方法

参考书吴厚航的《FPGA时序约束与分析》

1 时序约束概述

1.1 什么是时序约束

对系统延时(时序)有要求的情况下,不能指望FPGA编译工具自己“猜测”或靠”碰运气“保证系统延时要求得到满足。需要将对系统的所有时序要求通过时序约束的方式告诉FPGA编译工具。这样,FPGA编译工具工作起来就会有的放矢。而且布局布线结束后,也可以通过查看开发工具给出的时序分析报告确认时序要求执行的状况。这正是对FPGA设计进行时序约束和时序分析的意义所在。

1.2 为什么要做时序约束

没有任何设计约束的工程如同“脱缰的野马”般漫无目的且随意任性;但是任何的设计过约束或欠约束都可能导致时序难以收敛(难以达到设计要求)。因此,为了达到特定应用的设计要求,设计者必须设定合理的时序约束。

过约束:约束过于严格,超过实际设计的要求,有限的资源无法合理分配,导致其他功能块收到影响

欠约束:设计过于松散,低于实际设计的要求

1.3 时序约束的基本路径

FPGA时序约束所覆盖的时序路径主要有如下4类

- FPGA内部寄存器之间的时序路径,简称reg2reg

- 输入引脚到FPGA内部寄存器的时序路径,简称pin2reg

- FPGA内部寄存器到输出引脚的时序路径,简称reg2pin

- 输入引脚到输出引脚之间的时序路径(不通过寄存器),简称pin2pin

前三类约束的目标是确保数据信号在时钟锁存沿的建立时间和保持时间内是稳定不变的;

第四类约束目标是直接约束路径的时延值范围。

1.4 时序约束的基本流程

从时序约束本身来说,通常可以分为以下4个主要步骤,即

- 时钟约束:主时钟、虚拟时钟、衍生时钟

- 输入/输出接口约束:系统同步、源同步

- 时钟分组和跨时钟约束:异步

- 时序例外约束:多周期路径、虚假路径

以下按照时序约束的编译先后和优先级高低,自上而下的罗列了推荐的设计约束

##时序约束

#primary clocks(主时钟)

#virtual clocks(虚拟时钟)

#generated clocks(衍生时钟)

#clock groups(时钟组)

#bus skew constraints(总线偏斜约束)

#input and output delay constraints(输入和输出延迟约束)

##时序例外约束

#false paths(假路径)

#max delay/min delay(最大延迟/最小延迟)

#multicycle paths(多周期路径)

#case analysis(案例分析)

#disable timing(禁用时序)

##物理约束

1.5 时序约束的主要方法

- 使用编译软件(Vivado或Quartus)提供的GUI进行时序约束

- 手动编辑XDC文件的方式输入约束脚本

2 基本的时序路径

2.1 时钟偏差

FPGA内部集成的PLL产生的时钟信号:FPGA编译工具在做时序分析时可以直接套用既有的模型给出时钟的偏差参数,作为一部分需要预留的时序余量计算在内。

外部晶振所产生的时钟信号:设计者需要指定相关的时钟偏差参数,以时序约束的方式告诉FPGA编译工具,这些偏差参数的获取方式是查看晶振规格文档

重点关注文档中时钟精度(Frequency Tolerance)、时钟温漂(Frequency versus Temperature Characteristics)和时钟抖动(Jitter)这几个参数。

规格书中15ppm意思是每秒会产生15微秒的偏差

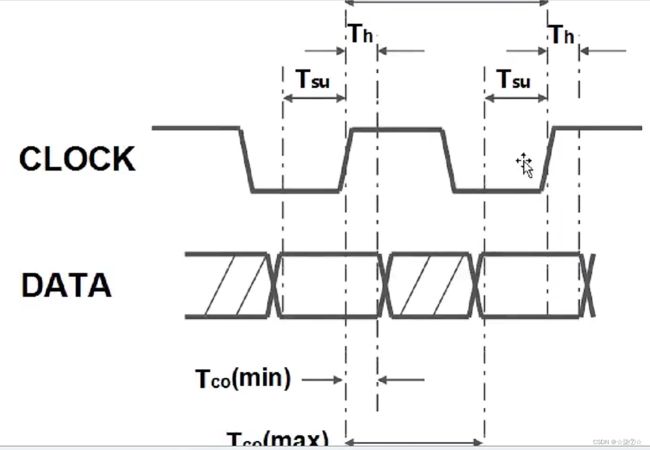

2.2 建立时间与保持时间

建立时间:指时钟上升沿来到之前数据必须保持稳定的时间

保持时间:指时钟上升沿到来以后数据必须保持稳定的时间

导致亚稳态的原因:

- 由于整个路径的延时过长,导致数据在时钟上升沿的建立时间内才到来,即建立时间内数据还未能稳定下来,则数据就无法在时钟上升沿被锁存,处于不确定状态。

- 由于数据传输的太快,原本应该在下一个时钟沿到达的数据,竟然在当前时钟沿的保持时间还没过去就来到了,则数据也无法在时钟上升沿被锁存,处于不确定状态。

故一个数据要想在时钟上升沿被锁存,那么这个数据就必须在这个时钟上升沿的建立时间和保持时间内保持稳定,即数据不能发生任何变化。

注:书中20页的例子有助于理解

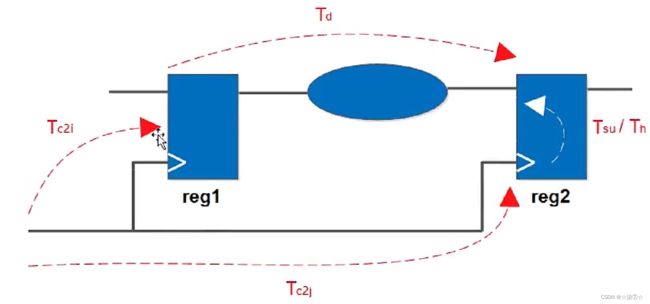

2.3 寄存器到寄存器的时序路径分析

对于reg2reg路径,只要告诉FPGA编译工具他们的时钟频率,时序设计工具便会将时钟周期,建立时间,保持时间等相关参数带入特定的公式,计算这条reg2reg路径允许的延时范围

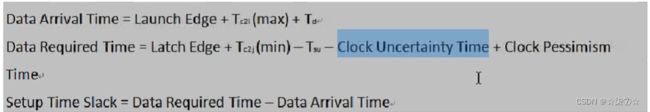

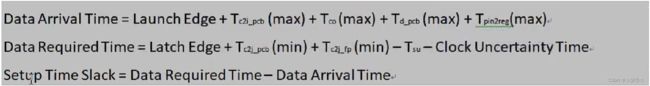

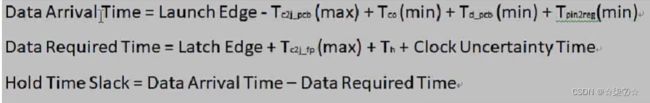

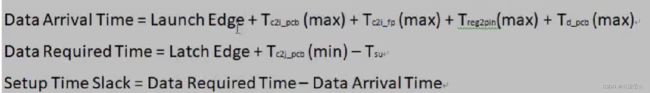

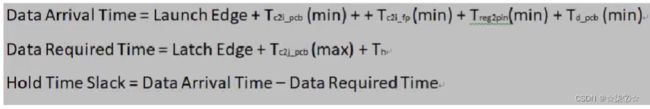

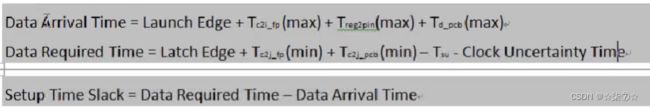

建立时间余量的计算公式如下

保持时间余量的计算公式如下

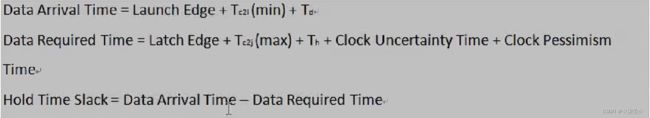

2.4 引脚到寄存器的时序路径分析

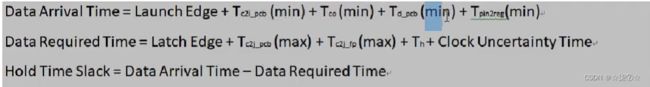

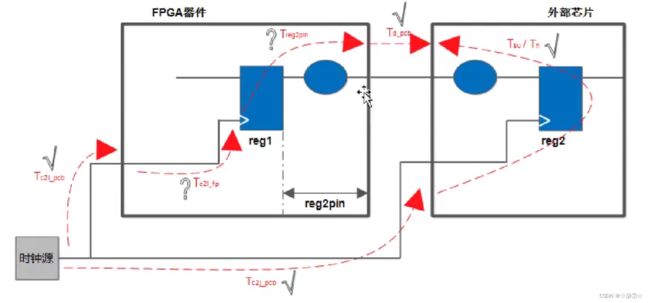

FPGA和外部芯片的通信接口,根据他们时钟来源可以分为系统同步接口和源同步接口。

系统同步接口:FPGA和外部芯片之间的通信时钟都由外部同一时钟源产生;

源同步接口:FPGA和外部芯片之间的通信时钟都由源寄存器的输出端产生;

2.4.1 系统同步接口的路径分析

建立时间余量的计算公式如下

保持时间余量的计算公式如下

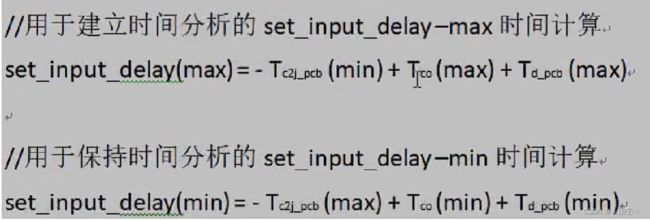

式中只有数据从FPGA器件的引脚到目的寄存器的输入端的延时和时钟信号从FPGA器件的引脚到目的寄存器的输入端的时钟网络延时不确定,其余参数都可以在芯片手册中查到,而时钟信号从FPGA器件的引脚到目的寄存器的输入端的时钟网络延时在编译时硬件会自动给出,是一个较小的定值,所以需要通过set_input_delay命令设置FPGA器件的引脚到目的寄存器的输入端的延时的最大最小值,最大最小值约束公式如下:

2.4.2 源同步接口的路径分析

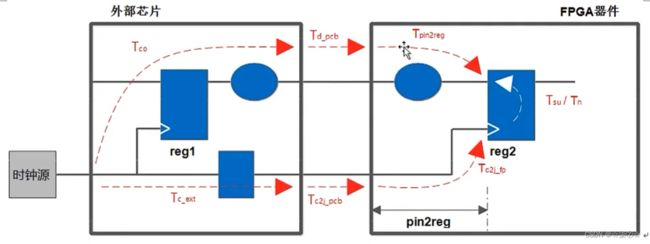

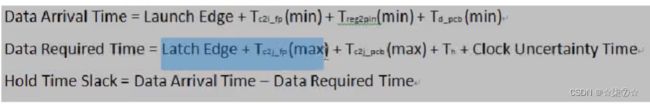

建立时间余量的计算公式如下

保持时间余量的计算公式如下

用于建立和保持时间分析的set_input_delay(max)和set_input_delay(min)公式如下

其中,不论是系统同步接口还是源同步接口,芯片手册中可能未给出

的值,但是可以通过芯片的建立时间和保持时间计算:

=时钟周期-建立时间

=保持时间

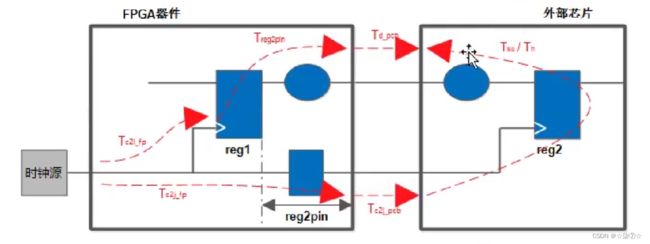

2.5 寄存器到引脚的时序路径分析

2.5.1 系统同步接口的路径分析

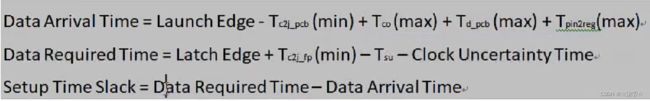

建立时间余量的计算公式如下

保持时间余量的计算公式如下

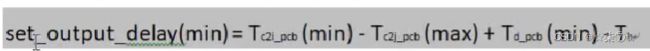

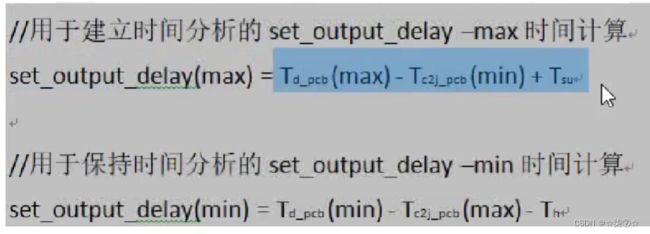

同引脚到寄存器,这里不做分析,需要通过set_output_delay命令设置FPGA器件的目的寄存器到引脚的输入端的延时的最大最小值,最大最小值约束公式如下:

2.5.1 源同步接口的路径分析

建立时间余量的计算公式如下

保持时间余量的计算公式如下

最大最小输出延时计算公式

2.5 引脚到引脚的时序路径分析

通过set_max_delay和set_min_delay这两条约束命令分别指定某个输入引脚到某个输出引脚的最大最小时延值,这个时延值取决于实际应用,没有通用公式。

3 主时钟与虚拟时钟约束

3.1 主时钟约束

主时钟约束的基本语法如下

create_clock -name -period -waveform{} [get_ports]

- clock_name是设计者自定义的主时钟名称,如果不指定,则会默认使用port_name所指定的时钟物理节点

- period是主时钟周期,单位ns

- get_ports表示定义的时钟是FPGA的物理引脚,除此之外FPGA内部网络也能作为主时钟的物理节点,使用get_nets定义。

- waveform的rise_time是上升沿时间,默认0,fall_time是下降沿时间,默认时钟周期一半,单位ns.

在Vivado工具中,可以通过时钟网络报告(Clock Networks Report)和时序确认报告(Check Timing Report)对时钟约束情况进行查看

- 在Tcl console中输入report_clock_networks命令会打开时钟网络报告;

- 在Tcl console中输入check_timing命令会打开时序确认报告;

- 使用GUI对时钟进行约束步骤见书45页的实例3.6

- clocking wzard ip时钟会自动被约束(如MMCM和PLL时钟)

- 如何查看主时钟时序路径报告见书中51页

3.2 跨时钟域约束

对于同步时钟约束的建立时间关系中启动沿和锁存沿相差一个时钟周期;保持时间关系中,启动沿和锁存沿是同一个时钟沿,而在异步时钟约束时,建立时间关系最坏情况,寻找发射沿之后最近的锁存沿,保持时间最坏情况是寻找发射沿之前最近的一个锁存沿。

3.3 虚拟时钟约束

在主时钟约束的基本语法中,get_ports是指定主时钟的实际物理节点,该节点实际存在于FOGA中,而虚拟时钟并不是实际存在于FPGA器件中,他无需依附任何物理节点或者网络。虚拟时钟一啊不能被用于以下情况的输入和输出延时约束:

- 时序分析(一般是I/O引脚相关的时序路径)的参考时钟并不是FPGA内部的设计时钟

- 与FPGA器件的I/O路径相关的内部驱动时钟与其扳级驱动时钟并不是同步的

- 设计者希望对I/O的驱动时钟指定一些特殊的抖动和延时值,但不希望影响此时钟在FPGA内部的时钟传输特性。

虚拟时钟同样用create_clock定义,只是省去了端口项

3.4 时钟特性约束

真实世界中,当时钟在FPGA内部传输时,会经过各种时钟缓冲器,时钟管理单元,以及各种噪声,都会引起时钟沿的变形和延时,时钟的偏差特性通过时钟抖动和时钟不确定性约束定义

时钟抖动

可以通过set_input_jitter命令对单个时钟设置抖动延时,只能约束主时钟,除了MMCM和PLL外,主时钟所设定的抖动延时会传递给他的衍生时钟

如果噪声较大,Vivido会默认使用set_system_jitter命令产生0.05的抖动延时,可以通过该命令设置新的抖动延时值

set_input_jitter基本语法

- set_input_jitter

<延时值> set_system_jitter基本语法

- set_system_jitter <延时值>

时钟不确定性

除了时钟抖动以外的所有可能影响时钟周期性偏差的因素,都可以使set_clock_uncertainty命令进行约束定义 ,基本语法如下:

set_clock_uncertainty -setup -from get_clocks

-to get_clocks <不确定值>

- setup表示定义建立时间不确定性,hold表示定义保持时间,如果不写,则默认定义建立和保持时间

时序分析时的clock uncertainty包括上面的时钟不确定性,其计算公式如下:

clock uncertainty=(sqrt(Tsj^2+Tij^2)+Dj)/2+PE+UU

- Tsj表示最坏情况系统时钟抖动时间,即set_system_jitter的设定值

- Tij表示set_input_jitter设定的输入抖动时间

- Dj是一些硬件原语(MMCM和PLL)等产生的离散时钟抖动

- PE是由MMCM和PLL产生的相位误差,是固定值

- UU是使用set_clock_uncertainty设定的时钟不确定值

可用set_clock_uncertainty命令人为的增加时序余量。

- 使用GUI约束时钟抖动和不确定时间见书68页实例3.12

- 时钟抖动约束分析方法见书70

- 时钟不确定度约束分析方法见书72

3.5 时钟延时约束

对于已经做过主时钟约束的内部时钟,FPGA会自动计算其时序延时值并给出时序报告 ,而FPGA外部的同步时钟信号需要设计者添加时钟延时约束,在引脚到寄存器接口时序约束中,并未专门约束时钟延时,因为在set_input_delay约束值中已经加入了。对于FPGA的时序约束而言,即便使用不同的时序约束方式,也可以达到同样的约束目的,条条大路通罗马。set_clock_latency的命令如下:

set_clock_latency -clock<时钟名称> -rise -fall -min -max -source 延时值

- rise,fall指定时钟延时的边沿

- source定义时钟延时的基本类型,即源延时,默认-network网络延时;源延时指外部引脚输入的时钟信号经过PCB板级延时到达FPGA引脚;网络延时指时钟信号从设计中的某个节点传输到寄存器的输入端口延时。

- min,max指定延时的最大最小值,只能指定其中一个,如不指定则同时作为最大最小值进行定义

查看FPGA内部时钟延时,时钟偏斜见书75页实例3.15

如何用GUI对时钟进行延时约束见书76页实例3.16

4 衍生时钟约束

4.1 衍生时钟定义

- 由已有的主时钟进行分频,倍频,相移而产生出来的时钟信号,如时钟管理单元MMCM等所驱动产生的时钟信号

- Vivado工具能够识别设计中的时钟调整模块CMB及其基于输入主时钟的变更特性,自动为CMB输出的时钟创建约束。

- 通过check timing命令查看未约束的衍生时钟,时序工具未能生成的约束,需要手动添加约束

衍生时钟约束语法如下:

create_generated_clock -name 衍生时钟名字 -source 生成此衍生时钟的源时钟引脚或端口 -multiply_by 衍生时钟相对于源时钟的倍频系数 -divide_by 分频系数 <衍生时钟物理节点>

使用GUI约束衍生时钟见书82页实例4.1