使用接口包装器模块简化在FPGA上实现PCIe的过程

许多最终应用程序都将基于FPGA的设计用作其解决方案的固有组件。他们通常需要PCI Express(PCIe)作为必不可少的功能,以提供与系统中其他组件的标准化接口。

从历史上看,PCI Express一直难以在FPGA中实现,因为它需要具有严格电气要求的千兆位SerDes和模拟电路。

此外,PCI Express的实现需要复杂的数字逻辑,包括物理层,数据链路层和事务层,以及具有高频运行的大型数据路径,因此很难在FPGA中实现。

在FPGA中实现PCI Express的最常用方法包括:

* ASSP / PCI Express桥接芯片

*带数字控制器软IP和内置SerDes / PHY的

FPGA *带数字控制器软IP和外部分立PHY芯片的

FPGA *带内置PCI Express硬IP的FPGA

每个解决方案都有其优点和缺点,本文将探讨不同的方法来帮助确定最佳的应用程序解决方案。

图1 – ASSP / PCIe桥接芯片

ASSP / PCI Express桥接芯片

在此实现中,桥接芯片(ASSP)通常与配套的FPGA / CPLD一起使用(上图1)。该解决方案的优势在于通常能够提供完全的PCI-E电气兼容性。但是,某些缺点可能会对实施造成问题:

*通常为两芯片解决方案,从而增加BOM和制造成本。

*随着时间的流逝,ASSP可能会过时

*通用的且通常是专有的用户界面,可能不易使用或不适合高性能应用程序。

*由于现有的ASSP仅在PCI-E 1.1(Gen1)模式下支持x1和x4链接,因此没有升级到高端PCI-E实施的途径。

*现有的ASSP仅限于端点设计。

*设计人员必须使用ASSP功能集和勘误表,这可能会限制功能。

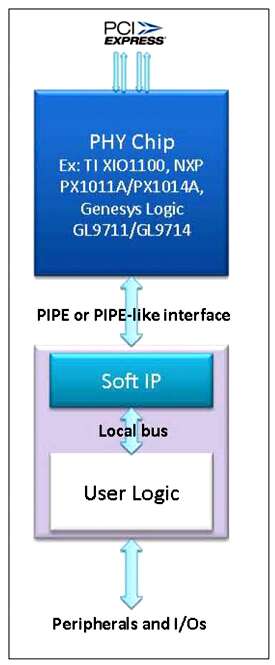

图2 – FPGA软IP和外部PHY

FPGA /数字控制器软IP和外部分立PHY

该解决方案是先前解决方案的衍生产品,但使用了低成本,没有内置收发器。(以上图2)。此方法具有以下优点:

*中量和量大时提供较低的成本。

*完全符合PCI-E电气规范。

*对仅限端点的设计没有限制。

但是,该解决方案确实存在一些缺点,包括:

*前期IP许可证为数量非常少的项目增加了可观的成本。

*软IP消耗了FPGA面积的一部分,从而减少了可供用户使用的逻辑资源。

*与PHY芯片接口(通常通过PIPE并行接口)所消耗的FPGA I / O百分比。PIPE接口可能需要更快速度等级/更高密度的FPGA,以容纳I / O数量和PIPE频率(在某些情况下为250MHz)。

*由于现有PHY芯片仅支持x1和x4中的PCI Express 1.1规范,因此无法升级到x8或PCI Express 2.0(Gen2)。

图3 – FPGA软IP和内置SerDes / PHY

具有数字控制器soft-IP和内置SerDes / PHY的

FPGA此解决方案需要具有内置多千兆位收发器的FPGA(上面的图3)。集成数字PCI Express控制器具有以下优点:

*单芯片解决方案,降低了BOM和制造成本。

*轻松升级到x4,x8和可能的PCI Express 2.0(Gen2),具体取决于FPGA收发器的功能。

*不限于仅端点设计。

但是,该解决方案存在以下问题:

*前期IP许可证为数量非常少的项目增加了可观的成本。FPGA

*软IP消耗了一部分FPGA资源,从而减少了可供用户使用的逻辑资源。

*潜在的PHY限制可能会限制对某些低功耗状态和某些信号机制(如信标生成)的支持。

图4 –带有内置PCI Express IP的FPGA

具有内置PCI Express硬IP的FPGA

一种更好的解决方案是使用硬IP,其SerDes / PHY和数字层(MAC,数据链路,事务处理)在FPGA硅片上进行了加固(上图4)。这具有一些明显的优点:

*提供单芯片解决方案,减少BOM并简化设计和测试。

*确保根据硬IP的功能无缝升级到x4,x8和PCI-E 2.0(Gen2)。

*整个FPGA资源可供用户使用。

但是,对PCI Express使用硬IP也存在一些问题,包括:

*直到最近,它仍需要使用高端FPGA,但是低成本FPGA系列现在支持PCI Express的硬IP。

*设计人员必须使用现有功能集,限制和勘误表,而不能进行定制。

*可用的光纤接口包括数百个信号,通常很难使用。

*由于每个供应商的硬IP和光纤接口的专有性,设计迁移和/或供应商迁移很困难。

使用易于使用的光纤接口

解决问题使用接口包装器提供简单而强大的用户界面,可以解决使用PCI Express硬IP实现FPGA所固有的许多问题。

例如,PLDA的EZDMA模块旨在包裹FPGA的PCI Express硬IP,隐藏硬IP架构接口的复杂性和局限性,并且通常解决硬IP功能问题(下面的图5)。

它是为那些几乎没有PCI Express经验或没有PCI Express经验的人而设计的,也适合有经验的设计师在寻找易于使用但功能强大的PCI Express接口解决方案。EZDMA模块通过显着减少与使用PCI Express硬IP结构接口相关的学习曲线,为设计人员提供了更短的设计周期。

图5. EZDMA接口。

EZDMA还使从PLDA的PCI Express软IP的移植变得容易,使设计人员可以灵活地选择同类最佳的解决方案,而不会花费额外的昂贵设计时间。

此外,PLDA在其PCI和PCI-X架构中整合了EZDMA接口,从而实现了从这些传统接口的无缝过渡和清晰的升级路径。

EZDMA方法不仅允许使用高端FPGA,而且还可以使用领先供应商(例如Altera和Xilinx)的低成本FPGA,从而使硬IP解决方案可用于许多类型的应用。支持的设备包括:

* Altera Stratix IV GX,Arria II GX

* Xilinx Virtex-5 LXT,FXT,TXT,Virtex-6 LXT,SXT,Spartan-6 LXT

EZDMA模块使用大约2K至5K LUT,并使用4KB的存储器,具体取决于特定的配置。PLDA EZDMA接口的其他功能包括:

*熟悉的主(DMA)/目标类型接口,添加了易于使用的高性能多通道DMA

*分散收集(DMA链接),支持多个DMA通道

*具有存储器映射的“从”接口,非常适合寄存器,存储器和I / O访问

*完全可配置用于FPGA资源优化

*支持低功耗模式

*经硬件验证的IP,已在400多种设计中部署

此外,将FPGA设计迁移到ASIC和结构化ASIC时,可以无缝使用EZDMA模块。

选择正确的FPGA – PCI Express解决方案

尽管PCI Express与FPGA接口有多种选择,但在当今的FPGA内部强化完整PCI Express控制器IP的方法正在迅速获得认可,这是一种最小化风险并减少设计时间的首选方法。用途广泛。

由于这些优点,这种方法看起来已成为未来FPGA的主流解决方案,有助于实现功能,灵活性和性能之间的平衡。